DLL发生谐波锁定的原理

描述

01 什么是DLL的谐波锁定问题?

举个简单的例子,假如一个250MHz的DLL,其正常锁定后的整个延时链(VCDL)的总延时为一个周期T,即4ns。但在某些特别情况下,VCDL可能延时2T,即8ns,这就发生了谐波锁定。这时候Loop虽然锁定在一个稳定状态下,然而却是一种错误情况。

在DLL必须提供十分准确的延时间隔(T/N)的应用中,应该极力避免谐波锁定情况,因为相邻时钟间隔可能被定在2T/N,而不是T/N(N为延时单元个数)。

02 发生谐波锁定的原理是什么?

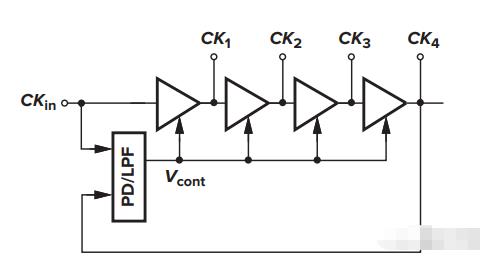

图1 DLL典型结构

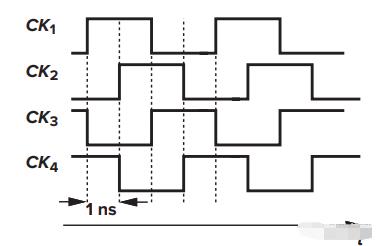

DLL典型结构如上图1所示。图1中有4级延时单元,CKin=250M,一个周期Tin=4ns,锁定后相邻时钟间隔为Tin/4。CK1~CK4如下图所示,相邻延时为1ns,即T/4=4ns/4=1ns。

图2 CK1~CK4的时钟延时

看图1,注意到鉴相器只比较Ckin和CK4,当CKin和CK4达到同相位时,Loop进入锁定状态。·那么我们设想一下这种情况:VCDL延时了8ns,而不是4ns,对于PD而言,CKin和CK4仍然达到了同相,此时Loop也会保持在这个状态。这时候如果我们观察Vcont电压的波形,会发现其进入了“稳定”状态,和正确的锁定状态看到的现象非常相似,然而这只是一种假象。此时,如果我们去测量CK1和CK2的延时,会发现delay=2ns,但别忘了我们的要求是delay=1ns!

我们继续思考一下,DLL是一种负反馈环路,既然VCDL可以延时2T,那难道是负反馈功能出错了吗?并不是,即使负反馈作用始终正确,但Vcont点的初始电位在不同的条件,如工艺角变化、温度变化、电压变化时其Vcont值可能不同。这就有可能一开始,VCDL的延时超出了T,但因为PD只对Ckin和CK4进行鉴相,Loop认为调节相位差不足,继续加大相位差,最终使VCDL延时2T,Loop进入假锁定状态。

根据上述内容,总结一下就是两点原因导致了谐波锁定:

(1)Vcont初始值不确定

(2)PD只对参考时钟和最后一项时钟进行鉴相

03 如何避免谐波锁定?

为了避免DLL的谐波锁定问题,需要增加额外的附加电路。如前所述,出现该情况的主要原因是Vcont的初值的不确定性导致的,所以笔者目前见到的最多的措施,是采用复位电路对Vcont进行赋初值,使其初值为VDD或者GND,初值下延时单元的delay达到最小。然后释放复位,Loop在负反馈作用下进入调节过程直至最终的锁定。

赋初值操作之所以能避免谐波锁定,是因为这种操作消除了Vcont的不确定性,使得DLL的建立过程中相位误差单向变化。从一开始,延时单元Tdu的延时是从最小开始慢慢增加,直到VCD延时一个T后Loop锁定。

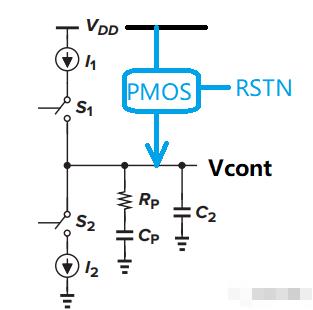

复位开关可加在如下图3所示的位置。左侧部分表示电荷泵CP。复位开关可使用PMOS,当RSTN=0V时,Vcont被PMOS上拉到了VDD。需注意,实际应用时可以不需要Rp,因为环路在原点只有一个极点,不存在稳定性问题。

图3 对Vcont增加复位上拉开关

-

4kHz谐波发生器2008-08-17 0

-

16900A DLL在加载后未锁定2018-10-10 0

-

HMC830锁定50/80MHz时谐波幅度很大是否正常?2019-01-09 0

-

4khz谐波发生器电路及制作2009-04-13 597

-

伪码测距延迟锁定环路(DLL)性能分析2009-08-07 757

-

如何编写dll文件2008-01-16 8680

-

谐波发生器电路图2009-03-21 3623

-

imm32.dll是什么2009-11-28 2369

-

comres.dll是什么,comres.dll怎么修复2009-11-28 1336

-

dinput8.dll是什么2009-11-28 4716

-

mfc71.dll是什么2009-11-28 2269

-

如何进行谐波发生器的设计2019-02-11 5079

-

锁定同步正弦发生器覆盖三十倍频程2023-01-12 935

-

DLL简介2023-05-22 915

-

DLL/PI的原理简述2023-12-15 376

全部0条评论

快来发表一下你的评论吧 !