efuseIP进行spice建模的实现方案

描述

1. efuse是什么?

回答efuse是什么之前,fuse是什么呢?fuse当然是熔丝,熔丝有很多种,常见的保险丝就是熔丝的一种。那什么是efuse呢?这个e的前缀表示电子的、可电子控制的。也就是说,efuse是可以电控制的fuse。

芯片设计中有时候要使用熔丝修调,工艺厂可提供的熔丝一般有金属熔丝和多晶熔丝,前者称作metal fuse,后者称作poly fuse。两种fuse随着过流的增加都会发生熔断,熔断前后的阻值差异巨大,比如熔断前可能在10Ω以内,熔断后可能在MΩ量级。因此,fuse具有以下两个明显的特点:

(1)通过选择是否熔断可以获得前后不同的阻值状态;

(2)熔断行为是不可逆的;

因为具有以上两个特点,所以在IC设计中,fuse被广泛应用在参数修调方面,当设计初值达不到要求或不理想时,可以通过对已经集成在IC中的fuse进行编程,从而改变配置,使性能参数达到目标值。由于不可逆特性,经过这种编程操作的IC的特性会固化下来,无法进行二次编程。所以应用在IC中的fuse也通常是为了出厂校正或者出厂修调。在一些数据需要加密的IC中,也会采用fuse来固化内部数据,使之不可更改。

2. efuseIP是什么?

实际的IC设计中,可能只需要用到很少量的fuse,这时候一般也就需要几个用几个,LAYOUT时按照设计规则放置就好了。但在需要大量控制字的应用中,直接使用很多单个的fuse就显得不那么经济了。这一方面是因为可靠性,另一方面也有面积、功耗等的考虑。这时候往往就需要用到efuseIP。

efuseIP是工艺厂提供的、具有全套资料且经过测试可直接调用的硬件IP。efuseIP包含多个熔丝单元,比如256个或者512个等,此外IP内部还会集成有读写控制等电路。既然集成有读写控制,efuseIP必须在一定的读写时序下工作。我们购买了工艺厂家efuseIP后,工艺厂家会提供相应的技术资料和.v文件等,.v文件其实就是用verilog编写的程序文件,但只是对efuseIP的行为的描述,该文件本身是不可综合的。

3. 为什么要进行efuseIP的spice建模?

目前正在设计的一款ADC芯片刚好需要用到efuseIP,由于efuseIP的.v模型无法直接带入spice或spectre仿真环境中,故只能通过混合仿真的方式进行顶层验证。为了能够用spectre或spice模拟仿真工具进行验证,所以就产生了对efuseIP进行spice建模的想法。

注意,这里说的"spice建模”,并不是100%用spice语法进行建模,而是建一个可以带入spice仿真环境的模型。

经过迭代尝试,最终还是建模成功了,并且经过仿真验证,已建模型的行为和厂家.v模型的行为基本一致。下面将解释具体的建模内容。

4. efuseIP的基本情况

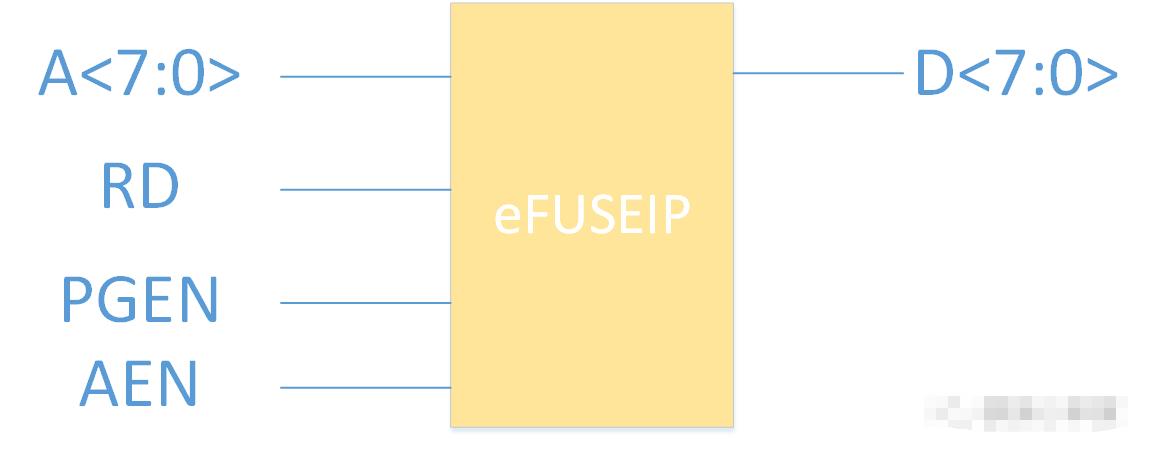

首先我们看下图,该efuseIP包含一个8位的地址输入A<7:0>、一个 读使能RD,一个编程使能PGEN,一个地址使能AEN,以及8位并行输出D<7:0>。

图1:eFUSEIP的输入输出示意图

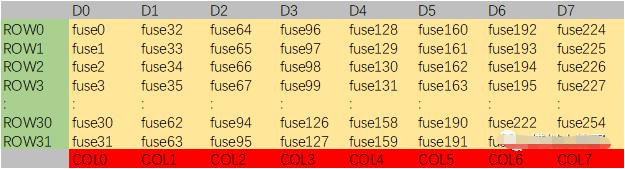

接着再看下表,其展示了厂家IP中各fuse的排布情况。可以看到,第一列从fuse0~fuse31,第二列从fuse32~fuse63,然后依次排布下去。

图2:熔丝的位置排布

以上介绍了efuseIP的基本情况,那实际中该efuseIP是怎样工作的呢?

对于上图所示的fuse阵列,为了精准控制每一个fuse,显然需要进行行列控制。A<7:0>的高3位可产生8个列信号,低5位可产生32个行信号,这样就可以对32*8的矩阵实现地址控制。需要编程时,令PGEN=1,RD=0,对指定地址位的熔丝进行熔烧操作。当需要读取熔丝数据时,令PGEN=0,RD=1,数据以每次8bit的形式并行输出,实际是一次读出一行数据,全部读出需要32次。

5. spice建模的具体实现

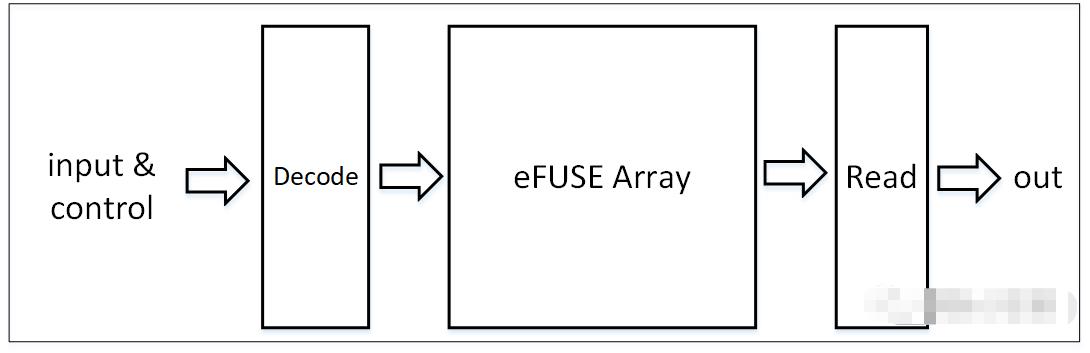

知道了efuseIP的行为,我们就可以着手进行建模了。看下图,最终的模型架构主要包括以下模块:Decode(译码电路,主要实现行列编码)、efuse Array(熔丝单元阵列)、Read(读取电路)

图3:模型电路架构图

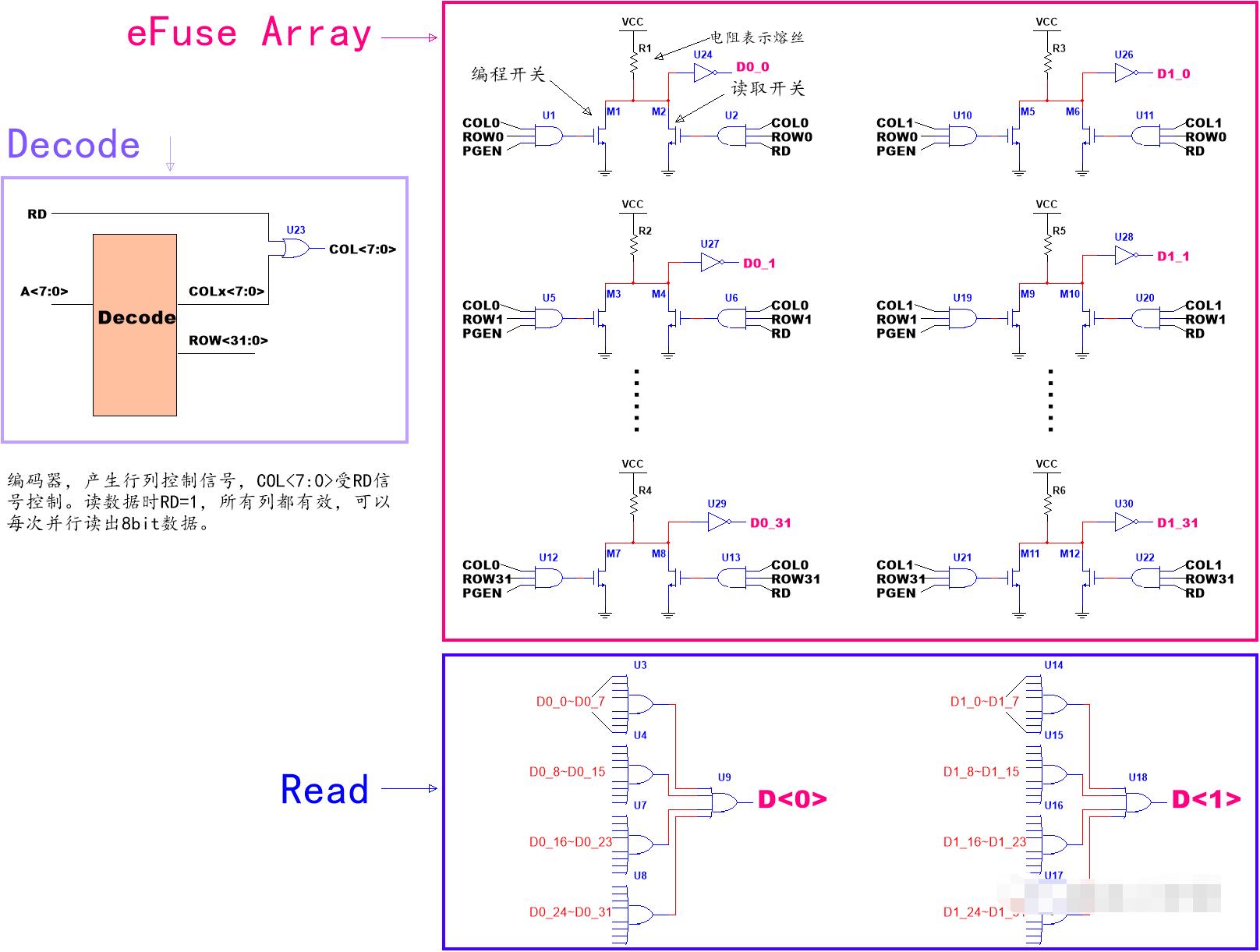

我们最终搭建出的spice模型如下图所示,该模型电路全部利用verilogA和理想器件构建而成。

图4: 模型原理图

5.1 Decode电路

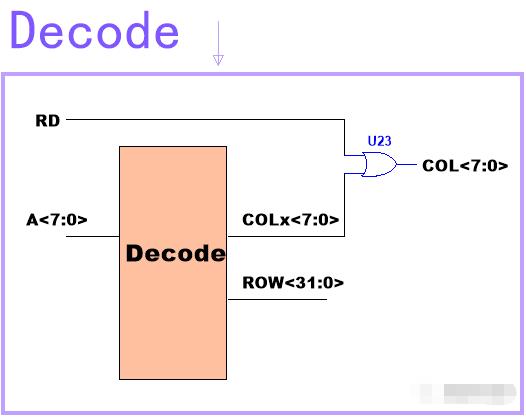

下图为译码电路的原理框图。地址信号为A<7:0>,其高三位A<7:5>作为3-8译码器的输入,产生8个列控制信号。低五位A<4:0>作为5-32译码器的输入,产生32个行控制信号。3-8译码器和5-32译码器可以用基本的组合逻辑电路实现,基本逻辑门可以调用理想的VerilogA模型。

图5: 译码电路原理框图

需要注意的是,RD与列控制信号COLx<7:0>或操作后输出真正的列控制信号COL<7:0>。这样一来,在数据读取时,RD=1,所有列信号都为1,表示所有列有效,就可以一次8bit读出有效行的所有数据。而熔丝编程时,RD=0,并不影响列控制信号,可以实现对每一位fuse的编程操作。

5.2 fuse 单元电路

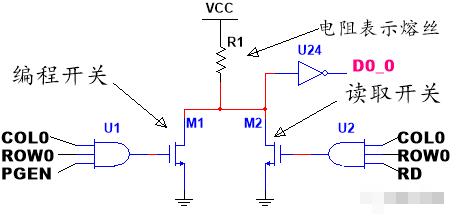

我们看下图,其为第0行、第0列对应的fuse单元电路。图中用R1表示fuse。M1为编程开关,大尺寸,可以流过大电流。M2为读取开关,提供读取电流。

图6: fuse单元电路

编程时:当行列信号以及PGEN同时有效,M1导通,流过大电流,熔断fuse。读取时:当行列信号和RD同时有效时,M2导通,提供一路读取电流,读取电流在fuse两端形成压降,输出点经过反相之后的值即为读取结果。具体为:

(1)fuse熔断前,R1很小,R下端电压为高,D0_0=0;

(2)fuse熔断后,R1很大,R1下端电压为低,D0_0=1;

5.3 Read电路

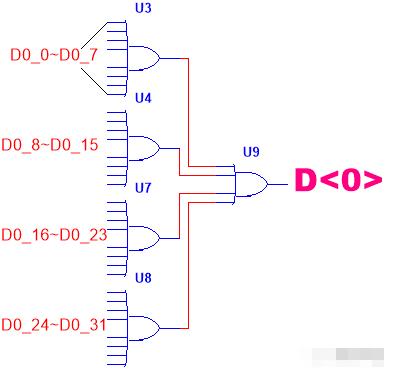

下图所示为第0列读取电路原理图,其实质上是将第一列的所有fuse单元的结果进行了求和。

图7:Read电路原理图

之所以可以用最简单的求和电路来实现,是因为基于这样一个认识:

因为读取的时候,是从第0~第31行依次来读的,也就是说开始读第0行时,其他行都不读取,所以其他行的数据为0,因此求和并不会影响当前行数据的读出。当然,读其他行的时候也是一样的道理。

6. 写在最后

说说这个模型的缺点吧。该模型不能实现编程然后读取的一体动作。为什么呢?因为fuse是用一个电阻代替的,而电阻是没有记忆能力的,无论编不编程,阻值一旦给定就不能改变。那么这一点有没有办法改进呢?我想是有办法的。设想有一个记忆单元,只要不受到编程触发,就一直保持为0,一旦受到编程触发,就变为1,那就可以解决这个问题。具有这种功能之一的,电平触发型DFF是一个选择。

-

功率器件 Spice 模型建立2024-04-12 0

-

木雕的扫描建模如何实现?2017-07-31 0

-

电源旁路之SPICE仿真与现实的差距2018-09-26 0

-

请问candence Spice能做氮化镓器件建模吗?2019-11-29 0

-

业界领先的半导体器件SPICE建模平台介绍2020-07-01 0

-

如何使用spice来进行模拟仿真?2021-04-12 0

-

如何为可变R-L-C元件的SPICE模拟行为建模?2021-04-22 0

-

求助,为pwm性能建模,想为驱动级找到一个spice模型2023-01-16 0

-

ADIsimPE如何导入SPICE模型,进行设计仿真?2023-11-17 0

-

基于spice3f5的建模工具的器件建模机制实现模块复用和快速原型化开发2017-12-05 1234

-

SPICE滞后建模的解决办法2022-04-26 1471

-

KT150电子管spice建模2022-06-13 879

-

ECLinPS 和 ECLinPS Lite SPICE I/O 建模套件2022-11-15 150

-

EPT Spice 建模套件2022-11-15 144

-

ECLinPS Max (SiGe) SPICE 建模套件2022-11-15 139

全部0条评论

快来发表一下你的评论吧 !