串并转换电路的实现方案

描述

当前设计的一款ADC芯片,其具有数据串行输出模式,由于串行输出的数据不能够直接后接理想DAC进行波形分析,因此不太方便。最好是能插入一个Serial_To_Parral的转换模块,将串行输出的数据转换为并行数据,再后接理想DAC产生模拟波形,如此就便于FFT分析了。

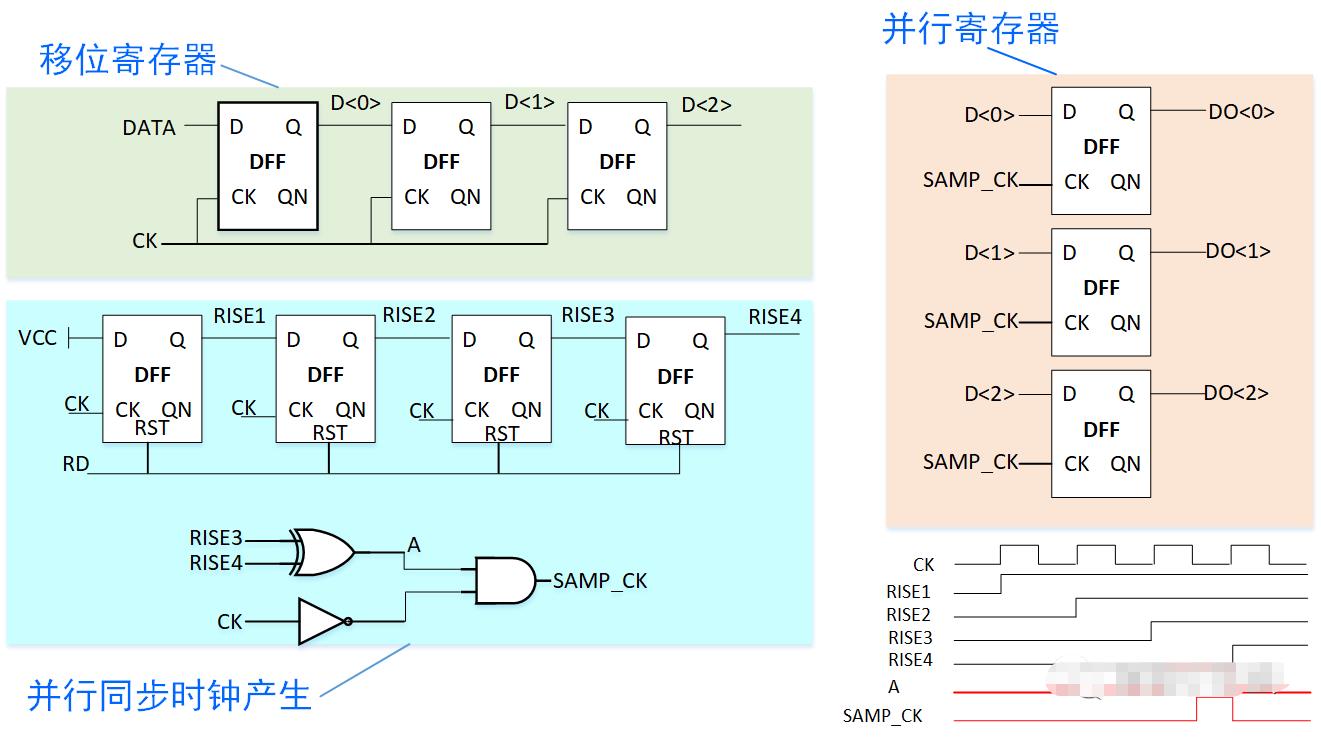

Serial_To_Parral:这里说的串并转换电路,指可以实现串行数据转并行数据的电路。本文提到的Serial_To_Parral模块是用VerilogA基本组件搭建的,以一个3bit数据的转换作为示例,其原理框图如下图所示:

图1:Serial_To_Parral原理框图

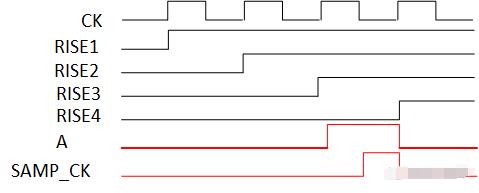

该电路的思路是:移位寄存器负责对DATA的每bit数据进行采样并且向右移位,移位寄存器的每级输出分别与右侧并行寄存器的输入相连。随着CK最后一次上沿采样完DATA数据后,在其后的半周期内将并行寄存器上的数据同步输出。

图2:相关时序图

并行寄存器的同步采样时钟为“并行同步时钟产生电路”产生。注意到,产生同步采样时钟的电路使用了RD信号对DFF进行复位。RD信号为ADC系统的读取使能信号,RD=0时有效。因此在RD=1期间,DFF复位,SAMP_CK=0,并行寄存器上的输出保持不变。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA设计思想与技巧之串并转换和流水线操作2012-02-10 0

-

串并转换74hc1642013-10-12 0

-

求串并转换74hc164应用实例2013-10-14 0

-

1to8串并转换2015-03-09 0

-

请问用labview怎样实现信源的串并转换?2015-06-18 0

-

FPGA串并转换实现问题2015-07-08 0

-

简单的串并转换怎样实现,不用移位寄存器。2015-12-14 0

-

求问,简单的串并转换怎样实现,不用移位寄存器。2015-12-14 0

-

大神啊~~简单的串并转换怎样实现,不用移位寄存器。2015-12-14 0

-

不用移位寄存器,简单的串并转换怎样实现?2020-07-16 0

-

求一款基于CPLD的串并转换和高速USB通信设计方案2021-04-13 0

-

如何去实现AT24存储器数据串并转换接口的VHDL设计?2021-05-27 0

-

求助大神!!!用伪双端口RAM实现高速数据流的串并转换2021-07-15 0

-

FPGA串/并转换的思想相关资料推荐2022-02-23 0

-

并串转换和串并转换2016-04-27 2341

全部0条评论

快来发表一下你的评论吧 !