基于英伟达芯片的自动驾驶典型架构设计

电子说

描述

NVIDIA DRIVE AGX 是一个可扩展的开放式自动驾驶汽车计算平台,充当自动驾驶汽车的 大脑。作为同类产品中硬件平台的佼佼者,NVIDIA DRIVE AGX 为功能安全的人工智能自动驾 驶提供高性能、高能效的计算。硬件方面,NVIDIA DRIVE 嵌入式超级计算平台处理来自摄像头、普通雷达和激光雷达传 感器的数据,以感知周围环境、在地图上确定汽车的位置,然后规划并执行安全的行车路线。软件方面,NVIDIA DRIVE AGX 具备可扩展和软件定义特性,平台能够提供先进的性能, 助力自动驾驶汽车处理大量传感器数据,并做出实时驾驶决策。

开放式 NVIDIA DRIVE 软件 栈还可帮助开发者使用冗余和多样化的深度神经网络 (DNN),构建感知、建图、规划和驾驶 员监控功能。通过持续迭代和无线更新,该平台变得日益强大。同时,开放式 NVIDIA DRIVE SDK 为开发者提供了自动驾驶所需的所有构建块和算法堆栈。该软件有助于开发者更高效地 构建和部署各种先进的自动驾驶应用程序,包括感知、定位和地图绘制、计划和控制、驾驶 员监控和自然语言处理。本文将分几个章节以当前应用最为广泛的主流英伟达芯片 Orin x 为例,分别从硬件和软 件两个方向来说明如何进行从软到硬件级别的开发和应用。

英伟达内部架构设计

以 Orin-x 为例,其中的 CPU 包括基于 Arm Cortex-A78AE 的主CPU 复合体,它提供通用高速计算能力;以及基于 Arm Cortex-R52 的功能安全岛(FSI),它提供了隔离的片上计算资源, 减少了对外部 ASIL D 功能安全 CPU 处理的需求。

GPU 则是 NVIDIAAmpere GPU,为 CUDA 语言提供高级并行处理计算能力,并支持多种工具, 如 TensorRT,一种深度学习推理优化器和运行时,可提供低延迟和高吞吐量。Ampere 还提供最先进的图形功能,包括实时光线跟踪。域特定硬件加速器(DSA)是一组专用硬件引擎,旨在从计算引擎中卸载各种计算任务,并以高吞吐量和高能效执行这些任务。

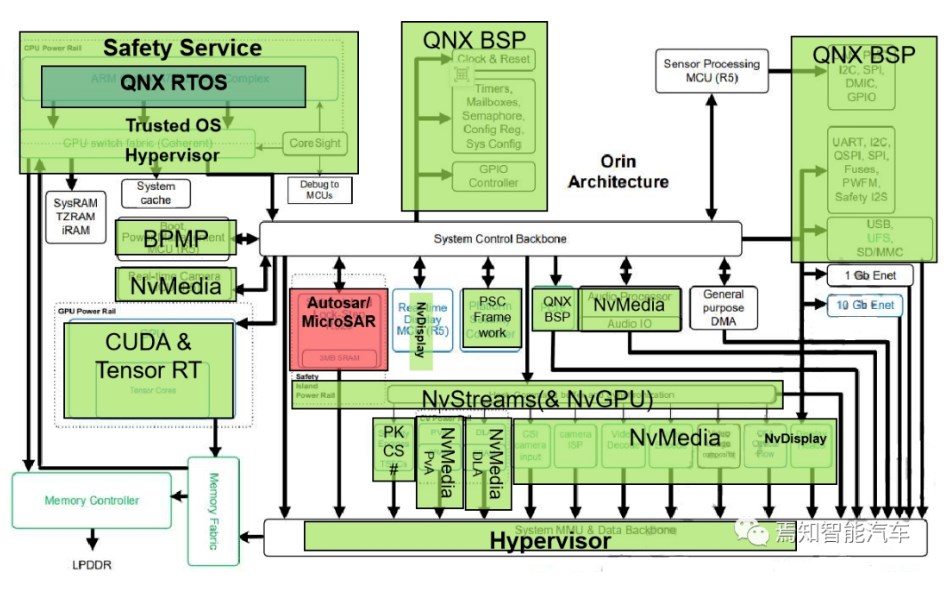

下图显示了 SoC 的高级架构,分为三个主要处理复合体:CPU、GPU 和硬件加速器。

整个芯片内部架构设计主要是按分块进行功能设计区分。包括操作系统底层软件QNX BSP(时钟Clock源&系统重启、CAN/SPI/I2C/GPIO/UART控制器、配置寄存器、系统配置)、实时运行系统QNX RTOS、Nv多媒体处理模块(传感器处理模块MCU(R5)、PVA、DLA、Audio Processor、MCU R5配置实时相机输入)、经典Autosar处理模块(用于Safety Island Lock-Step R52s)、安全服务Safety Service(ARM Cotex-A78AE CPU Complex、CPU Switch fabric Coherent、信息安全PSC)、神经网络处理模块(CUDA & TensorRT)。

基于英伟达芯片的自动驾驶典型架构设计

常规的 SOC 系统架构通常是包含有常规的 SOC+MCU 双芯片甚至三芯片的方式进行设计的。SOC 由于计算性能上的优势,一般在前端感知、规划中的计算应用场景比 MCU 更好。

MCU 由于具备较高的功能安全等级,可以作为控制执行的校验输出。业界对于英伟达芯片是否可以单纯作为类似 TDA4 一样的超异构芯片而独立承担任务, 一直都是褒贬不一的。原则上,从无论 Xavier 还是 Orin 系列,英伟达系列芯片设计都兼具 丰富的 AI 和 CPU 算力能力。考虑 L2+级别以上的自动驾驶系统开发而言,这种能力都是可 以完全适配整个方案设计的。

那么,行业内是否这样主推相应的设计方案了呢?答案是没有。

在英伟达 Datasheet 中关于最新安全需求中,针对 Orin 系列芯片的架构设计推荐方案中, 仍然需要使用特定的 MCU 用于失效分析和风险评估,这样就可以及时的定位到系统的严重 故障,从而确保满足由 ISO26262 标准所定义自动驾驶安全完整性能力要求(这块后续会单 独讲解)。同时,考虑到整个域控的电源管理,接入外置 MCU 也可以很好的提升其电源管 理能力,包括对进入睡眠模式的进入退出等等。

如上所设置的 MCU 在一定程度上也可以被称之为 Safe MCU(SMCU),开发系统过程 中需要使用一些安全等级较高的 MCU(一般需要达到 ASIL D 等级),如英飞凌 Aurix TC 系 列,瑞萨的 RH850 系列都可以充当 MCU 实现对 Orin 的 SMCU 接入。这样的 SMCU 实际是可 以充当整个系统开发的电源控制和严重失效故障规避的。

如上图所示表示了基于英伟达芯片设计系统架构的三层失效安全框架。整体上讲,该架 构从 SOC 层的基础服务、操作系统、虚拟机、实施运行环境再到 MCU 的实时运行环境几个 方面分别实现三层级失效安全保护。SOC 层和 MCU 层分别在 NvIVC、NvIPC、SPI/Error Pin 层 级上进行健康和独立的看门狗监控。其中,SOC 内部本身会承载一部分锁步安全校验 Lockstep FSI , 并 在 核 心 CPU 复 合 体 CCPLEX ( Carmel CPU complex running the capture stack and applications.表示运行捕获堆栈和应用程序的 Carmel CPU 复合体)上运行虚拟机 Hypervisor,CPU 核上采用具备高功能安全等级的 QNX 操作系统,完成应用软件看门狗、中间件、应用 层软件以及驱动软件的资源调度。当然,对于实时运行系统而言,还是运行在标准的 Autosar 上。

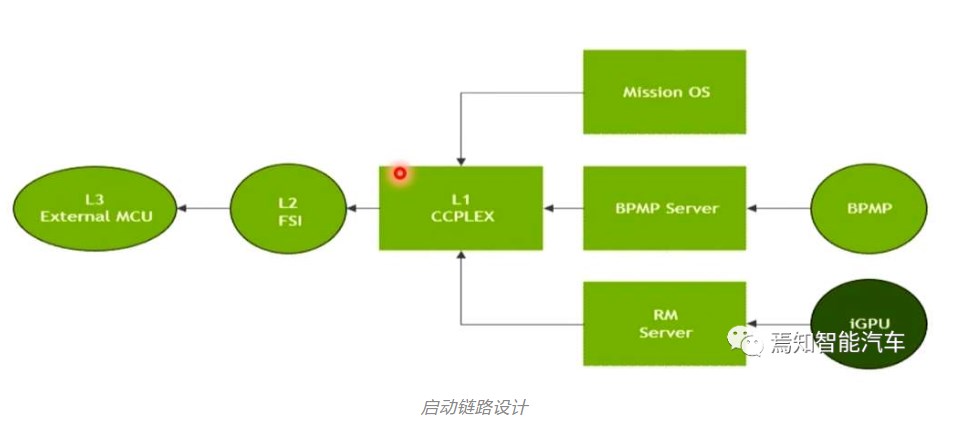

如下图所示的安全架构表示了外置 MCU 如何支持在 SOC 上的启动数据流,并通过一个 标准错误报告/传播数据流来进行有效的安全启动。其中,整个程序与数据引导加载过程包 括三个层面:Boot L1 级 CCPLEX、Boot L2 级 FSI、Boot L3 级 External MCU。

在 L1 级程序启动过程中,底层启动包括利用“引导和电源管理处理器(BPMP)”终端 (一个较小的 ARM 内核位于系统的核心位置)加载底层启动程序到 BPMP 服务器,由虚拟机Hypervisor 或操作系统 Safety OS 对相应的启动程序文件进行调用。总体上,BPMP 的 Cortex-R5 可以实现:

1、锁步核配对

2、Arm 7-R ISA

3、向量中断支持:基于菊花链 Arm PL192 矢量中断控制器(AVIC)

4、用于局部 SRAM 的 TCM 接口

5、完备指令和数据缓存(其中涉及 32KB 指令缓存 I-Cache 和 32KB 数据缓存 D-Cache)

6、Arm 处理器修正

同时,底层 iGPU 核也会由 RM 集成式服务器驱动起来。最终在第一层加载启动程序 L1 CCPLEX(在 NVIDIA 中称为 CPU Complex 即高性能 64 位 Arm 内核)中完成操作系统任务 调度、引导管理程序加载、RM 服务器驱动 GPU 核等各项专业任务。

此外,L2 级主要还涉及前序文章中提到的功能安全岛校验 FSI。文章后续会单独进行说 明。

最后,外挂的 SMCU 可以另外在做一层安全保护和启动管理配置。这样就可以从安全的 角度完整的驱动整个芯片工作。

功能安全岛设计原理

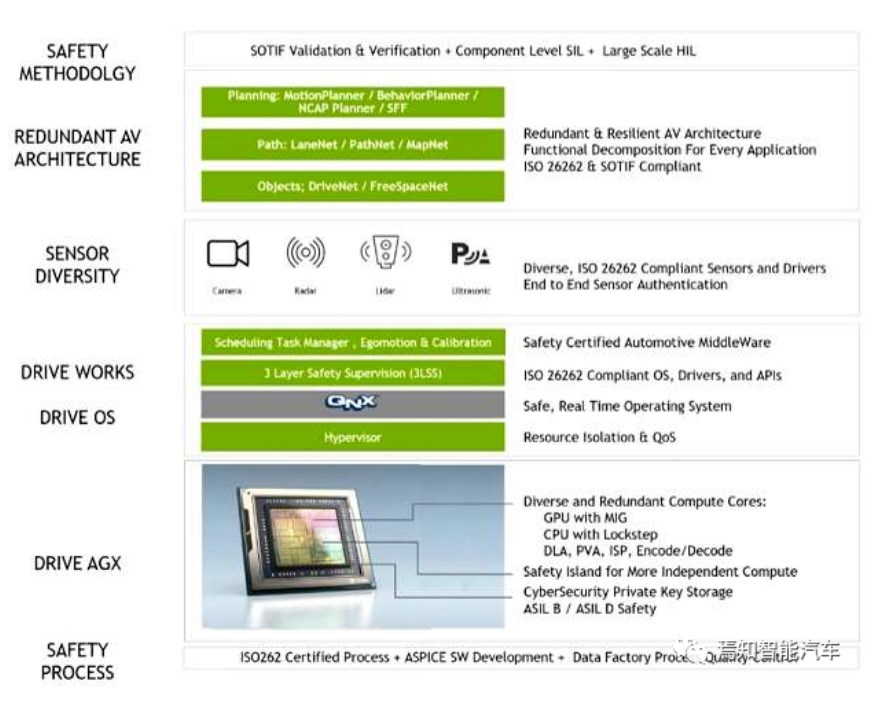

如图2显示了如何在英伟达系列芯片中加载 FSI 及底层相关模块驱动引导程序。英伟达系列芯片在功能安全设计上,Orin 系列通过制定目标实现 ASIL D 系统能力设计和ASIL B/D 随机错误管理能力设计。包括基于 SOC 芯片硬件的 ASIL 分解需求到各个核,确保核间设计一致性可以满足 ASIL D 需求,并应用标准的 ASIL D 开发流程到整个功能安全设计中,从底之上分别对安全流程、Drive AGX、操作系统 Drive OS、Drive Work、传感器、冗 余架构设计、安全策略几个方面分别进行相应的安全设计。

英伟达系列芯片的功能安全岛(FSI)是一个包含 Cortex-R52 和 Cortex-R5F real 的处理器集群,并具有专用 I/O 控制器的时间处理器的核心。例如,Orin-X 中的 FSI 模块具有自己的电压轨、振荡器和PLL、SRAM,以确保与 SOC 内部的其他模块相互作用最小,并实现如上模块相互之间无干扰。

Orin-x 系列 FSI 功能包括:

Cortex-R52 处理器,也称为安全 CPU,具有 DCLS(双核锁步)模式下的 4 个内核(共 8 个物理内核),可运行经典 AUTOSAR 操作系统,实现错误处理、系统故障处理和其他客户工作负载,综合性能约为 10KDMIPs。

Cortex-R5F 处理器,也称为加密硬件安全模块(CHSM),用于通过 CAN 接口运行加密 和安全用例,如安全车载通信(SecOC)。

整个FSI机制上总体包含有如下的一些安全指令和控制接口信息:

1、安全和 CHSM CPU 每个核心的紧密耦合内存、指令和数据缓存。

2、安全岛上总共有 5MB 的片上专用 RAM,以确保代码执行和数据存储可以保持在 FSI 内。

3、岛上有专门用于与外部组件通信的专用 I/O 接口。包含1个 UART,4 个 GPIO 口。

4、硬件安全机制,如 FSI 内所有 IP 的 DLS、CRC、ECC、奇偶校验、超时等。

专用热、电压和频率监测器。

5、逻辑隔离,确保与 SoC 的其他部分有足够的错误恢复时间FFI。

FSI的实例解析1:

这里本文将通过一个例子说明设计 FSI 为目的描述相应的错误处理机制,其中包括对如下过程的处理模式:

1、在基于 Xavier 的平台上调试 CSI 捕获错误的各种方法。

2、如何确定使用哪种方法进行调试。

3、如何识别错误。

4、错误的可能根本原因。

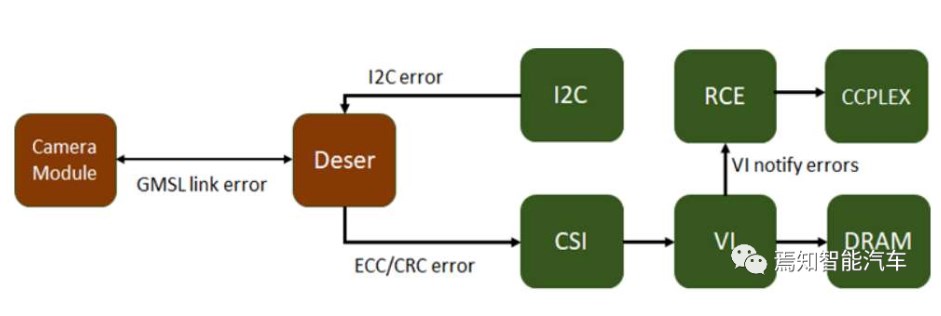

相机捕获过程中可能发生错误的图层如下:

每当解码在 SoC CSI 接口接收到的 CSI 数据包并将原始帧数据写入内存遇到错误时,VI 硬件引擎就会将这些错误通知给RCE。在 CCPLEX 上运行的捕获堆栈可以从 RCE 查询捕获状态并显示:CSI 数据流的 ID、发生错误的 VC ID、错误类型、每个错误类型的详细错误。错误状态为确定根本原因和确定后续步骤提供了一个很好的起点。如果 VI 引擎没有成功捕获帧,也没有遇到错误并向 RCE 报告错误,则会显示帧启动或结束超时错误消息提示。 这可能是由于以下两个原因之一:

1、解串器不是流数据。

2、VI 通道未配置为捕获正确的数据类型/VC id。

英伟达系列芯片如何考虑信息安全

对于英伟达芯片来说,有效的保证信息安全主要是通过两个层面:其一是信息安全芯片内核模块Tegra。尽管这一芯片曾经在2018年也出现过安全漏洞。有极端黑客利用NVIDIA Tegra X1芯片中的漏洞破解了Switch主机,此漏洞允许任何人在其上运行任意代码,这意味着自制系统和盗版软件可以随意运行。然而,通过不断地内部优化,英伟达已经在很大程度上完成了漏洞修补。

比如,在使用相同 Tegra X1 CPU 的初始 Nintendo Switch 控制台上,在 ROM 引导加载程序中发现了一个漏洞,就通过恢复模式和缓冲区溢出实现修复。NVIDIA 可以使用内置可编程保险丝将补丁存储到内部 ROM 中解决这类修复问题。这样既考虑了薄弱环节又兼顾了安全性,减少代码 bug。

又如,硬件设计的性质意味着某些内部硬件模块无法被 CCPLEX 访问,只有 BPMP 能够操纵它们。包括 u-boot 在内的所有低级引导步骤都可以通过签名的二进制文件来确保安全。它们的密钥可以存储在 CPU 中的一次性可编程保险丝中。U-boot 本身可以配置为使用签名的FIT 映像,从而提供一个安全的引导链,一直到 Linux 内核。初始 ROM 引导加载程序和 TegraBoot 也都支持完全冗余的引导路径。

Tegra是英伟达芯片中特有的信息安全芯片内核,Tegra Security Controller(TESC)是一种信息安全子系统,他有自己的可信任根ROM、IMEM、DMEM,Crypto 加速器(AES、SHA、RNG、PKA),关键链路和关键存储。TSEC 提供了一个片上TEE(可信任执行环境)可以运行NVIDIA-标记的为处理代码。TSEC是一种典型的安全视频回放解决方案,下载信息安全运行所需的HDCP1.x 和2.x连接授权和完整的线端连接检测。

整体来说,TSEC可以支持:

1)线端HDMI 1.4上的HDCP 1.4和 线端HDMI 2.3上的HDCP 2.0 2.1;

HDCP连接管理没有暴露受保护的内容,也无需运行在CPU上的软件钥匙。用于 HDCP 链路管理的两个软件可编程独立指令队列(最多可容纳 16 条指令);整个芯片能够独立于播放器在 HDCP 状态检查失败时禁用 HDMI 输出。

2)平台安全控制器;

他是一个高安全子系统,他可以保护和管理SOC中的资产(钥匙、保险丝、功能、特性),并提供可信任的服务,提升自由的抵御对 SOC 的攻击,并可以提高对子系统本身的软件和硬件攻击的保护水平。

3)钥匙管理和保护;

PSC 将是唯一可以访问芯片中最关键秘钥的机制。该子系统代表了 Orin-x 中最高级别的保护,并且该子系统本身对各种软件和硬件攻击具有高度的弹性。

4)授信服务;

例如,在 SOC 安全启动期间,主要的 PSC 服务可以完成有效的安全身份验证、提供额外的密钥/ID/数据、密钥访问和管理、随机数生成和授信的时间报告。

5)信息安全监控。

PSC 将负责定期的安全管理任务,包括持续评估 SOC 的安全状态,主动监控已知或潜在的攻击模式(例如,电压故障或热攻击),降低硬件攻击风险,并在检测到有攻击的情况下采取有效的措施。PSC 将能够接受各种软件更新来作为解决方法,以提高现场系统的稳健性。

其二,是安全引擎(SE)的应用。他可以为加密算法提供硬件加速。

安全引擎SE中有两种情况针对软件使用是有用的。其一,TZ-SE只能被可信任区域软件所访问。其二,NS/TZ-SE可配置用来被可信任的软件区域或非安全软件所访问。安全引擎SE可以为各种加密算法提供硬件加速以及硬件支撑密钥保护。SE提供的加密算法可以被软件用来建立加密协议和安全特性。所有加密运算都是基于国际标准技术协会NIST批准的加密算法。

英伟达的安全引擎SE可支持包含如下的所有信息安全保障能力:

NIST合规的对称以及非对称加密和哈希算法、侧信道对策(AES/RSA/ECC)、独立并行信道、硬件钥匙访问控制(KAC)(基于规则,增强硬件访问控制的对称钥匙)、16xAES,4xRSA/ECC钥匙孔、硬件密钥隔离(仅针对AES钥匙孔)、读保护(仅针对AES钥匙孔)、硬件钥匙孔函数、密钥包装/解包功能(AES->AES钥匙孔)、钥匙从钥匙孔分离(KDF->AES钥匙孔)、随机钥匙生成(RNG->AES钥匙孔)。

总结

本文从整个英伟达芯片的核心架构、功能安全、信息安全等角度完整的剖析了其在应用过程中的主要特性和策略优势。对于如何利用英伟达系列芯片进行开发而言,充分的考虑其内部架构并结合其功能安全和信息安全能力对于整个开发调优都显得尤为重要。后续文章将分别从硬件开发和软件开发的角度分别进行详细的策略剖析。

审核编辑:刘清

-

【话题】特斯拉首起自动驾驶致命车祸,自动驾驶的冬天来了?2016-07-05 0

-

自动驾驶真的会来吗?2016-07-21 0

-

自动驾驶的到来2017-06-08 0

-

AI/自动驾驶领域的巅峰会议—国际AI自动驾驶高峰论坛2017-09-13 0

-

如何让自动驾驶更加安全?2019-05-13 0

-

自动驾驶AI芯片现状分析2020-12-04 0

-

自动驾驶OS市场的现状及未来 精选资料推荐2021-07-27 0

-

自动驾驶系统设计及应用的相关资料分享2021-08-30 0

-

自动驾驶技术的实现2021-09-03 0

-

英伟达DPU的过“芯”之处2022-03-29 0

-

安培GPU发布 英伟达自动驾驶芯片算力升级2020-06-05 2852

-

自动驾驶备受关注 小马智行完成D轮融资 英伟达将量产自动驾驶芯片DRIVE Orin2022-03-30 3046

-

基于英伟达芯片的自动驾驶典型架构设计方案2023-03-30 627

-

自动驾驶基础架构2023-06-01 170

-

高通自动驾驶靠软件开发革新力压英伟达自动驾驶芯片2024-02-20 883

全部0条评论

快来发表一下你的评论吧 !