SoC接口技术之低速接口分析(上)

电子说

描述

1

UART

1.名词解释

UART:

全称 Universal Asynchronous Receiver/Transmitter,中文可译为通用异步收发器。

2.历史由来

UART的发明是由于贝尔自己需要将一个电传打印机(Teletype)连接到一个PDP-1,需要将并行信号转换为串行信号。贝尔于是设计了一个使用大约50个独立部件的电路。这个想法被证明是受欢迎的。当时西部数据公司(Western Digital)是一家制造计算机芯片的小公司,它设计了单芯片版的UART。

3.应用场景

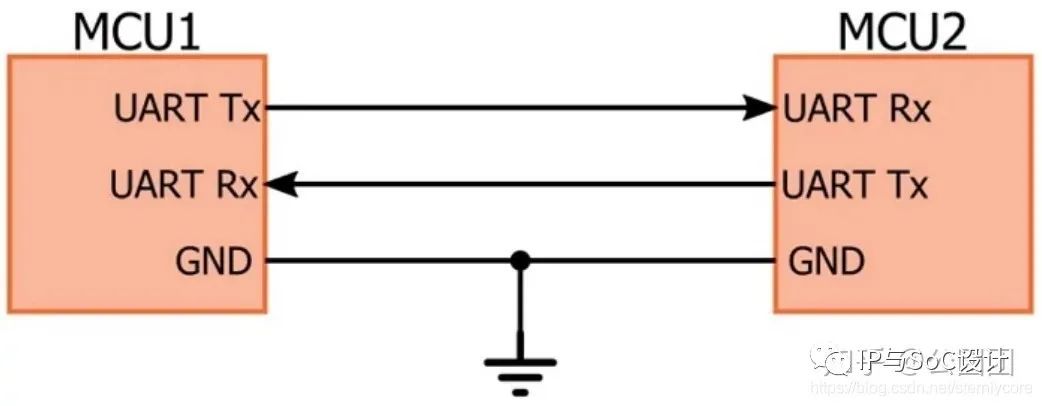

UART当前常用于MCU的低速互联,最少仅需要两根信号连接(TXD和RXD),信号支持TTL电平,RS232电平或者RS422电平。UART为全双工异步通信协议,最高支持115200bps的波特率(常用波特率为9600bps)。

4.协议解析

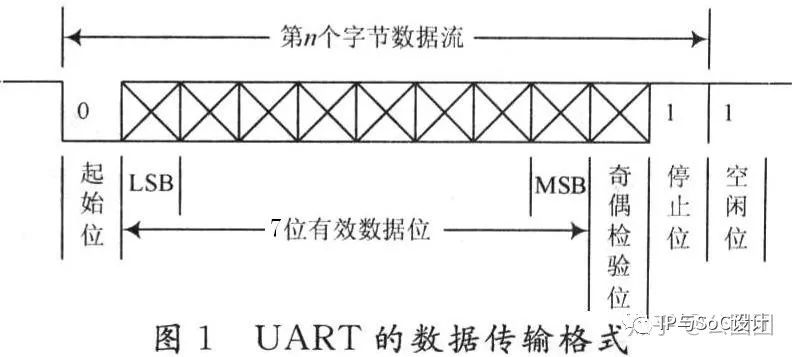

UART定义了一种串行传输协议,单次可传输一个字符,包含5到8bit有效数据(常采用7bit数据,ASCII)。

UART的一个字符除了包含有效数据位外,还包含起始位1bit,奇偶校验位1bit和停止位1bit(也支持1.5bit或者2bit配置)。UART一次传输最多8bit有效数据而不是更多的原因是其设计标准收发两端的频率误差在10%以内,当收到的数据为8bit时误差控制在1bit内,保证了数据的采样不会出错。

5. 协议实现

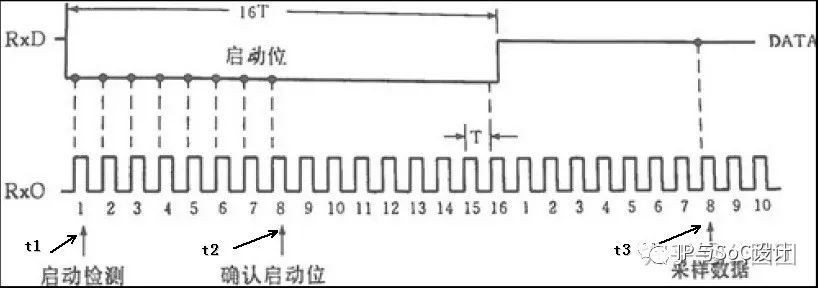

UART接收使用高频时钟进行采样,在最早的8086芯片中为兼顾速度和稳定性,常采用波特率的16倍时钟进行采样。当主时钟频率确定时,IC实现中可以通过设定波特率寄存器N实现任意波特率。

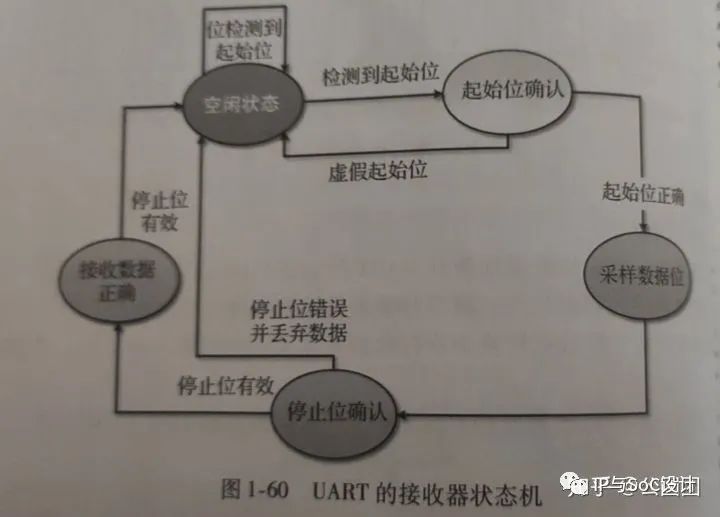

一个典型的UART接收器的状态机设计如图所示,在空闲状态时接收机通过监测接收信号从1变0,确定接收的起始位。为消除通信线路噪声的影响,只有连续接收到N/2个0后才认为这是一个真正的起始位,并开始在最佳采样点(N/2时刻)采样数据位。

6. 流程控制

UART的流控包括硬件流控和软件流控两种。

硬件流控基于RS232的两个信号接口RTS(数据发送请求)和CTS(数据发送允许),一端设备的RTS与另一端设备的CTS相连。RTS与CTS均为低电平有效,数据接收设备通过置低RTS接口通知发送设备的CTS接口,发送设备可以发送数据。

软件流控通过带内传输XOFF和XON信号,控制发送的起停。数据接收设备通过发送XOFF通知数据发送设备停止发送数据。数据接收设备通过发送XON通知发送设备继续发送数据。

2

SPI

1.名词解释

SPI 全称 Serial Peripheral Interface,中文译为串行外围设备接口。

2.历史由来

最早是由Motorola(摩托罗拉)公司开发的全双工同步串行总线,常用于微控制器与外设之间的连接比如SD卡,液晶屏等外设。SPI没有统一的协议规范,但由于其广泛的使用,根据实际使用中大家通用的习惯形成了一个类似行规的标准,具体的应用需要实际参考特定器件手册。

3.应用场景

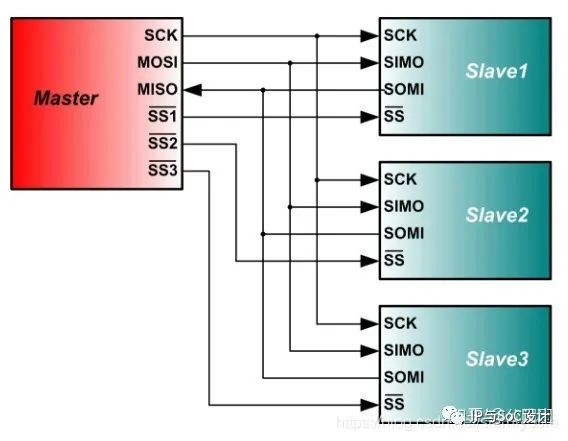

SPI用于在单个主控制器和一个或多个从设备之间交换数据,譬如MCU与EEPROM、FLASH、AD转换器的连接。SPI的两端中提供时钟的为Master,接收时钟的为Slave。SPI最少采用四线连接,SCLK,SS,MOSI,MISO。SPI按帧进行数据交换,支持的字长不限于8bit,可根据应用特点灵活选择消息字长。SPI是源同步时钟协议,支持100MHz以上的高速时钟。

4.协议解析

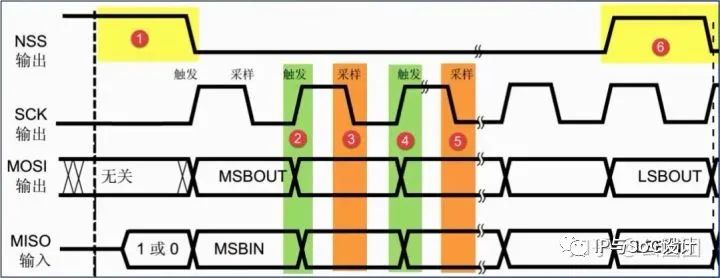

NSS电平由高变低,则产生起始信号;NSS电平由低变高,则产生停止信号。从机检测到自己的NSS线电平被置低,则开始与主机进行通讯;反之,检测到NSS电平被拉高,则停止通讯。

MOSI和MISO线在SCK的每个时钟周期传输一位数据,开发者可以自行设置MSB或LSB先行,不过需要保证两个通讯设备都使用同样的协定。

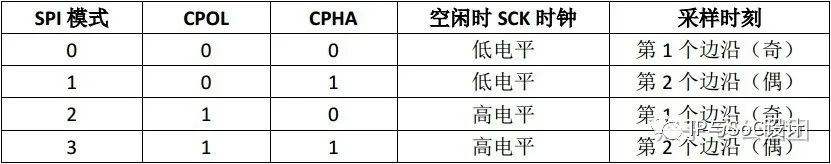

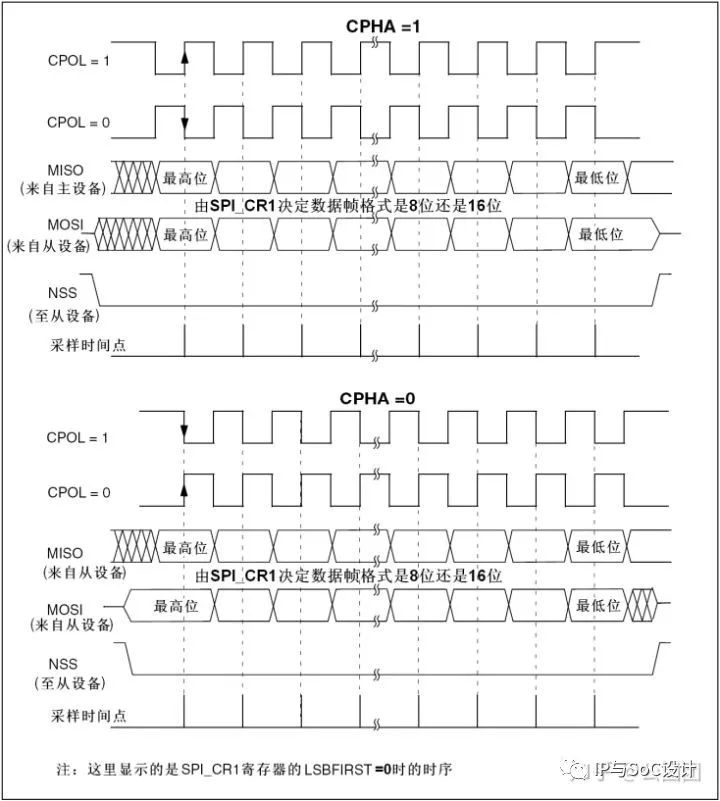

根据SCK空闲状态的电平(CPOL)和数据采样时刻(CPHA)的不同,SPI有四种通讯模式。Master和Slave需要工作在相同的模式下才能正常通讯,Master的MOSI如果在SCK上升沿launch数据,Slave的MOSI需要在SCK的下降沿capture数据,反之亦然。

当CPHA=0时,Master需要在第一个SCK的边沿出现前将数据在MOSI上准备好。

5. 协议实现

Motorola定义5类寄存器:

SPI Control Register 1 (SPICR1)控制寄存器1,极性控制,数据长度控制

SPI Control Register 2 (SPICR2)控制寄存器2

SPI Baud Rate Register (SPIBR)波特率寄存器

SPI Status Register (SPISR)状态寄存器

SPI Data Register (SPIDR)数据寄存器

6. SPI读写

SPI读写每笔传输交换一帧数据,一帧数据的bit数据可以是8bit,16bit或者其他数量的bit。

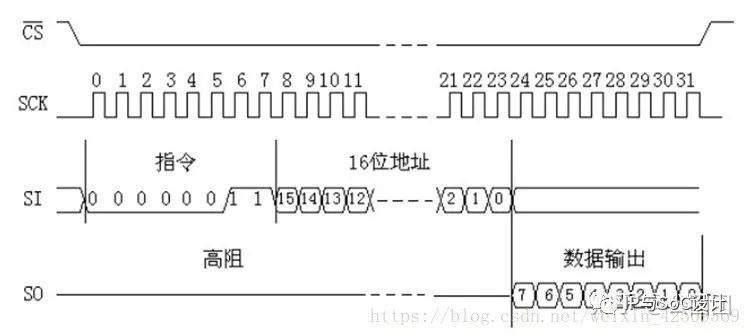

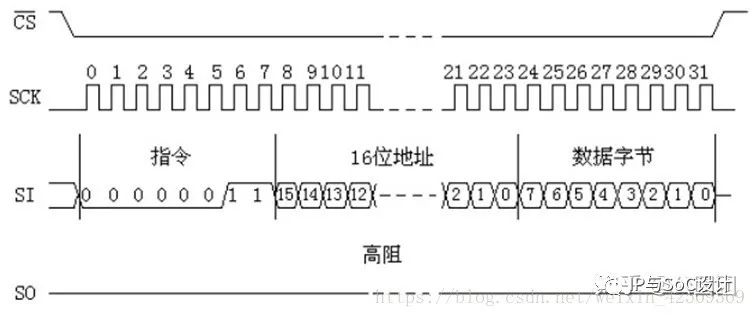

SPI读:片选---读指令---地址---数据读出

SPI写:片选---写指令---地址---数据写入

7. DSPI和QSPI

DSPI和QSPI主要用于存储器接口,其帧格式由存储器定义。归纳下来,QSPI的传输分为两种类型,第一种类型是传统的SPI的单线传输,第二种是QSPI的四线传输。

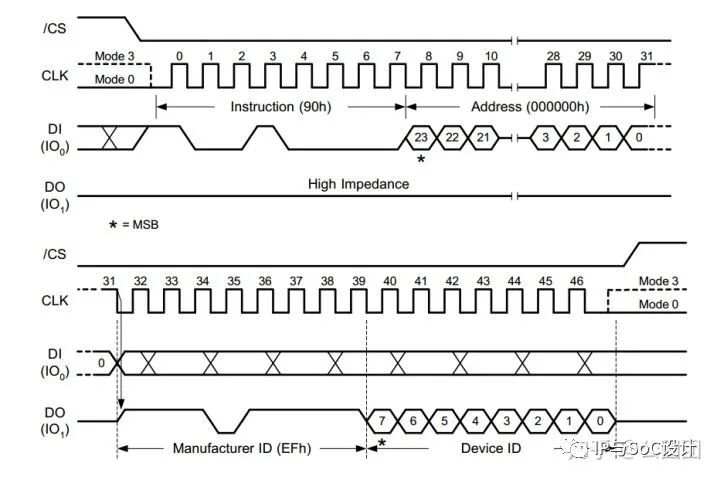

第一种类型传输常用于状态和控制寄存器的读写,譬如读ID。该传输过程采用MOSI和MISO进行数据交换,一帧数据是46bit。此外,单线传输也支持数据的读写。

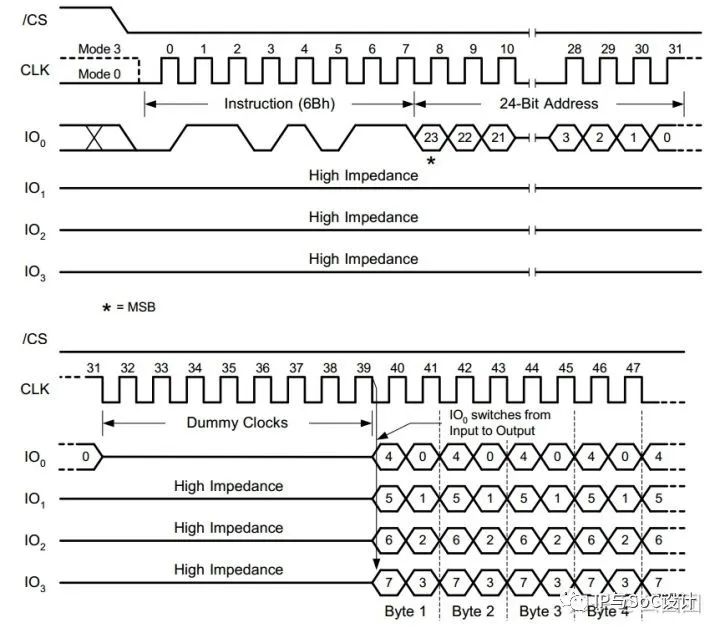

第二种类型的传输常用于数据的读写,譬如四线写数据。该传输包含了两个阶段,第一个阶段是命令和地址阶段,第二个阶段是数据传输阶段。第一个阶段,采用单线传输,通过MOSI向器件发送命令和地址。第二个阶段,采用四线传输,通过四个IO向器件发送或者读取数据。

此外,读数据时在第一个阶段和第二个阶段中间会插入Dumy Clocks。

3

JTATG

1.名词解释

JTAG,全称Joint Test Action Group,中文名称联合测试行动组。

2.历史由来

1990年JTAG正式由IEEE的1149.1-1990号文档标准化,在1994年,加入了补充文档对边界扫描描述语言(BSDL)进行了说明。从那时开始,这个标准被全球的电子企业广泛采用。边界扫描几乎成为了JTAG的同义词。

3.应用场景

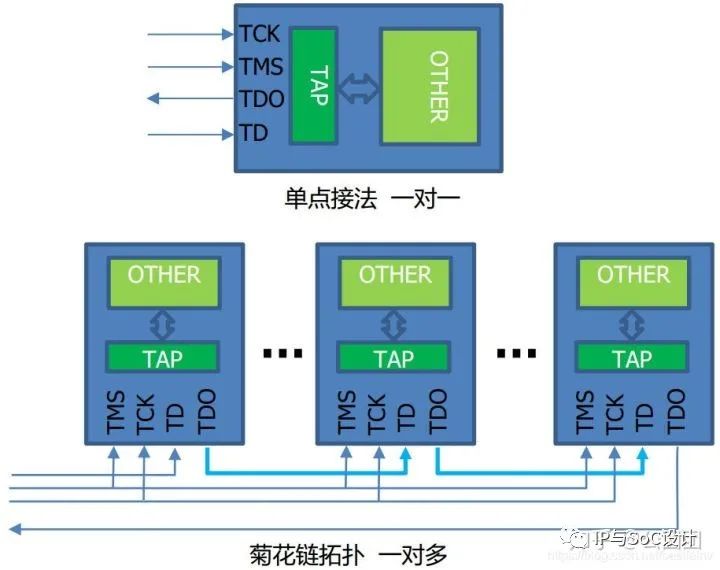

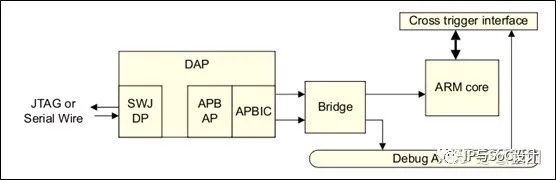

JTAG的基本原理是在器件内部定义一个TAP(Test Access Port,测试访问口)通过专用的JTAG测试工具对内部节点进行测试。当前JTAG协议也用来对芯片进行调试,JTAG通过器件内部的DAP(Debug Access Port,调试访问)访问内部总线。

JTAG最少使用四个信号,包括TCK,TRST,TMS,TDI和TDO,最高支持100MHz的串行数据传输。

-

微机接口技术课件2009-06-12 0

-

WCDMA无线接口技术2009-09-18 0

-

采用的IP核与系统的接口技术2019-05-27 0

-

基于IP核的SoC接口技术2019-06-11 0

-

MVB总线接口技术2020-04-10 0

-

谈谈微机原理与接口技术2021-07-28 0

-

微机接口技术尝试2021-09-10 0

-

微机原理与接口技术2021-09-10 0

-

微机接口技术实用教程2021-09-13 0

-

《单片机与接口技术》试卷集2010-08-11 441

-

开放核协议—IP核在SoC设计中的接口技术2006-03-24 676

-

高清晰视频会议终端应用接口分析2010-02-21 2100

-

MAVLink学习之路05_ MAVLink应用编程接口分析2020-03-07 5165

-

SoC接口技术之低速接口分析(下)2023-04-04 1308

全部0条评论

快来发表一下你的评论吧 !