同步复位信号如何跨时钟域

可编程逻辑

描述

XPM_CDC还提供了XPM_CDC_SYNC_RST用于处理同步复位信号的跨时钟域情形。这种情况下,该复位信号通常由用户逻辑在某个时钟域(例如clk_tx)下生成,提供给另一个时钟域(例如clk_rx)作为同步复位信号使用。与XPM_CDC_ASYNC_RST的差别在于:XPM_CDC_ASYNC_RST的目的是异步复位信号同步释放,即仅在释放(Deassert)时复位信号与接收时钟同步;而XPM_CDC_SYNC_RST则要求在激活(Assert)和释放(Deassert)时该复位信号都要与接收时钟同步。为了达到此目标,要求复位信号的有效宽度可以保证复位信号有效时接收时钟能稳定地采样到有效值至少两次。

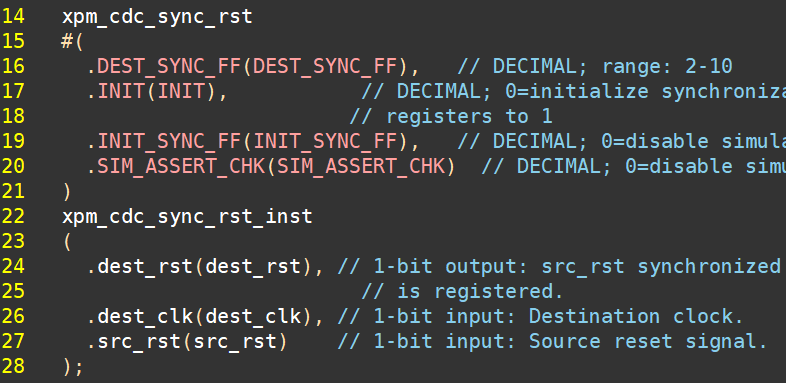

XPM_CDC_SYNC_RST的Verilog代码如下图所示。代码第16行参数DEST_SYNC_FF取值范围为2~10的整数,定义了级联寄存器的个数;INIT取值为0或1,定义了这些级联寄存器的初始值;INIT_SYNC_FF取值为0或1,用于指定仿真时这些初始值是否生效,为1时生效;SIM_ASSERT_CHK取值为0或1,用于显示仿真时给出的信息,为1时,将这些信息打印在仿真的log文件里。

我们将这些参数设置如下进行仿真:

DEST_SYNC_FF = 4

INIT = 0

INIT_SYNC_FF = 1

SIM_ASSERT_CHK = 1

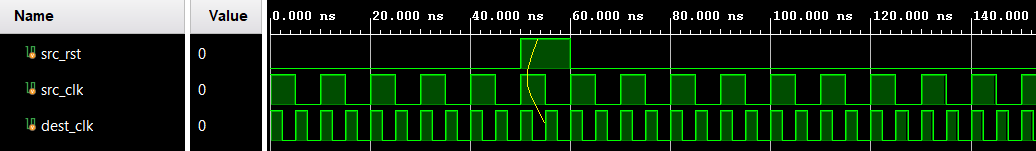

如果在复位信号有效时,接收时钟未能稳定地采样到至少两次,如下图所示情形,那么仿真时就好给出相应的信息。

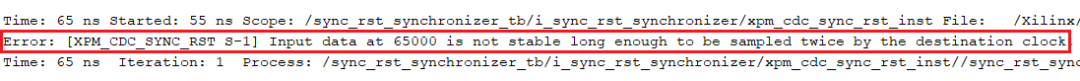

满足上述条件时,仿真结果如下:

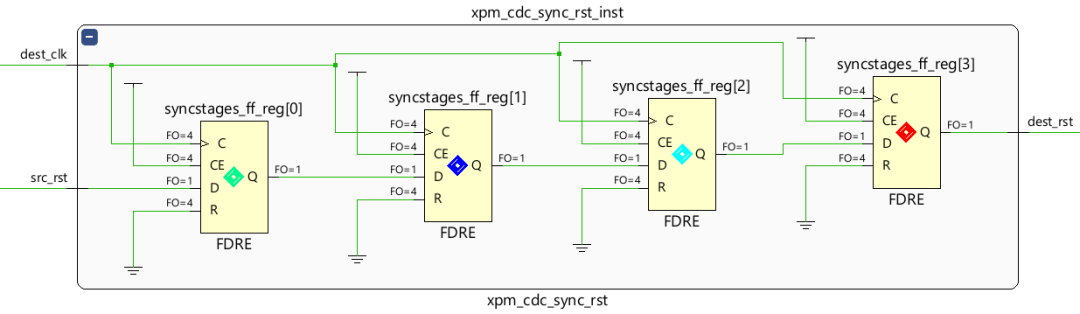

从综合结果来看,本质上这就是一个级联触发器电路,如下图所示。触发器的初始值由参数INIT决定,同时对这些级联触发器也设置了属性ASYNC_REG。

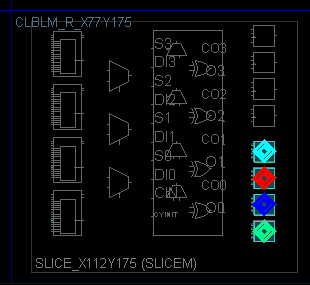

从布线结果来看,由于属性ASYNC_REG的作用,工具会将这4个触发器放置在一个SLICE内,如下图所示。对于7系列FPGA,建议级联触发器的个数控制在8以内(包含8),因为7系列FPGA每个SLICE内有8个触发器。如果级联触发器个数大于8,例如为10,工具会将其放置在竖直方向相邻的两个SLICE内。对于UltraScale系列FPGA,此值可以大于8,因为UltraScale一个SLICE内有16个触发器。

编辑:黄飞

-

FPGA设计中有多个时钟域时如何处理?2012-02-24 0

-

跨时钟域为什么要双寄存器同步2020-08-20 0

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 0

-

探寻FPGA中三种跨时钟域处理方法2020-10-20 0

-

三种跨时钟域处理的方法2021-01-08 0

-

三种FPGA界最常用的跨时钟域处理法式2021-02-21 0

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 0

-

如何处理好跨时钟域间的数据呢2021-11-01 0

-

两级DFF同步器跨时钟域处理简析2022-02-17 0

-

FPGA跨时钟域处理简介2022-02-23 0

-

看看Stream信号里是如何做跨时钟域握手的2022-07-07 0

-

调试FPGA跨时钟域信号的经验总结2022-11-15 0

-

同步复位和异步复位电路简介2019-08-12 7024

-

同步复位和异步复位到底孰优孰劣呢?2024-01-16 425

全部0条评论

快来发表一下你的评论吧 !