FPGA设计的五个主要任务

电子说

描述

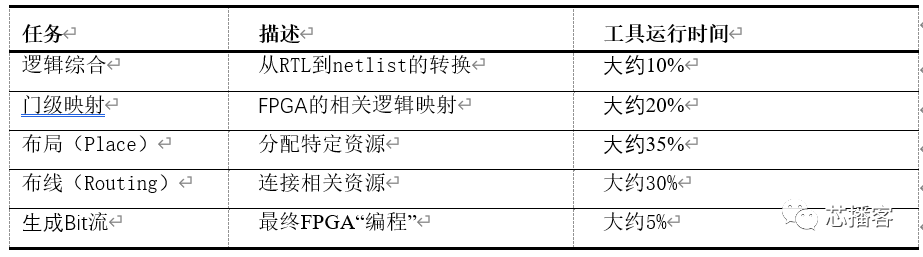

FPGA设计的五个主要任务:逻辑综合、门级映射、整体功能逻辑布局、逻辑资源互连布线,最后生成FPGA的bit流,根据常用的FPGA工具流程,这些任务将可以由不同的工具执行,每个步骤的运行时间比例将有所不同,如下图所示。例如,传统的布局布线流任务都由FPGA供应商提供的软件执行,相对应的布局布线工具,因此运行时间主要在布局布线阶段。

随着SoC设计变得更大,需要的FPGA资源也越来越多,时间也会变得更长。例如,大型FPGA芯片如果达到90%利用率,可能需要24小时或更长时间才能完成整个流程;

四分之三的时间都花在布局布线阶段。在进行原型设计时,这种长运行时间可能是一个巨大的代价,EDA工具永远在Shift Left的道路上狂飙就是这个原理,可以帮助客户节省时间是EDA的宗旨。

言归正状,从长远来看,使用四个FPGA50%利用率的FPGA原型比使用两个75%利用率的FPGA平台要划算,因为节省的迭代时间是非常宝贵的。虽然不是很等价,但由于跨FPGA的资源浪费,所以4片50%利用率也仅仅是估算,读者不必认真推算。

期望FPGA设计迭代一轮的时间,也就是整个编译加运行时间为数小时而不是数天,这样我们就可以更加多次进行重大的bug的修复,并在一天内看到修复的结果在FPGA原型平台上呈现。事实上,笔者经历过的团队,都习惯于在白天进行bug的修复和RTL的更改,然后在下班后的夜间运行,并在第二天早上上班第一时间看到新的结果,人可以休息,机器绝对不可休息。因此,在这个过程中自动化脚本显得尤为重要。

项目执行过程中,只要我们认真执行,并在最后得到正常运行的FPGA状态,并且取得了进展,那么长运行时间是可以接受的。最不能忍受的是一些工程师由于粗心的错误,使我们的结果变得无用时,运行时间又特别长,这就非常恼火。

如果整个系统运行时间很长,不允许这样的迭代周期,那么建议采取一些步骤来取得更好的效果:

1. 添加更多高性能的工作站和FPGA相关软件License:这允许更大的并行处理和运行时任务的平衡。

2. 更低的FPGA资源利用率:将设计重新划分为更多的FPGA。分割可能需要一些时间,多的FPGA可能需要一些投资,但这是一项值得投资的投资。总运行时间可以根据设备的使用水平而变化很大,节省大量运行时间,从而更快的shift left。

3. 放松约束:在设计的不太关键的部分,可以降低时序目标,以减少工具运行时间。布局布线运行时间不仅取决于利用率,其他因素可能会产生更大的影响,包括时序约束、全局时钟数量以及驱动BRAM的时钟数量。基本上,布局布线任务越复杂,运行时间越长。

4. 使用增量编译:一般而言,FPGA综合布局布线都有内置的增量编译选项,执行过程中一定选上这个option,通过不重新处理设计中未更改的部分来减少运行时间。

5. 使用快速流程:一些工具可以选择关闭某些优化步骤,但代价是降低结果质量。

审核编辑:刘清

-

基于FPGA的光栅尺位置速度反馈模块设计2010-04-24 0

-

低通滤波器的FPGA设计及仿真2013-04-04 0

-

设计分析:树莓派的多串口服务器软件设计中3个主要任务2020-05-20 0

-

请问uClinux Bootloader的主要任务有哪些?2021-04-26 0

-

嵌入式系统设计的主要任务是什么2021-11-09 0

-

采用FPGA来实现SVPWM调制算法2022-01-20 0

-

区块链是欧洲证券2018年的主要任务2018-02-09 1004

-

浅谈电子信息领域的五个主要任务和五点要求2018-04-24 4160

-

数据链路层的任务2019-02-27 6903

-

产品架构师的主要任务有哪些2019-04-23 3755

-

5G资料:单站验证的主要任务(NAS组网)资料下载2021-03-29 662

-

功率放大器的主要任务2023-02-27 411

-

变配电的主要任务 变配电的五防是什么2023-04-04 1582

-

处理FPGA原型设计需要多长时间?2023-05-23 483

-

功率放大器的主要任务是什么2024-01-03 242

全部0条评论

快来发表一下你的评论吧 !