DCDC芯片自举电容原理详解

电源/新能源

描述

1、DCDC芯片自举电容

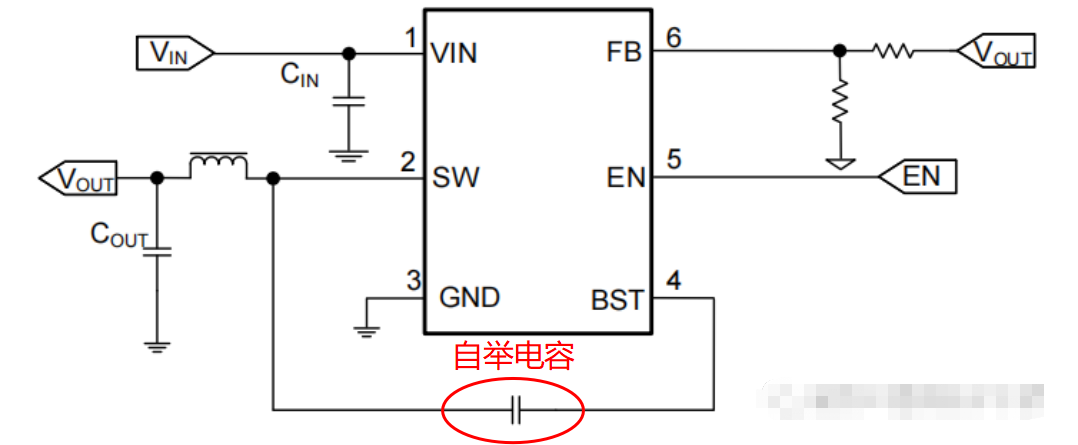

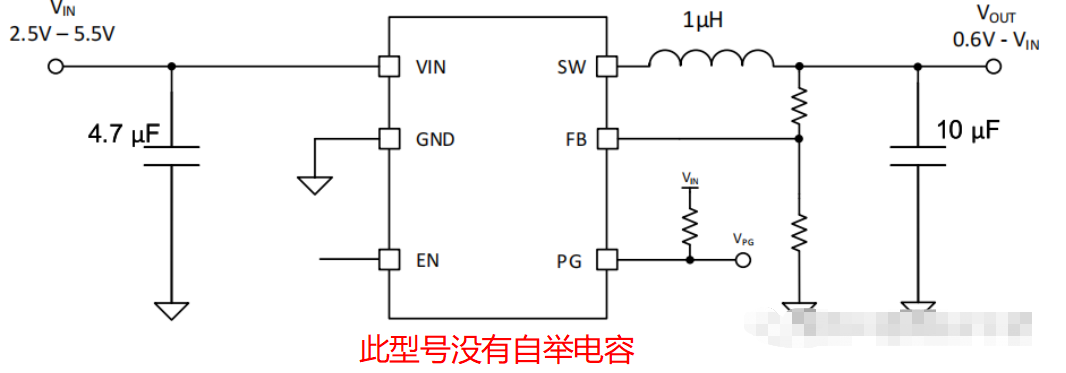

我们经常见到部分型号DCDC芯片电路有这种自举电容,而有些DCDC芯片却没有这个电容,如下面两款DCDC。很多人不知道这个自举电容有什么作用,虽然按照厂商的推荐电路设计也没有什么问题,但是不懂电路细节确实不妥。

型号:TPS563203,有自举电容。

型号:TPS62A01,没有自举电容。

2、两款芯片的结构框图:

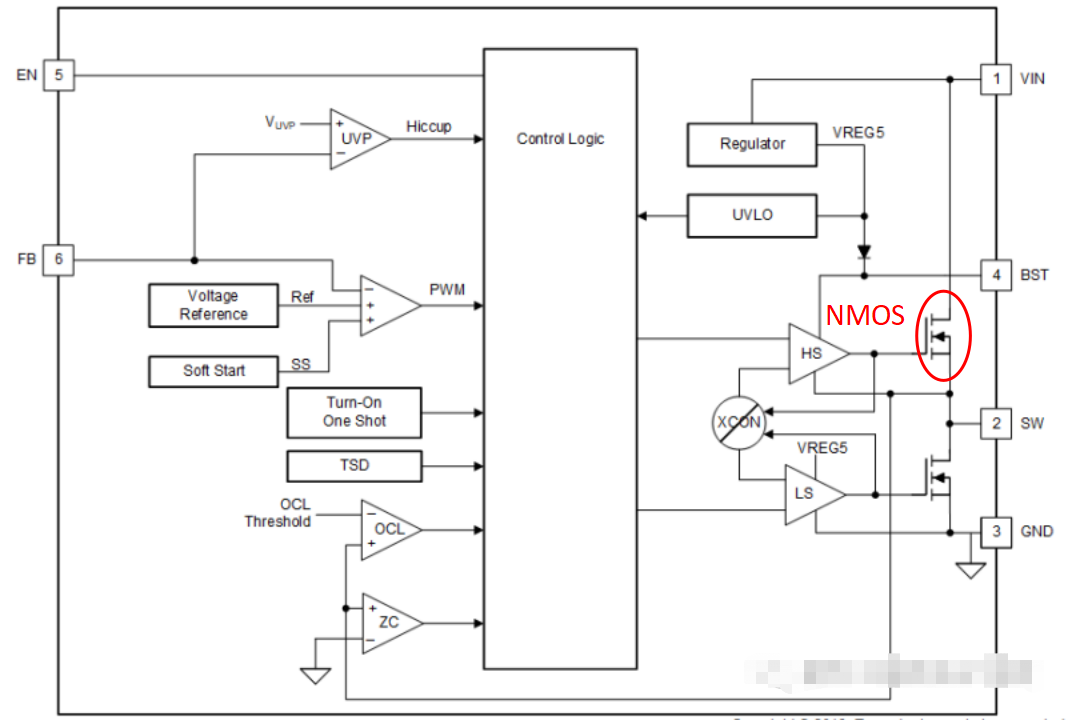

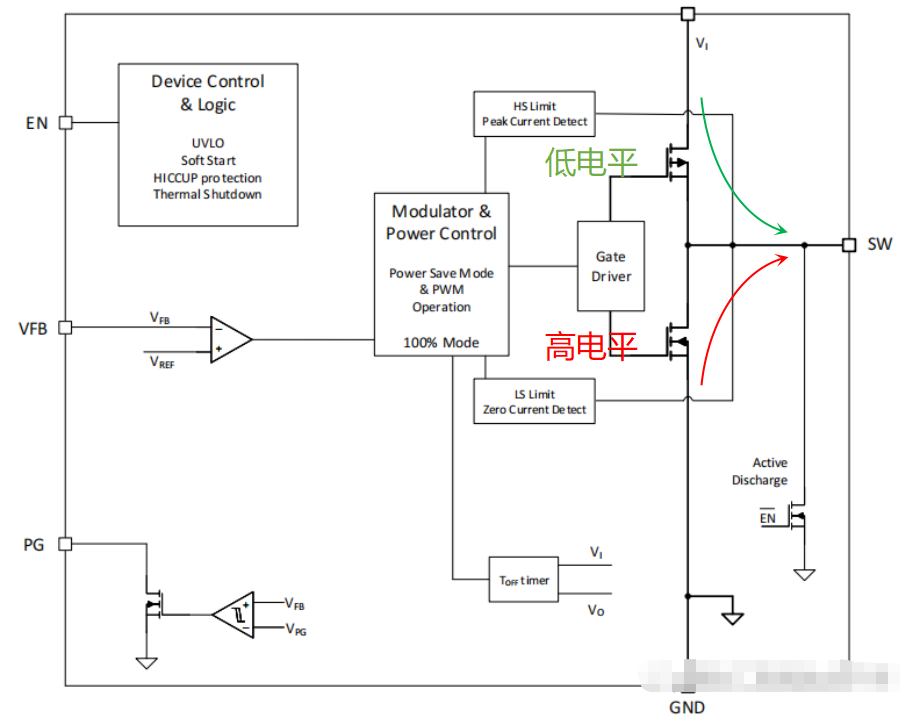

TPS563203结构框图如下,此款芯片上管为NMOS。

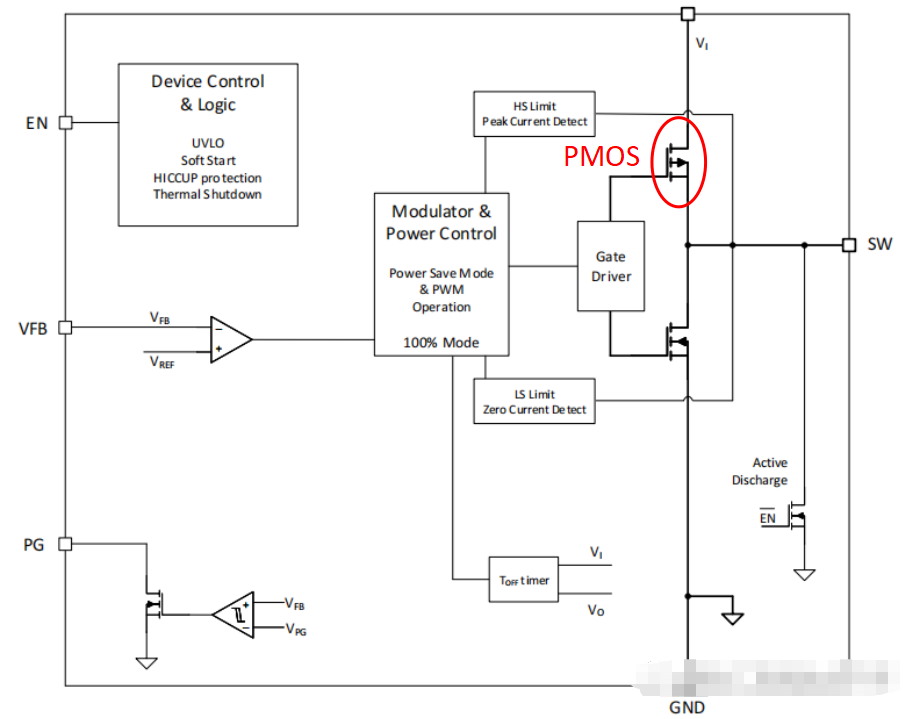

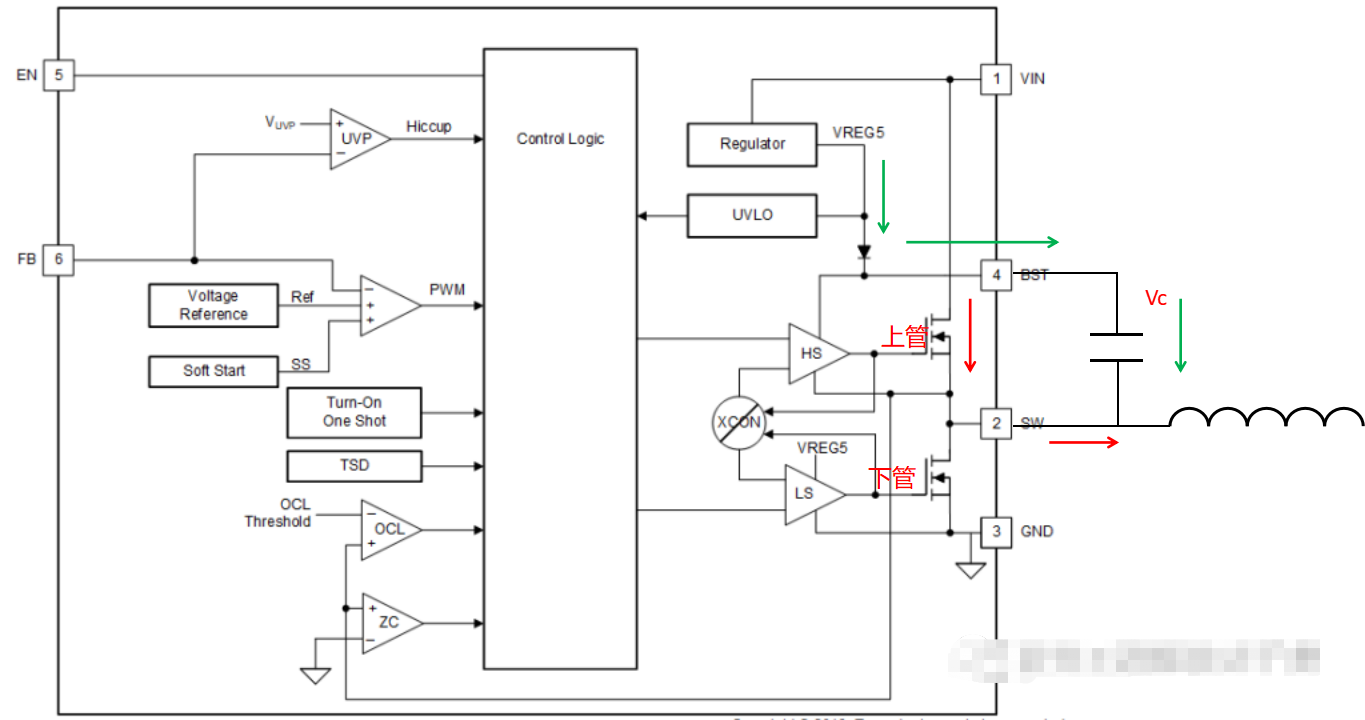

TPS62A01结构框图如下,此款芯片上管为PMOS。

3、驱动方式

1)TPS62A01驱动方式:

这种类型的芯片驱动方式好理解,驱动电路输出高电平,下管的Vgs大于开启电压,开始导通。同样道理驱动电路输出低电平,上管导通,下管截止。PMOS和NMOS交互导通。

2)TPS563203驱动方式:

以上芯片框图中可以看出,此芯片上管使用NMOS,因为上管的源极不是接地设计,所以上管导通后,源极电压比较高,几乎就是Vin,所以要想上管持续导通,至少使栅极电压比源极电压高一个MOS管开启电压,也就是至少比Vin高一个开启电压,这就用到了电容自举。当上管截止,下管导通,此时SW管脚被下管强行拉到GND,自举电容通过二极管充电,电压充至Vc,如上图绿色箭头所示。当上管导通,下管截止时,SW管脚不为0,假设为Vsw,此时电容的上端电压为Vsw+Vc,下端是Vsw。但是电容两端电压差仍然是Vc,理由是电容两端电压不能突变。这个自举电容跨在上管的源极和栅极之间,也就是说栅极和源极之间的电压差为Vc,这个电压差就是为了保证上管的Vgs大于开启电压,使上管能正常开启。自举电容的作用就是抬高上管的栅极电压。

4、题外话

上管使用NMOS增加了一些芯片设计复杂度。为什么有的DCDC中的上管仍然使用NMOS?上篇文章介绍了PMOS的导通电阻比较大,流过相同电流压降较大,发热量大,效率低,因此在大功率DCDC中上管一般使用NMOS,小功率DCDC使用PMOS设计简单,成本低。

-

southgnss

2023-04-13

0 回复 举报好文章,学到了 收起回复

southgnss

2023-04-13

0 回复 举报好文章,学到了 收起回复

-

什么是自举电容?自举电容的额定电压如何选?2021-03-11 0

-

自举电容的相关资料分享2021-11-12 0

-

自举电容的作用及原理2021-11-16 0

-

什么是自举电容_自举电容的作用是什么2017-11-06 74402

-

电容自举电路电路图大全(六款电容自举电路设计原理图详解)2018-03-01 90703

-

BUCK电源芯片中自举电容的说明2021-11-07 920

-

DC/DC电路自举电容作用2021-11-09 1822

-

详解自举电容的工作原理2022-04-09 8397

-

详解用于MOS管驱动的电容自举电路工作原理以及器件选型2022-04-12 31170

-

什么是自举电容?自举电容在buck芯片上的典型应用2023-10-25 983

-

DCDC芯片中的自举电容是什么2023-11-20 273

-

电路中的自举电容分析2023-11-20 672

-

异步DCDC中的自举电容2023-11-20 263

-

自举电容是如何实现充电的呢2023-12-12 446

全部0条评论

快来发表一下你的评论吧 !