聊聊PCIe Bus总线

电子说

描述

今天这篇文章,我们来聊聊PCIe Bus(PCIe总线)。 Bus在国内被理解成汽车,在国内还有一种解释是总线的意思。其实这两种翻译还是有共通之处。以我们生活中例子来说,Bus是两个城市中沟通的重要连通方式,而总线则是计算机之间联通的重要方式。 我们想从天津去北京办点事,那么可以乘坐长途大巴,电脑则需要通过PCIe的Bus。简单来说,Bus总线是多个硬件之间的一条通信公路。

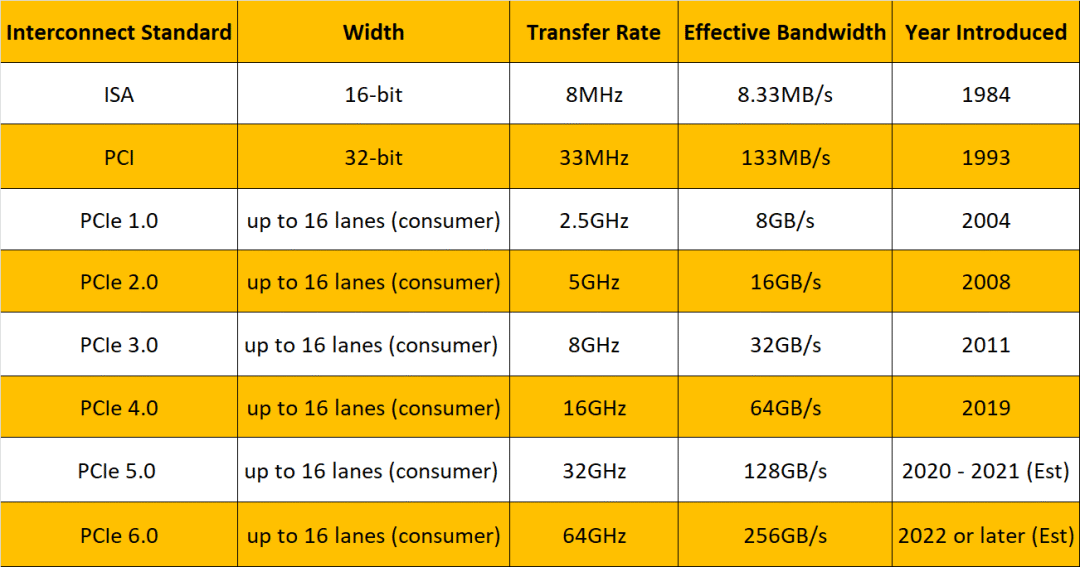

与公路相对应的是,PCIe也有不同的规范,就像高速一样,不同的道路也有不同的限速,比如国道和高速,宽度和最高行驶速度都不同。这个就对应着PCIe1.0、PCIe2.0、PCIe3.0、PCIe4.0这些规范。

但即使是同一条公务,行驶在不同的线路上也有不同的限速,这个就是跟PCIe1.0不同扩展槽的性能类似,例如PCIE x16/x8/x4/x1四种扩展方式能够支持的最大传输速度也是不一样的。 可以说,PCIe总线是计算机设备树的重要组成部分,几乎所有外围硬件的扩展都需要PCIe上,今天我们就来聊聊PCIe发展史。

01 挖挖PCIe的祖先们

在多年以前,计算机主板上不同的设备所使用的的总线接口是完全不一样的,硬盘有硬盘对应的总线接口,网卡有网卡对应的总线接口。 这样好处是每个设备都有对应的总线接口,优化性能简单。但对于个人来说,随着扩展设备的逐渐增多,如果都在主板上扩展对应的总线接口,有点得不偿失,同时造成了主板拓展的局限性,也对硬件规格的统一带来很多的不便。 为了解决这个瓶颈,IBM和Intel联手,在1981年第一代IBM PC XT机型上采用了第一代ISA插槽,作为现代PC的开山之作,当时8位的ISA提供了4.77MB/s的带宽(或传输率)。

由于兼容性好,一经推出,ISA总线就受到了各个厂商的欢迎,成为了上个世纪80年代最广泛使用的系统总线。但由于ISA使用的是并行总线,当时的抗干扰技术也不成熟,就导致ISA总线的带宽不能设计的很高,只能达到8MB/s的速率。 这个传输速度对于在90年代逐渐出现的像图像这种大数据传输需求来说还是有点"不够劲儿"。 除了速度慢这个缺点,还有就是ISA总线接口上的设备不能自动配置,无法即插即用。再加上IBM自作聪明在PS/2产品线上引入了MCA总线,迫使其他几家PC兼容机厂商联合起来捣鼓出来EISA。这些都导致了ISA总线最终被淘汰。 在1992年,Intel搞出了自己的杀招,提出PCI(Peripheral Component Interconnect)总线协议,并靠着自己在PC领域的强大影响力,召集了一堆小伙伴组成了名为 PCI-SIG (PCI Special Interest Group)(PCI 特殊兴趣组J)的企业联盟。从那以后这个组织就负责PCI总监的标准制定和推广。

不得不点赞下Intel这种先见之明,在90年代就开始建立自己的"朋友圈",相比于封闭的IBM,英特尔合作共赢的心态让PCI标准得到了广泛推广和使用。统一的标准也有利于外围设备制造商的创新,从那以后各种各样的PCI设备应运而生,丰富了PC的整个生态环境。 相比ISA总线,PCI总线带宽升级到了132MB/s,速度提升非常明显。再就是支持自动配置,即插即用。

但PCI总线也并不是完美的,PCI总线跟ISA总线都是使用了并行总线设计,所以传输速度也受到了影响。再就是PCI总线的带宽共享机制,在高负载下,其他设备可能会出现抢带宽的现象,也不支持热插拔。 于是为了解决PCI总线的缺陷,技术再一次进行了升级革新,2004年,Intel再一次带领小伙伴革了PCI的命也就是本篇文章要说的PCI Express(简称PCIe)总线了。如今计算机已经开始是第五代(gen5,5.0),而且在计算机中更是更为了不可或缺的存在。

如今,PCIe可以支持的设备非常多,常见的有显卡、固态硬盘(PCIe接口形式)、无线网卡、有线网卡、声卡、视频采集卡、PCIe转接M.2接口、PCIe转接USB接口、PCIe转接Tpye-C接口等。

02 PCIe的传输速度和宽度

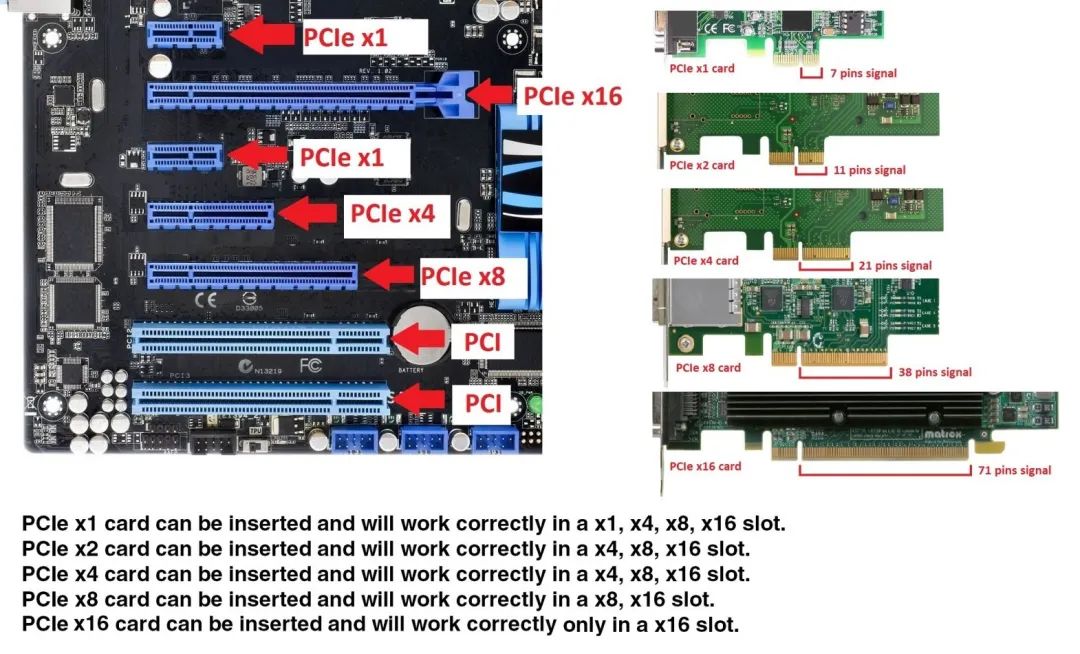

PCIe总线有两种存在形式,一种是接口、一种是通道。当PCIe以接口形式存在的时候,就是主板上横着的长槽。有人可能会问,这长槽有啥作用,为啥我的主板上的长槽长短不一呢?

这些长槽其实是PCIe不同的接口,常见的PCIe接口主要有四种尺寸,X1、X4、X8、X16,一般情况下四种尺寸的插槽最大带宽是不同的。它们的速度是不一样的,X16的PCIe速度就是X8的两倍,X8就是X4的两倍。当然,上面这段话都是建立在同一代PCIe总线之上的。

那么PCIe的吞吐量是怎么算出来的呢?首先我们来看下不同PCIe接口尺寸的计算公式:吞吐量=传输速率*编码方案*物理信道Lane 以PCIe4.0x4为例,该系列为4.0版本的PCIe,包含4个物理信道Lane,每个通道的吞吐量为: 16GT/s x 128b/130b =1.969GB/s 所以PCIe4.0x4的吞吐量为:1.969GB/s x 4 = 7.877GB/s,如果是PCIe4.0x16,吞吐量最大就是64GB/s。

除了吞吐量不同,不同的PCIe的尺寸的应用有啥不同呢?我们就来详细看下X1、X4、X8、X16的应用情况。

PCIe x16插槽:如上图所示,PCIe x16插槽全长89mm,有164根针脚,靠主板外侧端有一卡口,将16x分为前后两组,较短的插槽有22根针脚,这个是用于供电,每个尺寸的插槽都有这个22根针脚的供电设计。较长的插槽142根,主要用于数据传输,具有16通道所带来的高带宽。 目前来看,PCIe x16插槽,主要用于GPU显卡以及RAID阵列卡等,这个插槽拥有优良的兼容性,可以向下兼容x1/x4/x8级别的设备,而且具有更强的传输性能,可以说是PCIE x16插槽是PCIE的万能插槽。 由于PCIe x16插槽常用于显卡,与CPU处理器直接相通,在物理位置上直接靠近CPU,这样显卡与处理器之间的数据交换就可以减少延迟,让系统的性能可以得到充分的发挥。

PCIe x8插槽:全长56mm,有98根针脚,与PCIe x16比较,主要是数据针脚减少至76根,短的供电针脚仍然是22针脚。 为了兼容性,PCIe x8插槽通常加工成PCIE x16插槽的形式,但数据针脚只有一半是有效的,也就是说实际带宽只有真正的PCIE x16插槽的一半。可以观察主板布线,x8的后半段没有线路连接,甚至针脚也没有焊接。 实际上除了旗舰级或服务器的主板,能提供多条真正的PCIex16插槽外,大多数的主板,只会提供一条真正的PCIe x16插槽,就是最靠近CPU的那条。而第二条和第三条PCIe x16插槽,则多数是PCIe x8甚至是x4级别的。

PCIe x4插槽:长度为39mm,同样是在PCIE x16插槽的基础上,以减少数据针脚的方式实现,主要用于PCIe SSD固态硬盘,或者是通过PCIE转接卡安装的M.2 SSD固态硬盘。 PCIe x4插槽通常由主板芯片扩展而来,不过随着cpu内部PCIE通道数的增多,现在有部分高端主板可以开始提供直连cpu的PCIE x4插槽,用于安装PCIE SSD固态硬盘。 不过与PCIe x8插槽一样,PCIe x4插槽为了兼容性,现在多数也是做成PCIe x16插槽的形式,或是扩展为M.2接口,用于安装M.2 SSD、M.2无线网卡或者其它M.2接口设备,其余扩展卡则留给PCIE x1插槽负责。

PCIE x1插槽:长度仅有25mm,相比PCIE x16插槽,其数据针脚是大幅度减少至14个。PCIE x1插槽的带宽通常由主板芯片提供,主要用途是独立网卡、独立声卡、USB 3.0/3.1扩展卡等都会用到PCIE x1插槽,甚至可以通过转接线给PCIE x1插槽装上显卡,用来挖矿或者实现多屏输出。 X1的另外一个重要作用就是是用来替代原来的PCI设备的。

03 PCIe未来会怎样?

PCIe接口从2001年发展至今,在协议的完整性上已经建立足够高的"护城河",重新定义一个接口协议在性能上超越PCIe,短期内一方面没有企业会有这个动力,另一方面技术的维度,也没有可预期的雏形创新。 但"成"也Intel ,"阻碍"也在Intel。 我们都知道,Intel在CPU发展方面一直以"挤牙膏"著称,其实在PCIe方面,Intel挤牙膏那是更严重。 一般来说,规范确定到商品化需要1~2年的时间,就像摩尔定律估算的差不多,每过1~2年,其实产品就需要升级进化。 但是靠着英特尔靠着自己的垄断优势,在PCIe升级方面则是亦步亦趋。从2004年发布PCIe1.0以后,到2023年新一代服务器的发布,PCIe5.0才开始逐渐出现在主板上。 而且可以说,PCIe 5.0是PCIe发展的重要分水岭,这是因为人算不如天算,Intel没想到大数据AI、视觉渲染、基因分析以及EDR仿真等需求的突然爆发,让PCIe的数据传输已经赶不上GPU的需求。

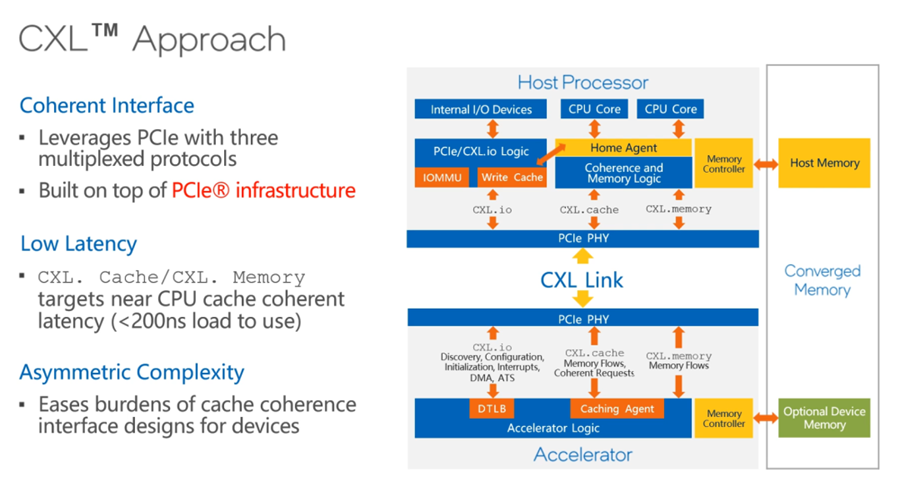

为了解决PCIe在数据传输的限制,早在几年前,市场上几种不同的传输和内存语义协议逐渐出现--IBM的OpenCAPI内存接口协议、Xilinx的CCIX协议、NVIDIA的NVLink协议、惠普企业版的Gen-Z协议,都是为了解决PCIe4.0传输过慢的问题。 眼看着大家都在革PCIe的"命",在2019年3月份Intel推出了CXL(Compute Express Link)协议接口,将CXL协议封装到PCIE链路层数据包中传送,并在CPU端的PCIE总控后端按照事务标识分流CXL专属事务给CXL处理逻辑处理。 Intel希望能够让CPU与GPU、FPGA或其他加速器之间实现高速高效的互联,从而满足高性能异构计算的要求。最值得注意的是CXL标准的接口规格与PCIe 5.0是兼容的,从而让CXL协议让PCIe5.0上可以运行,进一步巩固PCIe在计算机里的影响力。

Intel的策略是,既然CPU等需求趋势已经来袭,堵不如疏,不如把GPU、DPU等用作一把刀,来与NVIDIA形成某种制衡,如今,NVIDIA也加入了CXL联盟,对Intel来说,反正我建了通往内存的"高速路",你GPU怎么走都得听我的。

通过这种方式,也能进一步制衡GPU的发展,一颗CPU想支持几个GPU,还得通过Intel说了算。 值得注意的是,第四代英特尔至强可扩展处理器每一颗处理器支持最多4个CXL设备,支持CXL Type1和CXL Type2。)这些将提升服务器的综合能力,为内存密集型和IO密集型场景提供更高价值。

04 最后

2022年1月,PCI-SIG 组织今日正式发布了 PCIe 6.0 标准。作为CXL 3.0软件栈协议规范的物理连接承载平台,PCIe 6.0主要用于CPU与GPU(AI加速器)、CPU与DPU(智能万卡NIC)、以及CXL内存模块(可以理解为其他CPU DDR内存)的连接,对应的应用场景,如大内存、以及不同外设缓存之间的直接数据交换。 对于这些场景而言,PCIe 6.0接口子系统高达64GT/s的数据传输速率,对于异构计算架构的影响意义重大。

审核编辑:刘清

-

TSS721A,M-Bus,瑞盟MS726仪表总线收发电路2024-03-08 0

-

PCIE总线的FPGA设计方法2015-10-30 0

-

PCIE总线详细资料2016-02-15 0

-

PCIe总线的复位方式是什么?2019-10-16 0

-

PCIe总线和PCI总线有哪些不同之处呢2021-10-26 0

-

Bus/总线布线时如何做到等长2009-09-28 1592

-

令牌总线(Token Bus),令牌总线是什么意思2010-03-22 2746

-

PCIE总线基本资料2012-05-10 1260

-

CAN-bus现场总线基础方案_通信2017-02-07 934

-

PCIE总线的多DSP系统接口设计2017-10-31 910

-

在orcad中使用Bus总线时的注意事项2021-09-06 2403

-

聊聊PCIe Bus(PCIe总线)2023-04-13 3119

-

M-Bus总线概述、特点及工作原理2023-07-14 1560

-

什么是M-Bus总线协议?2023-07-31 736

全部0条评论

快来发表一下你的评论吧 !