信号完整性之反射(二)

描述

3 阻性负载的反射

传输线的终端匹配有三种特殊情况:开路、短路、终端阻抗和传输线阻抗匹配。

情况一:终端开路(假设传输线阻抗是50R)

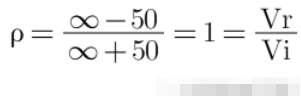

当传输线终端开路,则传输线模末端的瞬态阻抗是无群大,此时反射系数是:

即当信号到达传输线的终端时,在终端将产生与入射波大小相同,方向相反,返回源端的反射波。在终端看到的波形是入射波形的2倍(入射波形+反射波形)

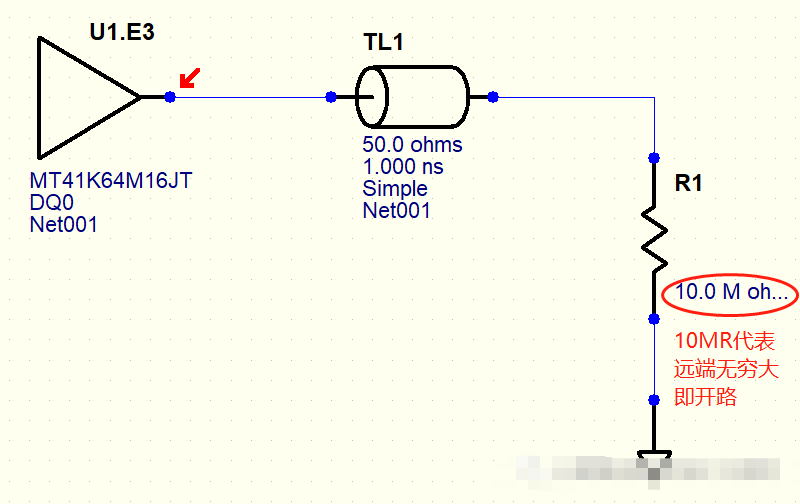

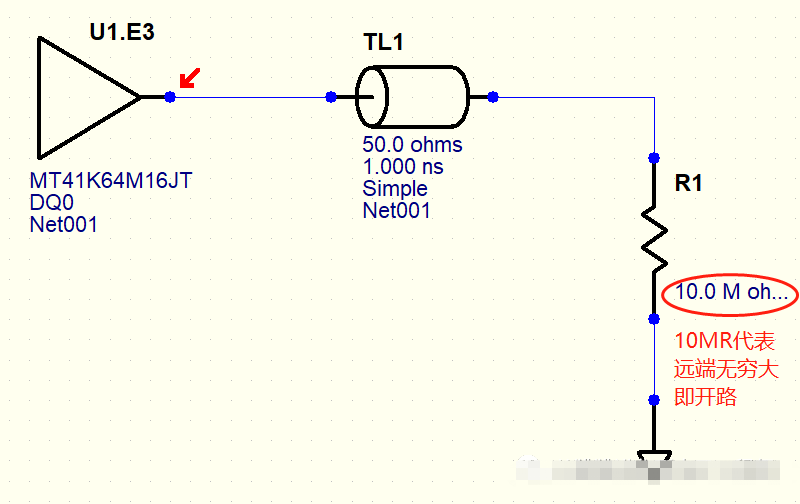

如下图是一个简单的仿真电路,R1赋值10MR,用来表示终端开路。本案例中LPDDR3的E3 pin(DQ0)是输出pin。

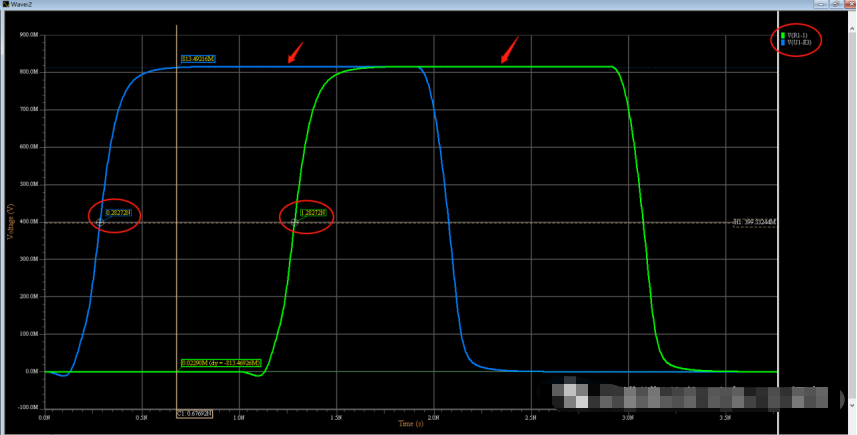

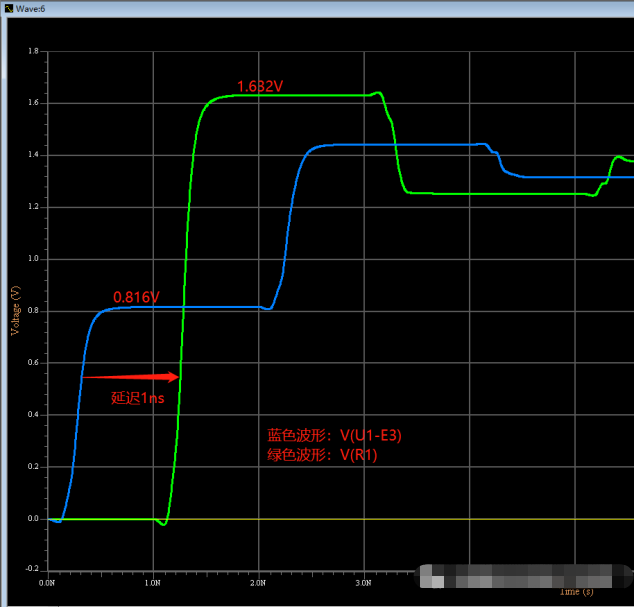

下图是仿真结果。蓝色是源端输出的波形,也被称为入射电压。绿色是终端的波形。就像上面计算的那样,入射电压是0.816V。同时因为终端开路,因此在终端会产生一个0.816V的反射电压,导致在终端看到的总电压是入射电压和反射电压之和(1.632V)。另外,因为设计传输线延迟在1ns,蓝色信号和绿色信号之间的延迟也差不多是1ns。

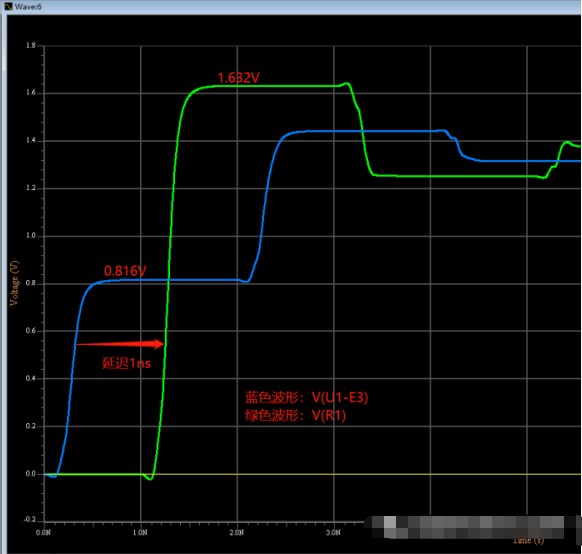

情况二:终端短路(假设传输线阻抗是50R)

当传输线终端短路,则传输线模末端的瞬态阻抗是0,此时反射系数是:

即1V入射信号到达远端时,将产生-1V反射信号,向源端传播。短路突变处的电压为入射电压和反射电压之和,即1V-(-1V)=0V。

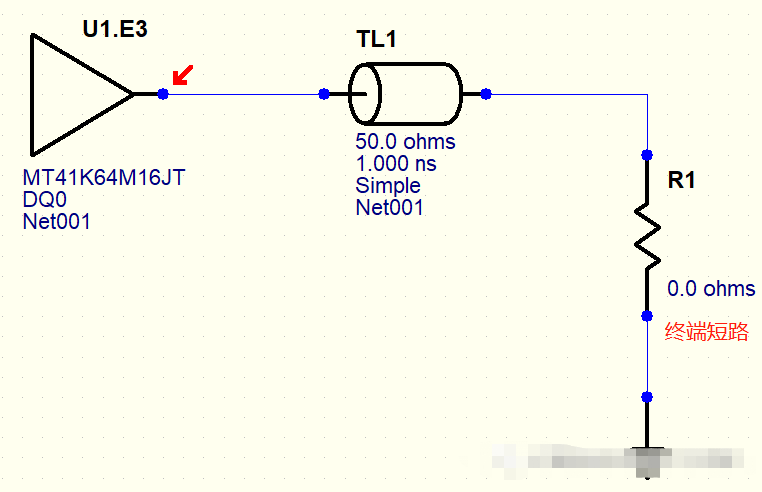

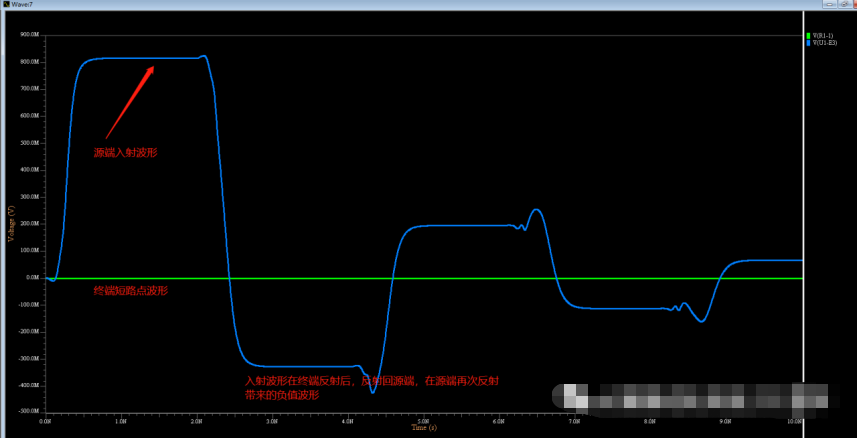

如下是终端短路的电路仿真,R1=0R,代表终端短路。

从仿真结果看:终端信号为0V,因为终端的信号端和返回平面端(地)是短路的。同时入射信号在终端阻抗短路处发生反射,反射波形回到源端,遇到源端内阻,再次被反射,产生一个负电压。

情况三:终端阻抗和传输线阻抗匹配

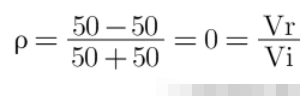

当终端阻抗和传输线阻抗匹配时,此时反射系数为:

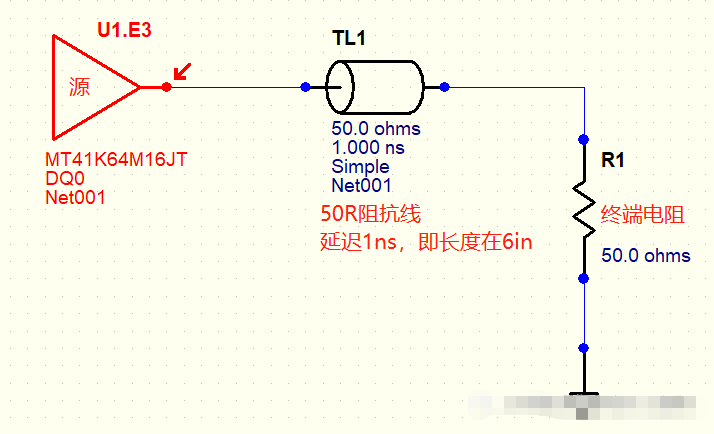

没有反射信号,终端电阻两端的电压就是入射信号。如下图是使用Hyperlynx做的简单仿真。U1是某个LPDDR3的DQ0,在本仿真中做输出。经过一段阻抗为50R的传输线(此段线带来的信号延迟是1ns),终端是一个50R的电阻。

通过仿真结果可以看到(1)终端电压和入射电压幅度一致,为813mV,没有反射。(2)入射电压和终端电阻电压有1ns的信号延迟。

总之:当末端为一般性阻性负载时,信号在终端感受到的瞬态阻抗在0~无群大之间,反射系数在1~-1之间。

4 驱动源的内阻

驱动源总是存在内阻。典型的CMOS器件,内阻大约在5R~20R之间。内阻对进入传输线的初始电压和后来的多次反射电压都有影响。例如当反射波最终到达源端时,会将源端的输出阻抗(内阻)作为瞬态阻抗,此阻抗决定反射波再次反射回负载端的情况。

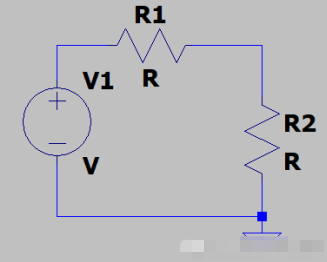

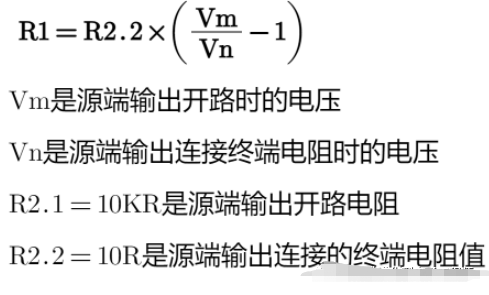

怎么知道源端的内阻是多大呢?假设V1是信号源,R1是信号源内阻,R2是外部负载。

通过SPICE或者IBIS模型可以计算得到R1的值。分别仿真R2=10KR和R2=10R时的输出电压。

例如某芯片的一根信号源,进行仿真。当连接R2.1时,Vm=3.3V。当连接R2.2时,Vn=1.9V。由上述公式计算得知R1=7.3R。

5 反弹图

因为内阻的存在,初始进入传输线的信号是源内阻和传输线特性阻抗的分压。当分压后的信号到达负载端,如果负载端阻抗不匹配,有部分信号被反射回源端。这些反射回源端的信号到达源端后,会再次被反射,叠加在原始信号上又被传到负载端,而后再次被反射。就这样循环下去。

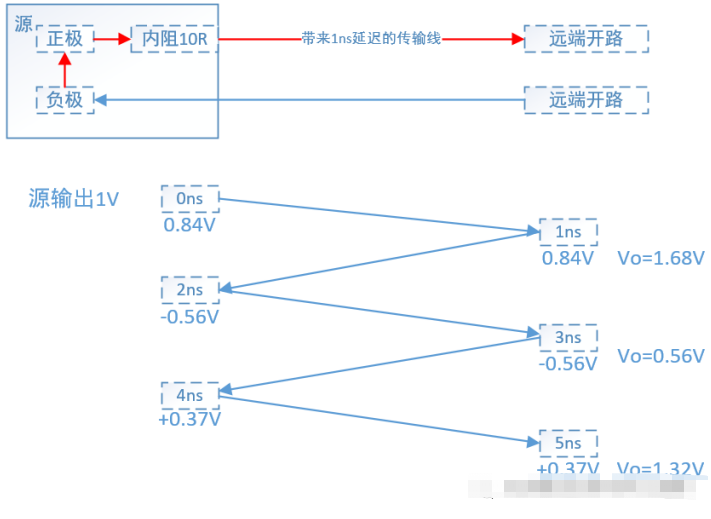

举例,假设源端输出电压是1V,源内阻是10R,传输线阻抗是50R,考虑负载端是开路的极端情况,步骤分析如下

(1)刚开始,有1Vx50/(10+50)=0.84V的电压进入50R传输线。这个0.84V就是沿传输线传播的初始入射电压。

(2)1ns时间到,0.84V的电压到达负载端,之前已经说过假设负载端是开路的。此时反射系数是1,反射电压=入射电压=0.84V。即有0.84V的反射电压开始向这源端反射回去。此时在负载端(开路端)测得总电压为0.84V+0.84V=1.68V

(3)又过了1ns,被反射回来的0.84V反射波回到源端,在源端遇到阻抗匹配,再次被反射。此时源端的反射系数是(10-50)/(10+50)=-0.67,即此时由被负载端反射回源端的0.84V在源端再次反射的电压是0.84Vx(-0.67)=-0.56V。这个-0.56V被传回负载端。

(4)又过了1ns,此时已经是第3ns了,-0.56V的波到达负载端,并且又被反射回源端。同时在负载端测试到由此-0.56V产生的波是(-0.56v)+(-0.56v)=-1.12V。此时的-1.12V叠加上之前的1.68V,第3ns时在开路端测量到的波形是1.68V-1.12V=0.56V。

(5)再过1ns,即第4ns时,反射波(-0.56V)回到源端,产生的反射电压是+0.37V。

(6)再过1ns,+0.37V的源端反射电压到达负载端,产生负载端新的反射电压+0.37V。此时已经是第5ns,此时负载端的总电压是0.56V+0.37+0.37V=1.3V。

(7)如此继续循环反射下去。

(8)最终输出端电压会趋向于源端电压1V,毕竟终端最终是开路的。

当源内阻小于传输线的特性阻抗时,源端出现负反射,这会引起振铃现象。在此过程中,部分时间点的输出开路电压大于源电压。多出来的电压是由于传输线的寄生电感和寄生电容谐振产生的。

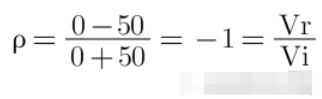

如下图是一个仿真电路来模拟终端开路时的反射过程。本案例中LPDDR3的E3 pin(DQ0)是输出pin。

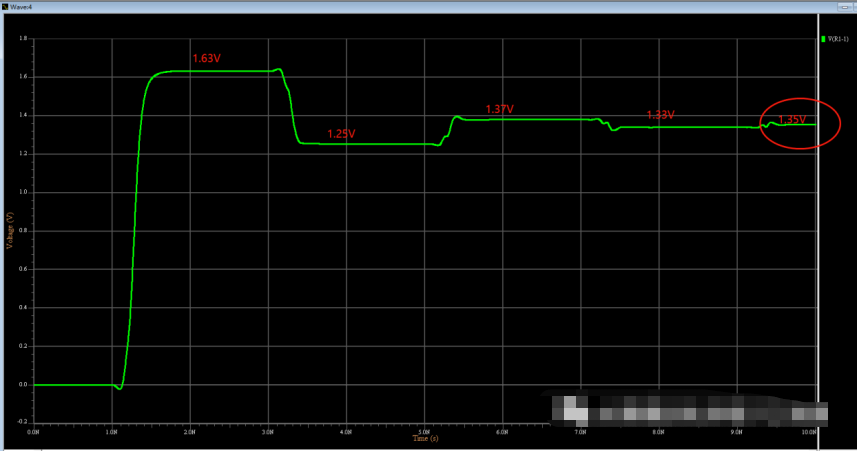

(一)下图中绿色波形是终端电阻上的波形。结果显示有振铃,电压幅度按照上述步骤所述的随着时间在变化(注:本仿真案例中的LPDDR3的信号入射电压和上述步骤中案例的信号入射电压不同,内阻也不同,因此在电压上没有一一对应关系,此处只是表示每一步的趋势是一致的)。当然因为远端是开路的,随着时间的推移,最终远端的电压值会和源端电压一致。因为仿真选择的MT41K64M16JT是LPDDR3,1.35V供电。因此其输出的Data是1.35V。

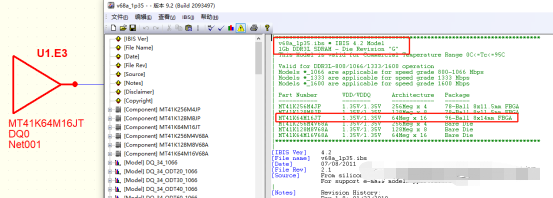

下图是MT41K64M16JT的IBIS模型,显示为1.35V的IO口电压。

(二)下图表示源端发出信号(入射电压),在1ns之后到远端的情况。和上述步骤(1)(2)对应。下图我只截取前面几个纳秒的波形。有兴趣的人可以试着自己做个仿真,得到完整的仿真波形。结合上述的反射图步骤,看看源端和终端波形在每一步是什么幅度,怎么计算出来的。

全部0条评论

快来发表一下你的评论吧 !