单板上以太网硬件设计框架

描述

一 关于这篇文章

如果没有接触过以太网相关硬件设计的话,也许会好奇,RJ45网口到控制器内部的物理通路是什么样的,我的这系列文章希望能够帮助到需要的人。内容初步规划为三个部分:以太网硬件设计需要知道的基础知识、以太网硬件设计细节、以太网测试,这篇是关于是以太网硬件设计需要知道的基础知识,能够对单板上以太网硬件设计的框架有个系统性认识。

二 单板上以太网硬件设计框架

2.1 以太网协议的基本构成

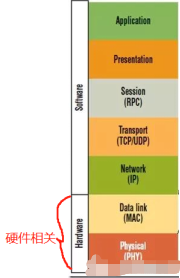

由于以太网的接口形态、信号的传输媒介和标准非常多(在IEEE 802.3中定义),这里只介绍最熟悉的,我们生活中最常见的以铜质双绞线为媒介的10Base-T、100Base-TX、1000Base-T网络,也就是我们常说的十兆、百兆、千兆网络(单位兆是Mbps,Million bits per second),这三者可以在同一硬件架构上自动兼容,取决于PHY芯片的支持。标准以太网的整个通信链路被分为7层(许多协议复用以太网硬件架构,将以太网上层软件协议进行扩展和修改,譬如EtherNET、GigE Vision、PROFINET等协议),与硬件设计相关的仅仅是数据链路层(MAC)、物理层(PHY)。

图 1 开放式系统互联通信参考模型(此图来自网络)

2.2 以太网的硬件部分的基本构成

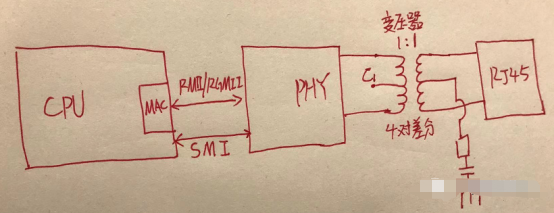

以太网协议与硬件相关的2层中,主控制器的接口为MAC,MAC口连接的外围芯片PHY(有些主控内部集成了PHY,外部直接连网络变压器即可),MAC和PHY通信的接口有很多种(其实大同小异),用得最多的有RMII(最大支持百兆带宽,MCU用得比较多)和RGMII(最大支持千兆带宽,高性能平台芯片用得比较多),其中SMI接口为PHY的寄存器配置引脚(MDIO,MDC),CPU可以通过该接口对PHY进行寄存器配置以及状态的读取。硬件的框图如下:

图 2 硬件框架简图

从框图可以看到,电路并不复杂,CPU通过MAC的高速数字接口RMII/RGMII与PHY进行交互,PHY作为物理层,起到将CPU发送过来的网络数据编码成差分信号给到外部网络接口MDI,同样的,本机的PHY将与RJ45连接的另一头的PHY发送过来的差分信号转换为RGMII信号发送给CPU。图中变压器原边中心抽头C1的连接方式取决于PHY的类型,电流型PHY,C1连接电源,电压型PHY,C1连接电容到信号地,PHY芯片的Datasheet中会有说明。

PHY的主要作用:

以太网底层协议的处理,包括自协商、link状态、网线自动翻转、冲突检测等等,这些信息同步体现在寄存器中,可以通过SMI接口进行读或写。

RMII/RGMII数据的编解码工作,在不同的带宽下编解码不一样,1000BASE-T是4D-PAM编码(5电平),100BASE-TX是MLT-3编码(3电平),10BASE-T是曼彻斯特编码。

在10/100兆网中,RJ45的1、2为TX,3、6为RX,现在的PHY芯片基本都支持自动MDI/MDI-X技术,TX和RX无需考虑交叉(如果不放心可以在PHY的datasheet中搜索“Automatic MDI/MDIX”,不支持可以使用交叉网线,参考《网线T568A与T568B(交叉网线)》)。1000兆网的使用8根线,采用混合调制技术(后续专门写一篇文章讲这个),4对差分线可以同时进行收发。

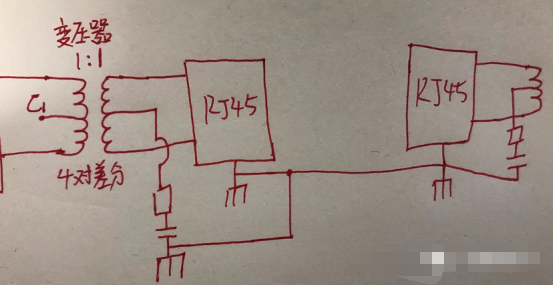

变压器次级线圈的中心抽头通过阻容连接到机壳地,电阻一般取值75Ω,电容一般取值1nF/2KV,主要作用是提供共模噪声通路和滤波(变压器内部还有共模滤波电感,图中没有画出),如果网线是带屏蔽的,屏蔽线连接机壳地(最好是围绕信号线360°端接的方式),从而提供一个共模信号回流路径,效果会更好。如下图:

如果没有屏蔽线,则两设备通过电容或者远端地线提供共模回路,从而共模信号的环路较大,工模信号的辐射也会较大。

图中电路没有保护电路,一般在变压器的初级(靠近PHY芯片一侧)放置ESD阵列即可,由于是高速信号,ESD的结电容原则上不超过1pF,如果在工作环境比较恶劣的场景,需要选用功率更高的管子,结电容可适当增加,原则上不超过2pF,次级也需要增加保护器件,具体情况具体分析。

-

EtherCAT实时以太网分析仪直击痛点#以太网ZLG致远电子 2022-12-12

-

EtherCAT实时以太网分析仪应用场景#以太网ZLG致远电子 2022-12-12

-

EtherCAT实时以太网分析仪功能详解#以太网ZLG致远电子 2022-12-12

-

以太网是什么鬼?以太网基础知识详解电子学习 2023-02-07

-

「无线工程师基础知识」以太网是什么鬼?以太网的使用注意事项电子学习 2023-02-08

-

车载以太网快速入门#车载以太网北汇信息POLELINK 2023-09-01

-

车载以太网测试系统测试实例介绍#车载以太网北汇信息POLELINK 2023-09-12

-

车载以太网基础培训——车载以太网的链路层#车载以太网北汇信息POLELINK 2023-09-19

-

车载以太网基础培训——网络层#车载以太网北汇信息POLELINK 2023-09-20

-

车载以太网总线基础培训——传输层#车载以太网北汇信息POLELINK 2023-09-21

-

车载以太网基础视频——应用层#车载以太网北汇信息POLELINK 2023-09-22

-

以太网和工业以太网的不同2018-10-23 0

-

以太网控制器(MAC)的基本框架怎么搭建2018-12-28 0

-

哪里可以做硬件故障单板的整改,USB2./USB3.0/以太网/MIPI/电源2019-11-15 0

-

光网络以太网单板特性介绍2012-02-08 494

全部0条评论

快来发表一下你的评论吧 !