基于Verilog的分数分频电路设计

描述

上一篇文章时钟分频系列——偶数分频/奇数分频/分数分频,IC君介绍了各种分频器的设计原理,其中分数分频器较为复杂,这一篇文章IC君再跟大家聊聊分数分频的具体设计实现。

一个分数分频器由两部分组成:以ZN和ZN+1为分频系数的多路分频器,还有一个ACC计数器。

1ZN/ZN+1分频器设计

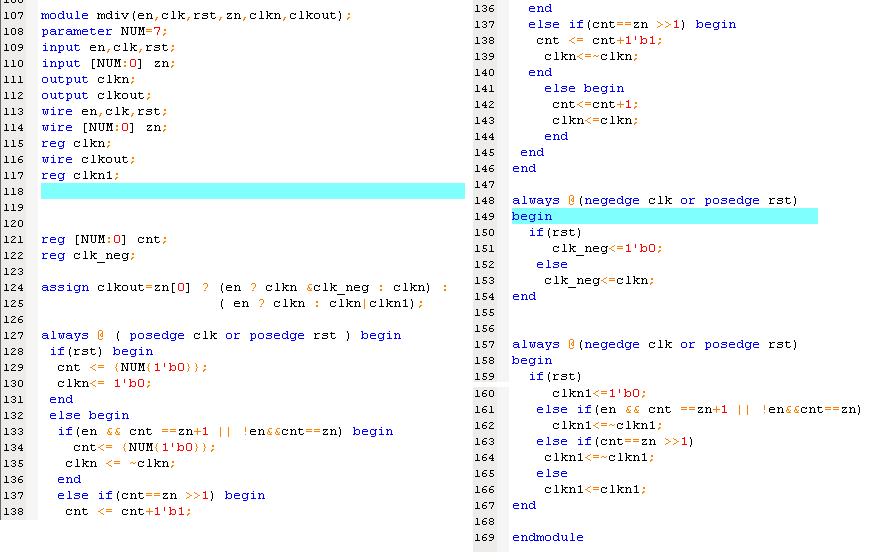

ZN/ZN+1分频器的设计包含了偶分频器和奇分频器,首先定义ZN/ZN+1分频器的模块名字MDIV。 下图是MDIV的引脚信号的名字,及功能定义:

废话不多说,Verilog硬件描述语言实现MDIV的代码如下:

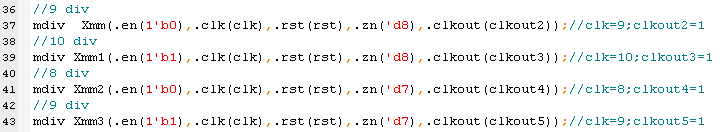

MDIV调用方法如下:

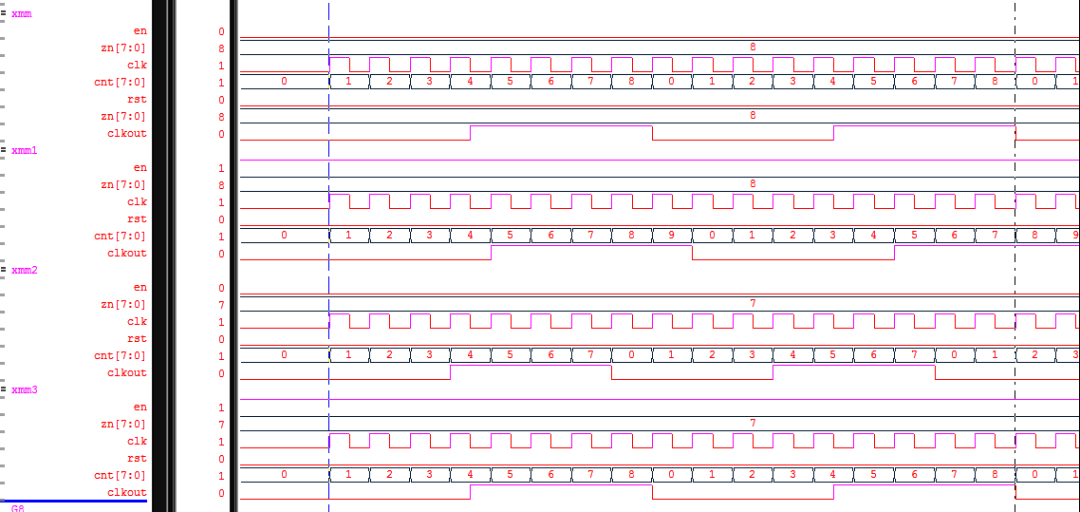

具体的仿真波形如下所示:

2ACC计数器设计

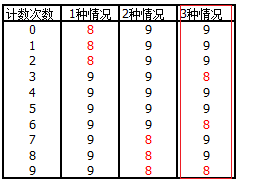

ACC计数器就是控制做N次ZN分频和M次ZN+1次分频,具体控制过程可以分为以下几种情况:

第1种情况 :先做N次ZN分频,再做M次ZN+1次分频;

第2种情况: 先做M次ZN+1次分频,再做N次ZN分频;

第3种情况 :把N次ZN分频平均插入到M次ZN+1分频中;

第4种情况 :把M次ZN+1次分频平均插入到N次ZN分频中。

组合N次ZN分频和M次ZN+1次分频的情况很多。 第1、2种情况前后时钟频率不太均匀,因此相位抖动比较大;

第3、4种情况前后时钟频率均匀性稍好,因此相位抖动会减小。

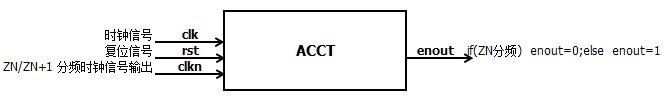

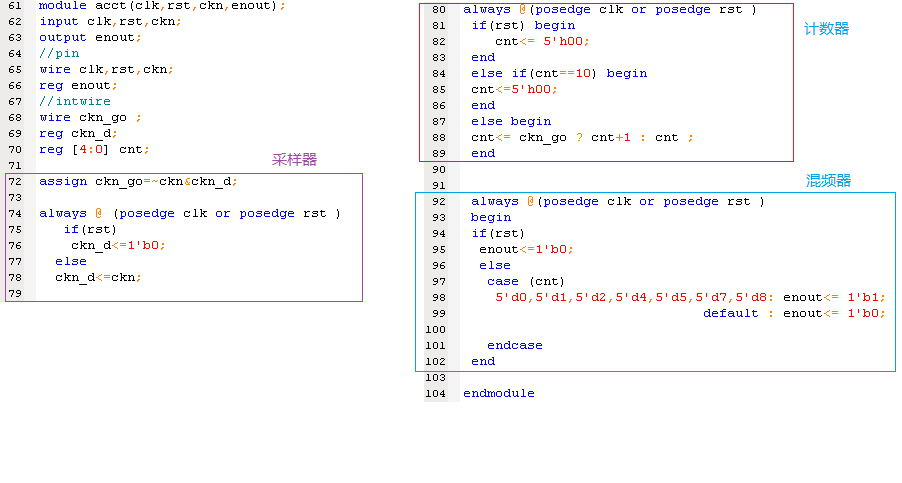

下面以8.7分频为例子设计ACC计数器模块名ACCT,下图为模块ACCT的引脚:

8.7分频的原理是用3次8分频和7次9分频的对应的时钟总时间来等效原时钟87个周期的总时间。

下图选用前面所述的第3种情况,把3次8分频平均地插入到7次9分频中,这个过程也叫混频。

采用第3种情况设计ACCT的Verilog代码代码如下所示:

代码的92-102行就是第3种情况混频,修改98行的数字可以得到不同的混频。

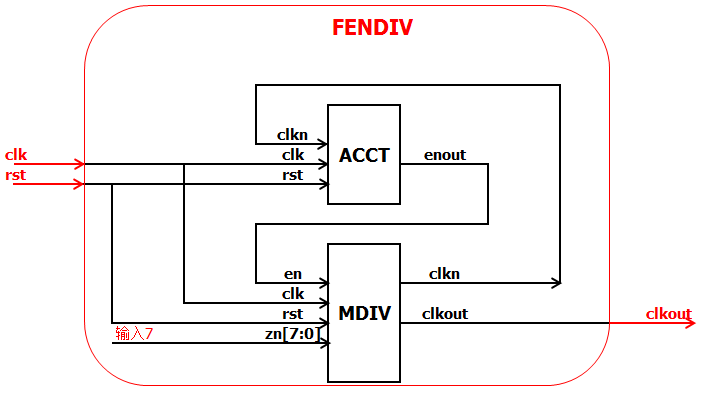

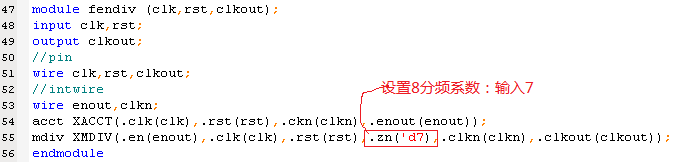

38.7分频器设计

完成了模块MDIV 和ACCT之后,就可以用组成一个8.7分频器,这个分频器的模块名是FENDIV,框图如下所示:

Verilog代码如下:

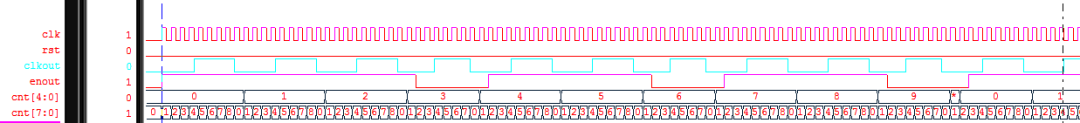

最终生成的clkout波形如下所示:

有兴趣的可以试试用MDIV 和ACCT设计一个10.3分频器?

-

基于FPGA 的等占空比任意整数分频器的设计2010-02-22 584

-

基于Verilog的FPGA分频设计2011-11-09 1158

-

FPGA实现小数分频器2011-11-29 747

-

用Verilog实现基于FPGA的通用分频器的设计2016-07-14 1008

-

此通用电路可以实现任意奇数分频电路2017-02-09 2589

-

分频器的作用是什么 半整数分频器原理图分析2019-02-01 15859

-

如何使用FPGA进行任意小数分频器的设计2019-08-02 2245

-

时序至关重要:改善分数分频锁相环合成器中的整数边界杂散状况2022-11-04 262

-

偶数分频器的设计2023-03-23 1022

-

奇数分频器的设计2023-03-23 735

-

小数分频器的设计2023-03-23 720

-

偶数分频、奇数分频、半整数分频和小数分频详解2023-03-29 3344

-

偶数分频/奇数分频/分数分频详解2023-04-25 6051

-

分频器之小数分频设计2023-06-05 1080

-

锁相环整数分频和小数分频的区别是什么?2024-01-31 608

全部0条评论

快来发表一下你的评论吧 !