译码器、多路选择器介绍

电子说

描述

想不出来什么无敌炫酷的开头。我们就直接来吧;

- 1对译码器的原理叙述;

- 2关于38译码器的撰写、N位译码器的撰写;

- 3对应测试文本的撰写;

1.1译码器

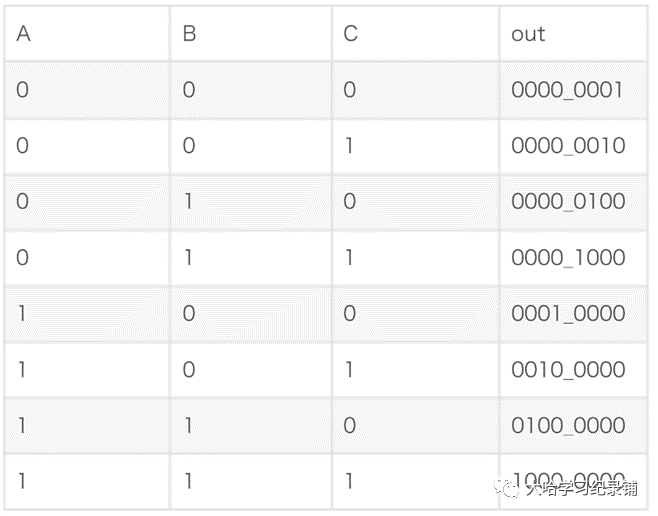

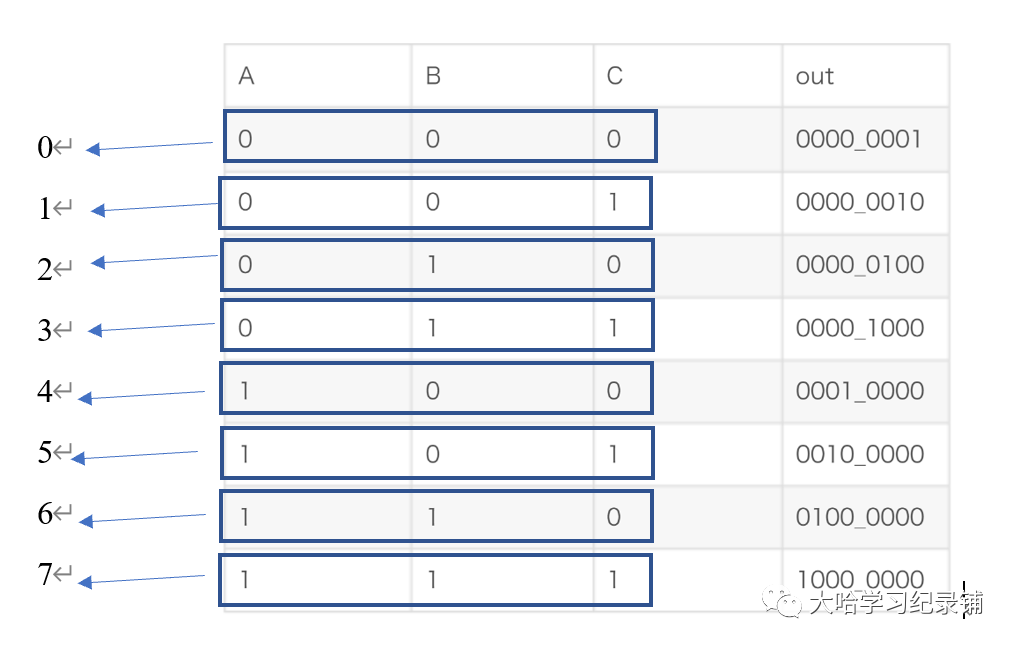

译码器就是将每种⼆进制的组合代码译成对应的输出线上的⾼低电平信号。用如下表格可以直观的了解:

其中ABC就是对应了我们的输入端口;

三个端口组合起来就是三位二进制0-7;

当ABC的值为0时,我们将八位输出的最低位置1;

当ABC的值为1时,我们将八位输出的次低位置1;

如此便实现了译码器的功能,即输入端逻辑值为多少,我们就置高输入端哪一位为高电平(从低位到高位).同时输出端的位数=2 ^n^ ;(设输入端位数为n);

1.2译码器source文件撰写

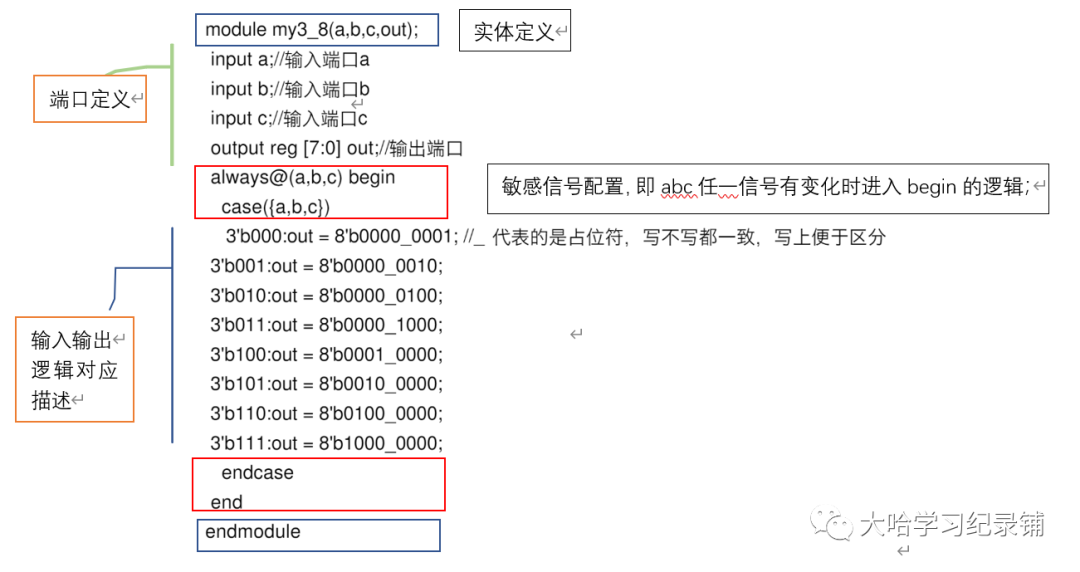

①Verilog以及VHDL如名字所示是一种硬件描述语言,接下来我们就要用verilog去描述出来上述的功能;

以3、8译码器为例:

VDHL语言其实和verilog大致相同,大家可以尝试阅读一下,主要还是以verilog为主;

②

library IEEE;

use IEEE.std_logic_1164.all;

entity mux83 is

port (

c : out std_logic_vector(7downto 0);

s1,s2,s3:in std_logic;

s : in std_logic_vector(2downto 0));

end mux83;

architecture mux83_arch of mux83 is

begin

p1:process(s,s1,s2,s3)

begin

if(s1='0')then

c<="11111111";

elsif(s1='1' and s2='0' and s3='0')then

cases is

when"000"=> c<="01111111";

when"001"=> c<="10111111";

when"010"=> c<="11011111";

when"011"=> c<="11101111";

when"100"=> c<="11110111";

when"101"=> c<="11111011";

when"110"=> c<="11111101";

when"111"=> c<="11111110";

when others=>c<="11111111";

end case;

else c<="11111111";

end if;

end process p1;

end mux83_arch;

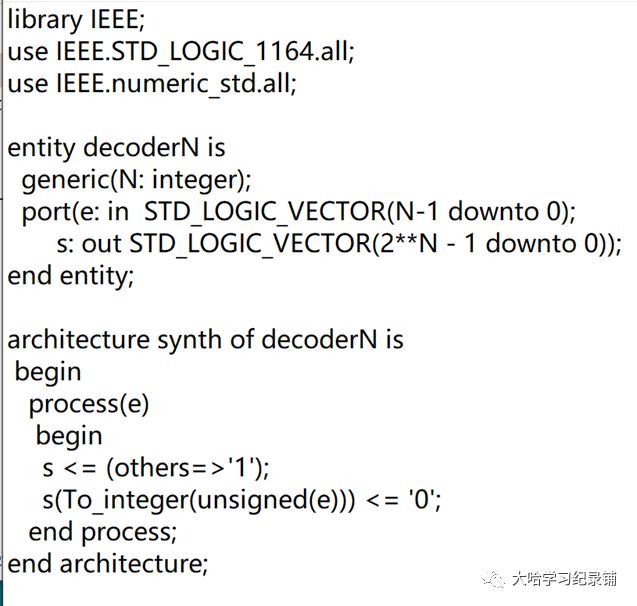

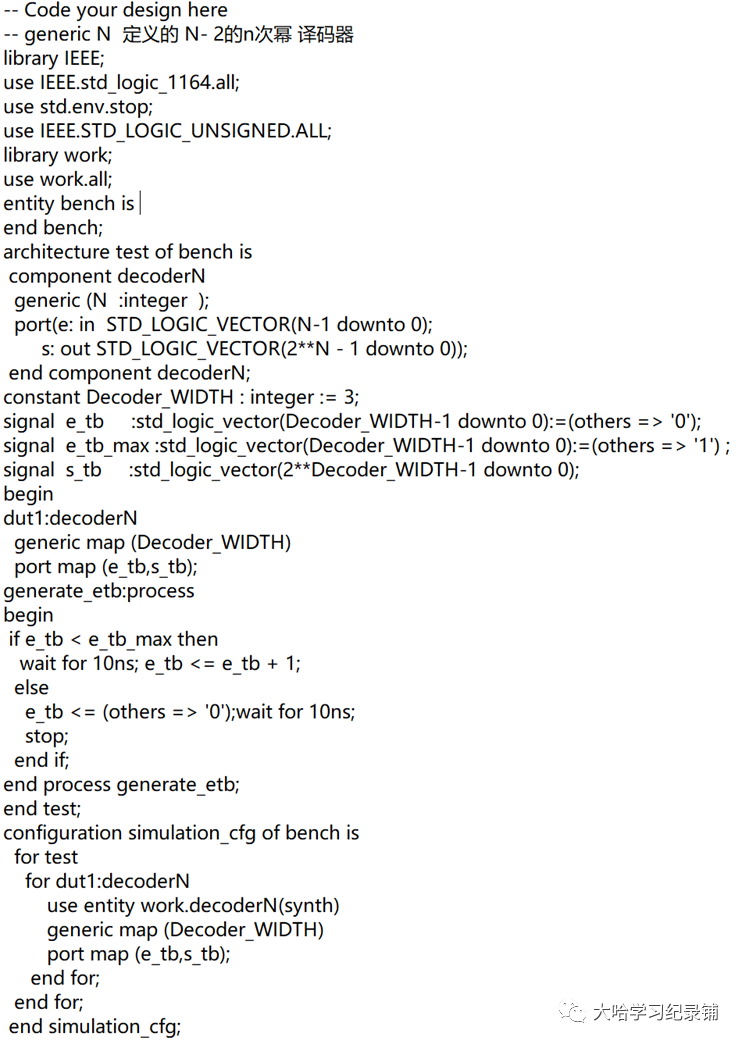

③以及VHDL版本的通用译码器:

1.3对应测试文本撰写

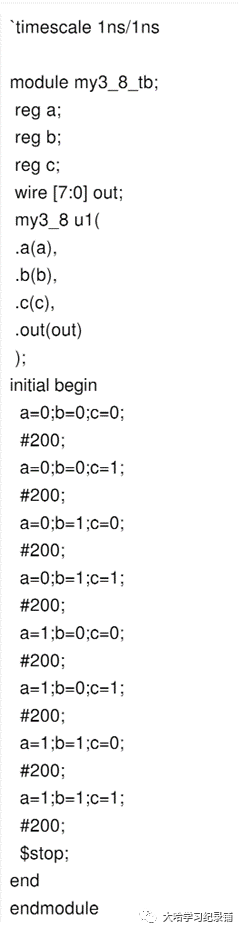

①

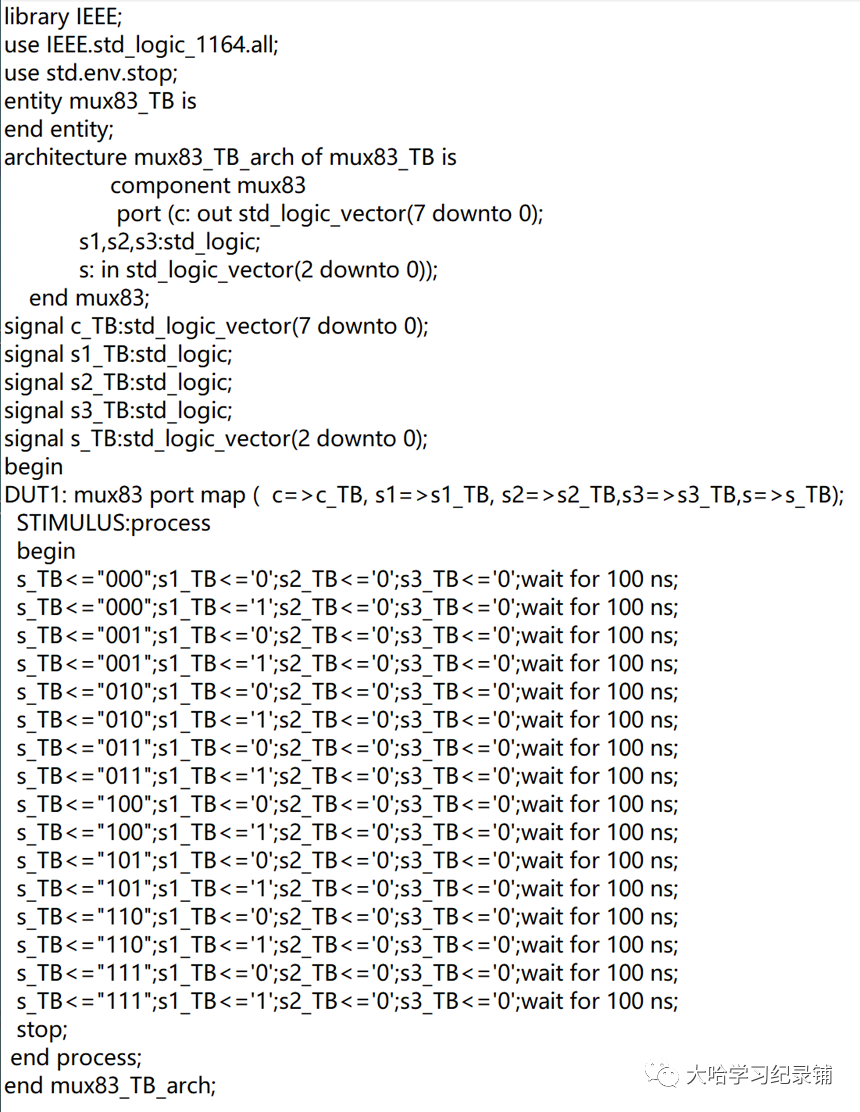

②

③

源文件暂时还不知道如何上传,目前仅供自己总结复习。有任何建议可以小窗私信我哦;

(表格用word画的,直接截屏使用了,有点粗糙,下次好好整。

这周先这样儿先这样儿

-

译码器及多路选择器的使用( EDA 仿真) 实验2010-02-06 5919

-

[6.1.1]--5.1数据选择器和显示译码器学习电子知识 2022-12-04

-

全译码器可作什么使用?2015-05-18 0

-

译码器定义2021-12-07 0

-

4选1多路选择器是什么?2022-02-09 0

-

如何设计32选1数据选择器2022-04-18 0

-

多种方式自制CPU 译码器2022-10-02 0

-

基于FPGA的多路选择器设计(附代码)2023-03-01 0

-

译码器、数据选择器及应用2007-12-20 1007

-

译码器和数据选择器2009-03-20 1398

-

译码器,编码器,数据选择器,电子开关,电源分册2017-09-21 611

-

一文解析多路选择器的工作原理及电路实现2018-04-27 56952

-

多路选择器有哪些_多路选择器分类介绍2018-04-27 32093

-

4选1多路选择器电路图(四款多路选择器电路)2018-04-27 132422

-

eda四选一多路选择器的设计2018-04-27 30181

全部0条评论

快来发表一下你的评论吧 !