FPGA奇偶校验的基本原理及实现方法

描述

在数字电路中,数据的正确性非常重要。 为了保证数据的正确性,在传输数据时需要添加一些冗余信息,以便在接收端进行校验。 其中一种常用的校验方式是奇偶校验(Parity Check)。 本文将介绍奇偶校验的基本原理及实现方法,并给出FPGA实现的代码示例。

一、奇偶校验原理

奇偶校验是一种基本的数据校验方式,其原理是在数据的尾部添加一个位,使得该位和数据中所有1的个数之和为奇数或偶数。 由于校验位的加入,使得数据传输中一旦数据错误就能够被检测出来,从而保证了数据的正确性。

奇偶校验可以采用两种方式:奇校验和偶校验。

奇校验::全部数据和该校验位中“1”的总数为奇数,则表示数据无误,否则数据错误

偶校验:全部数据和该校验位中“1”的总数为偶数,则表示数据无误,否则数据错误

奇偶校验的优点是简单、快速,不需要大量计算。 但是奇偶校验只能检测出错误,不能纠正错误,因此在实际应用中很少单独使用,通常与其它更加强大的校验方式结合起来使用。

以输出一组16bit数据为“1100_0011_1101_0100”为例,这组数据中有8个“1”。

如果使用奇校验,则校验位为1,传输数据实际为16bit数据+1bit奇校验位,即“1100_0011_1101_0100_1”。

如果使用偶校验,则校验位为0,传输数据实际为16bit数据+1bit偶校验位,即“1100_0011_1101_0100_0”。

二、FPGA奇偶校验设计

1、多位输入,分别用每位做:与、或、异或

module test(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

//方法一

assign out_and = in[0] & in[1] & in[2] & in[3];

assign out_or = in[0] | in[1] | in[2] | in[3];

assign out_xor = in[0] ^ in[1] ^ in[2] ^ in[3];

//方法二

assign out_and = ∈

assign out_or = |in;

assign out_xor = ^in;

endmodule

2、奇偶校验测试

奇偶校验只要求出其中一个,另一个取反即得到了。

module parity_check(

input [7:0] data_in,

input sel,

output check

);

wire even;// 偶校验

wire odd;// 奇校验

assign even = ^data_in;

assign odd = ~even;

assign check = (sel)?odd : even;

endmodule

测试激励

module sim(

);

reg clk;

reg [7:0] data_in;

parity_check u_parity_check (

.data_in(data_in),

.sel(1'b0)

);

initial begin

data_in = 0;

#10 data_in = 8'b1011_1000;

#10 data_in = 8'b1011_0000;

#10 data_in = 8'b1111_1000;

#10 data_in = 8'b1011_1100;

#10 data_in = 8'b1011_1010;

#10 data_in = 8'b1111_1010;

#10 data_in = 8'b1011_1001;

#10 data_in = 8'b1011_1101;

#10 data_in = 8'b1011_1011;

#10 $finish;

end

endmodule

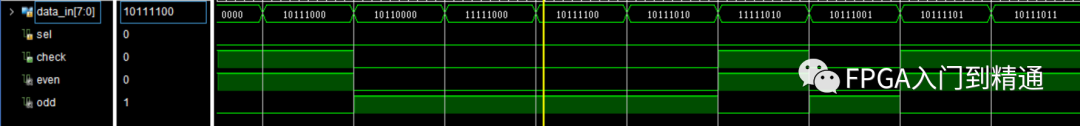

仿真测试结果图:

从图中可以看出,仿真测试结果与预期一致。

三、总结

奇偶校验算法很简单,实现起来也很容易,本文提供了一个比较简单的方法实现,大家可以参考下。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

stm32串口奇偶校验2021-07-23 9921

-

串口调试助手的奇偶校验测试方法2015-04-28 0

-

奇偶校验码2009-10-13 4750

-

奇偶校验器,奇偶校验器是什么意思2010-03-08 2057

-

奇偶校验码,奇偶校验码原理是什么?2010-03-17 61774

-

奇偶校验器_奇偶校验设计程序2011-11-11 5501

-

stm32 usart奇偶校验如何配置2021-07-23 6687

-

增强FIFO模式下的奇偶校验2022-11-02 719

-

介绍FPGA奇偶校验的基本原理及实现方法2023-05-22 1178

-

如何实现一种基于FPGA的奇偶校验器设计?2023-09-05 475

-

奇偶校验器的设计方法和特点2023-09-05 1178

-

什么是奇偶校验 奇偶校验的基本原理 奇偶校验电路什么意思2023-10-17 2680

-

什么是奇偶校验电路?奇偶校验器是时序逻辑电路吗?2023-10-17 2632

-

什么是奇校验和偶校验?常见的奇偶校验方式有哪些?2023-10-17 7856

-

奇偶校验和crc校验的区别 CRC校验和奇偶校验之间有什么关系?2023-10-17 2465

全部0条评论

快来发表一下你的评论吧 !