CDM防护措施以及设计思路

电子说

描述

一.封装

前几期曾经讲过,对封装后的芯片进行CDM测试,大量非平衡载流子会通过金线集聚到封装框架中。所以封装也是影响CDM的关键因素之一,恰宜的封装能大幅度提升芯片的CDM防护等级。(笔者对于封装还是才疏学浅,这里就不多做笔墨了。)

二.片内防护

CDM是一种自发性的,从内到外的ESD事件。所以其波形参数并不固定,虽然CDM的瞬态电流峰值很高,但是持续时间短,脉冲能量低。其防护电力路的设计思路与HBM还是有一定差异。CDM与HBM防护设计的主要区别有:

因为放电机理不同,CDM防护设计与HBM防护设计的侧重点不一,HBM侧重于过电流能力,同时需要设计合理的Design Window,而CDM侧重于瞬态特性,CDM很少关注Design Window和过电流能力。

防护部位不一,HBM会对MOS的源,漏,栅;隔离环;输入电阻等都会造成损坏,而CDM的只会对MOS管的栅极造成破坏。

失效机理差异,HBM波形虽然峰值电流低,但是其持续时间长,放电功率大,HBM设计需要将电学特性与热电特性相结合。反观CDM,因为其总能量很低,只需要关注其高频脉冲特性。

相较于HBM,CDM防护的设计目标更加明确,但是因为其较高的频率和由内而外的机制,所以设计难度也高一些(越先进的制程CDM设计越难)。本文针对CDM的设计从全片ESD策略,布局布线,器件特性的角度进行分析。

2.1 全片防护策略

目前全片ESD防护策略大致分为两种:一种是Pad-Based;一种是Rail-Based。两种策略的区别在于触发机制,Pad-Based是利用寄生器件的反向击穿/正向导通特性,构建从Pad到Power Rail的双向ESD通路,在Pad端实现ESD泄放,所以Pad-Based策略属于电压触发。GGNMOS,SCR,二极管串,都属于Pad-Based型ESD防护器件。

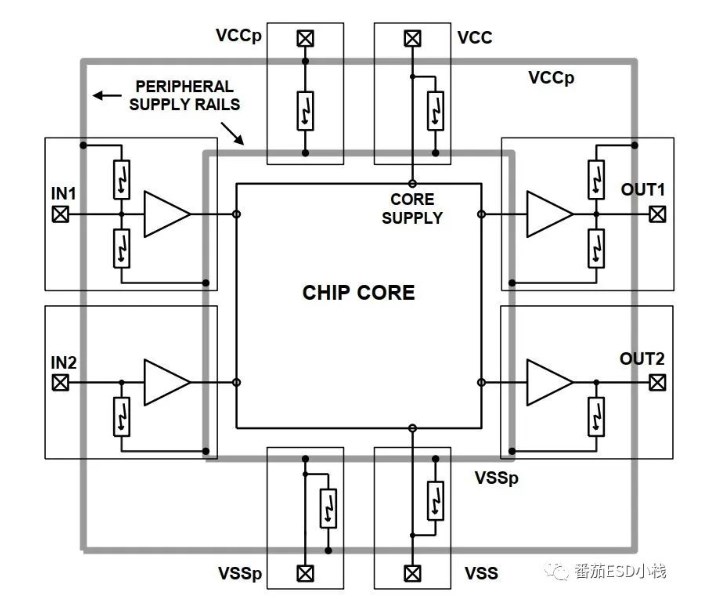

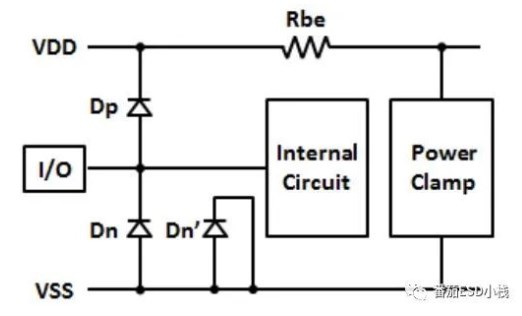

图一.Pad-Based 电路结构。

Rail-Based是利用二极管的正向导通特性,将ESD电流先行从端口转移到Power Rail,再利用RC电路的频率触发特性,利用响应栅压开启BigMOS,将Power Rail上的ESD电流通过MOS泄放。实现了Rail to Rail的ESD泄放。

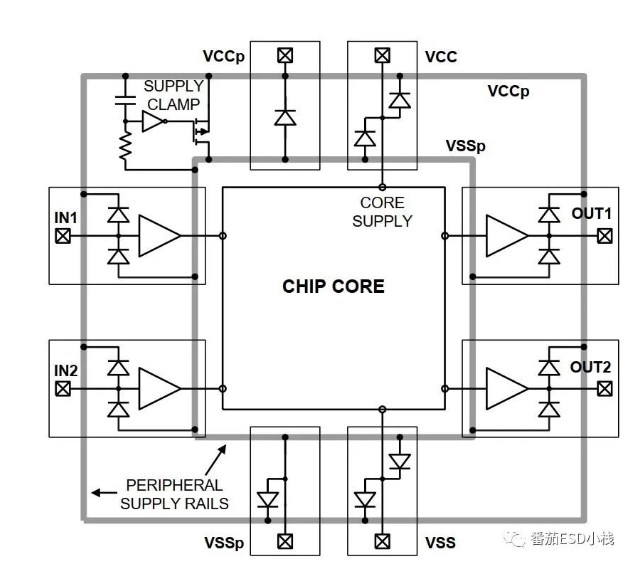

图二.Rail-Based 电路结构。

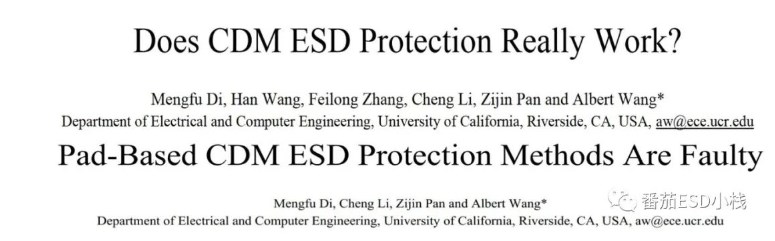

两种策略各有千秋,适用于不同的场景。但是目前学术界对Pad-Based全片防护策略针对CDM的性能与机制产生了质疑。学者认为Pad-Based全片防护策略可能并不适合于CDM防护。

图三.Pad-Based 电路结构对CDM防护乏力。

Pad-Based电路结构无法有效对CDM进行防护,主要因为Pad-Based结构多利用寄生器件的反向击穿电压或者正向导通累积电压实现正常工作与ESD的区别,也就是Design Window的设置。而该类器件因为异质结,普遍具有较大的寄生电容参数,对高频CDM的开启响应缓慢,瞬态电压高,阻碍CDM泄放,很难实现令人满意的CDM保护效果。而Rail-based电路结构则是利用ESD的频率特性,只要Power Rail上的特征频率满足要求,MOS就会开启,通过MOS管的沟道实现ESD泄放。由于RC-detector电路具有特征频率的向下兼容性,RC电路能对HBM和CDM都产生响应。

2.2 端口防护策略

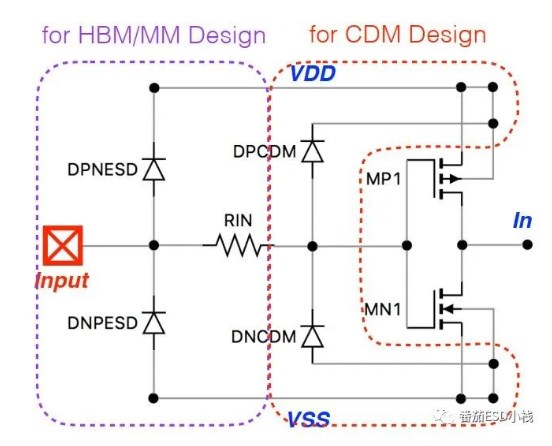

目前大多数芯片的IO端口都会采用端口二级防护策略。一级防护针对HBM和MM波形,器件面积大,寄生电容大,开启速度慢,适合泄放大电流。二级防护针对CDM波形,面积小,寄生电容小,开启速度快,能快速对CDM进行响应。两级保护之间的电阻R一方面提高栅极的鲁棒性,一方面限制HBM进入二级保护电路。

图四.CDM的端口防护。

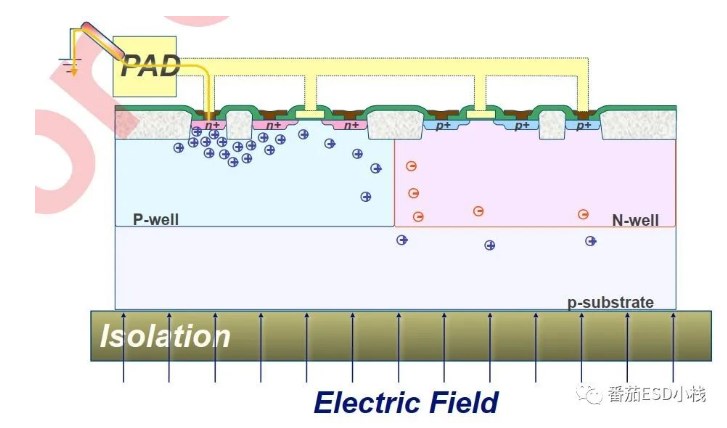

根据前几章的阐述,CDM源于半导体材料内部。所以二级保护器件需要尽可能的靠近被保护的电路元件,同时还需要和被保护的器件位于同一衬底内,需要其尽可能快的泄放衬底中的非平衡载流子。

图五.CDM防护示意图。

如图所示,衬底中的非平衡载流子通过同一衬底中的N+/P-WeLL二极管和P+/N-WeLL二极管流出体系,避免了栅极所面临的失效风险。

2.3 布局布线

CDM是一种未经调制的高频波形,其能量主要集中在高频波段,而高频波对电容电感较为敏感。所以布局布线对CDM防护也有一定影响。

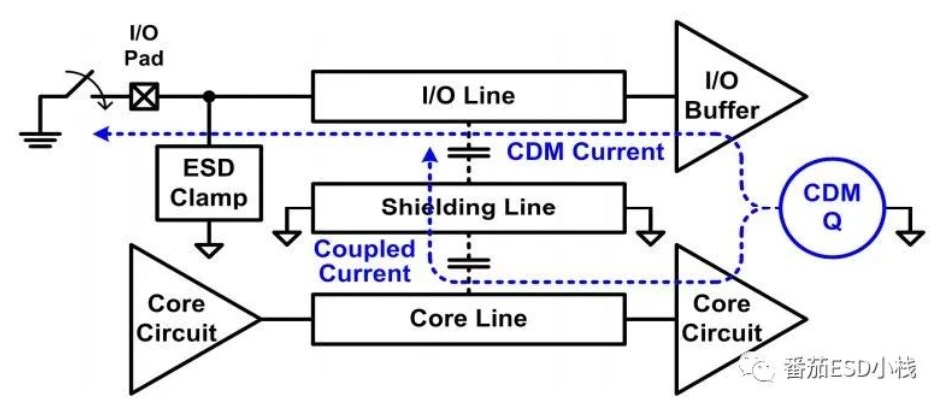

图六.屏蔽线对CDM的影响。

如图所示为屏蔽线对CDM的影响,某些设计会在IO线缆旁放置一条接地屏蔽线,但是该屏蔽线会降低体系对CDM的防护能力。屏蔽线会与IO线缆发生耦合作用,在IO上产生耦合电流,降低CDM鲁棒性。

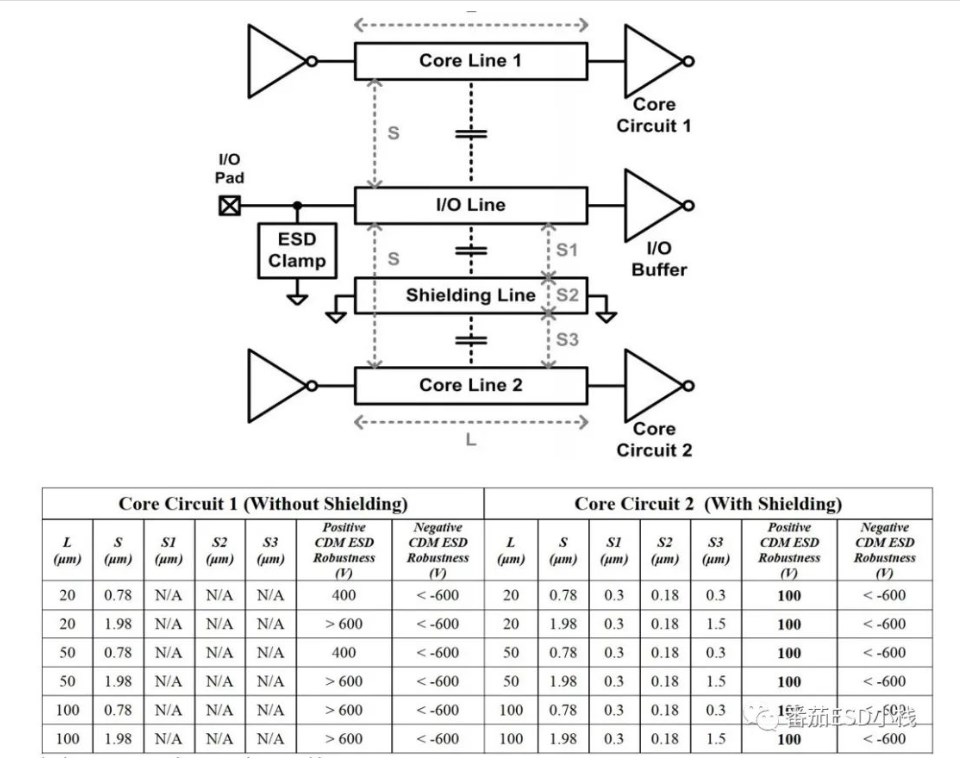

图七.布局布线对CDM的影响。

如图所示,布线细节也会对CDM能力产生影响。平行走线长度越长、走线与走线之间的间隔距离越大,防护效果越好。根据传输线模型,线缆会对高频信号造成衰减,而CDM能量主要集中在高频波段,平行走线长度越长,线缆造成的高频衰减越大,能略微提升CDM防护效果。CDM作为一种物理现象,波形频谱分布极其复杂。线缆间的耦合作用更加难以预测,所以增加关键IO线缆间的距离,降低耦合作用,也能提高CDM的防护效果。同时IO端口的走线也不要频繁跳线,避免CDM波形在金属线中发生反射与折射。

2.4 特殊元器件

为了降低CDM所带来的破坏,针对CDM的定制化器件也逐渐步入视野。笔者所列之一是前文已经提到过的Ploy-diode(浅谈ESD防护—二极管的应用),另一种是LCSCR(Low-Capacitance SCR)。

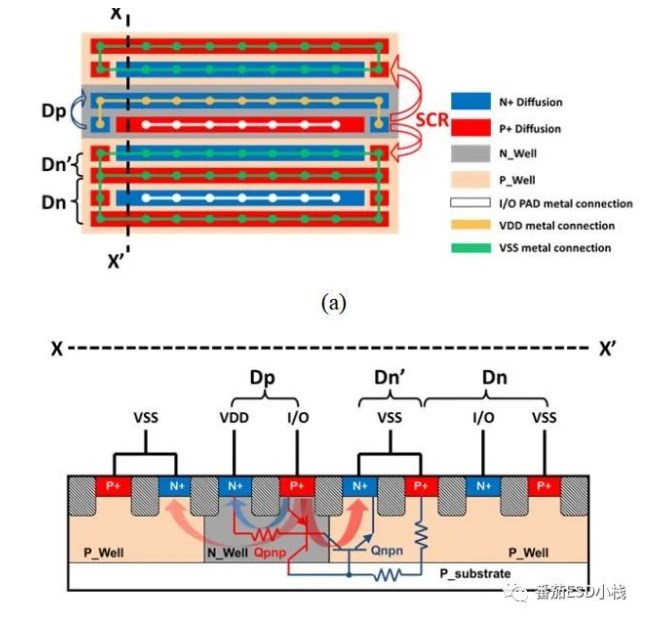

LCSCR器件的版图与剖面图如下,该结构中有寄生二极管Dp,Dn也有寄生三极管Qpnp和Qnpn。

图八.LCSCR版图与剖面图。

LCSCR是将IO到VDD和VSS的ESD器件进行了集成。该器件的ESD通路如下:

VDD—GND:通过Power Clamp(RC+GCNMOS)泄放。

GND—VDD:通过Power Clamp 并联二极管泄放。

IO—VDD:通过寄生二极管(P+/N-WeLL)Dp进行泄放。

VDD—IO:VDD上的静电流先通过Power Clamp(RC+GCNMOS)进入GND轨,然后通过寄生二极管Dn到达IO。

GND—IO:通过寄生二极管(P-WeLL/N+)Dn进行泄放。

IO—GND:首先静电流通过Dp进入VDD后,又通过Power Clamp泄放到GND,因为N-WeLL阱电阻的存在,寄生三极管Qpnp的栅极会有压降,该寄生三极管会开启,同时静电流经过P-WeLL也会产生压降,寄生三极管Qnpn在栅压下也会开启。寄生三极管Qpnp和Qnpn相互正反馈,从而建立新的ESD泄放通道,取代Dp—Power Clamp的泄放路径。相较于传统SCR,因为该ESD防护网络采用Rail-Based策略,所以静电流通过Dp进入VDD后,Power Clamp会快速开启,电压降很低。所以基本不会影响VDD—IO,IO—GND路径的导通电压和Trigger Voltage。

图九.LCSCR电路图。

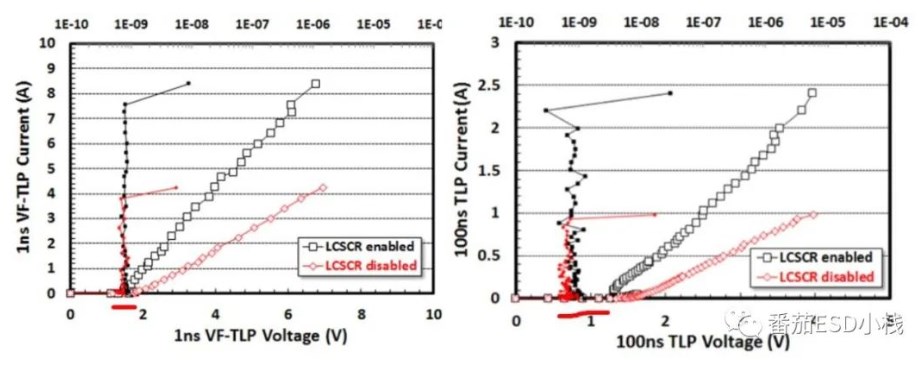

LCSCR的ESD性能如下图所示:

图十.LCSCR的TLP和VF-TLP曲线对比。

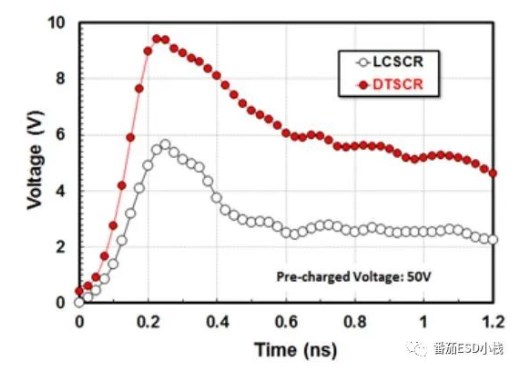

如图为LCSCR与传统二极管的ESD性能对比,可以看出无论是TLP还是VF-TLP,新型LCSCR器件的性能都更加优异。其过冲电压也比二极管串触发的DTSCR优异。该器件具有良好的CDM防护性能。

图十一.LCSCR的瞬态过冲电压。

两种结构中,Ploy-Diode已经在某些产品中得到了大规模应用,具有良好的前景。而LCSCR结构简单,性能优异但是还需要更多的验证。

-

干货 工程师该如何培养防护方案电路设计的思路2016-07-12 0

-

雷击浪涌防护方案基本设计思路2018-01-30 0

-

SMT电子生产中的静电的危害和防护措施2018-08-29 0

-

请问GSM/GPRS/GPS模块怎么引入静电防护措施?2019-05-31 0

-

ESD有哪几种防护措施?2021-03-18 0

-

数码产品的静电防护措施有哪些?2021-05-24 0

-

静电防护措施在电视机生产中的应用2010-12-31 651

-

手机的辐射和防护措施2009-03-15 1409

-

通信系统过电压产生的原因与防护2009-07-11 925

-

CDM6系列断路器操作指南2017-10-23 1359

-

油船腐蚀的类型及防护措施2021-06-07 431

-

DDoS攻击原理 DDoS攻击原理及防护措施2022-10-20 300

-

低压配电柜的防护措施和防护等级2023-04-12 5493

-

磐石测控:深圳液压动态疲劳试验机的基本防护措施?2022-11-23 406

-

静电的危害及防护措施2024-01-03 676

全部0条评论

快来发表一下你的评论吧 !