车规芯片-双核锁步介绍

汽车电子

描述

注重安全性的汽车设计需要一些特殊的实现功能,以实现可自动兼顾安全性的 P&R,包括三重投票触发器(Triple Voting Flop)插入、 安全岛生成、逻辑隔离缓冲器插入和不同布线约束的规范。本文讲讲双核锁步。

利用完全集成的流程,数字安全机制可以通过 Genus Synthesis、Innovus Implementation(P&R)、Cadence Modus DFT Software 和 Conformal Equivalence Checker 进行设计、管理和验证。Genus Synthesis 可以自动插入安全机制,如 TMR flops 或双核锁步(DCLS)控制器,并加快安全机制综合。然后,Innovus Implementation 可以自动创建和控制投票触发器的插入,并管理 DCLS 控制器安全岛的创建、形状和布线。

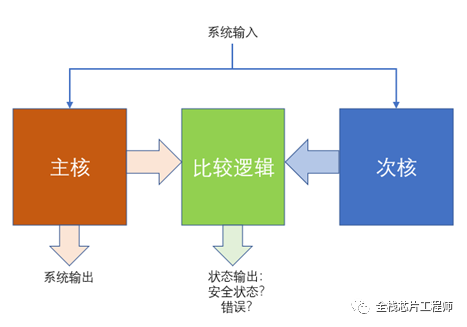

双核锁步(DCLS:Dual Core Lock Step):

双核锁步(DCLS)是指对安全关键型的核心处理模块进行复制,在每一个时钟周期对双核的输出进行比较,在发生故障时输出错误标识信号,以供系统及时采取应对措施。

以电动助力转向(EPS)应用场景为例,用于EPS的MCU必须满足ASIL D,确保汽车的转向系统是可预测的、确定的、安全的。EPS控制系统通常使用双核锁步MCU,并增加内部自检、使用高级电源管理解决方案提高安全性,防止电源故障和时钟故障带来的安全风险。

那么逻辑综合、后端实现,在布局、时钟树综合、布线等每一步骤上做哪些处理才能减少主核与次核共模失效的几率呢?答案参见全栈芯片工程师知识星球。

虽然可以使用完全自动化的 RTL-to-GDSII 流程进行数字安全设计和实现,但模拟和混合信号设计流程并没有为模拟综合和物理实现的 P&R 提供这种自动化水平。大量的现场失效是由产品的模拟或混合信号部分引起的,因此引入了基于缺陷导向测试概念的综合模拟故障仿真方法,以测量和最大程 度提高检测覆盖率。IEEE P2427工作组对模拟仿真制造缺陷的定义进行了标准化,并提出了一套缺陷模型,大大简化了缺陷建模和仿真。

审核编辑:刘清

-

芯片IC封装形式图片介绍大全2007-11-10 6139

-

高精度AD采集芯片ADS7809的中文介绍2008-11-23 9213

-

pga2311音频功放芯片C语言程序详细介绍2016-05-23 2187

-

tms320vc33芯片主要功能介绍2017-08-30 2142

-

芯片 IC 封装工艺介绍(PPT)资料下载2021-03-31 1363

-

电源芯片U6117详细介绍与特点2021-04-07 5153

-

芯片的结构及芯片封装的类型介绍2021-12-10 6646

-

芯片是什么,芯片内部制造工艺的介绍2022-06-14 5635

-

KT148A语音芯片关于_音量_声音的所有介绍汇总_比如声音小等等_V12022-11-14 671

-

中国芯片设计应布局Chiplet架构介绍2023-01-09 884

-

射频433接收芯片Y62R介绍2023-09-05 650

-

芯片制造流片Corner介绍2023-11-01 2758

-

开关降压型单节锰锂电池/磷酸铁锂电池充电管理芯片TP5000X应用介绍2023-12-25 200

-

13.56MHz 非接触式读写卡芯片LS5120产品介绍2024-03-22 98

-

模拟芯片之电源管理芯片介绍2024-04-30 174

全部0条评论

快来发表一下你的评论吧 !