时序电路之不同触发器对比分析

模拟技术

描述

1什么是时序电路?

组合电路是根据当前输入信号的组合来决定输出电平的电路,换言之,就是现在的输出不会被过去的输入所左右,也可以说成是,过去的输入状态对现在的输出状态没有影响的电路。

时序电路和组合电路不同,时序电路的输出不仅受现在输入状态的影响,还要受过去输入状态的影响。

那么,如何才能将过去的输入状态反映到现在的输出上呢?时序电路到底需要些什么呢?

人类总是根据过去的经验,决定现在的行动,这时我们需要的就是—记忆,同样时序电路也需要这样的功能,这种能够实现人类记忆功能的元器件就是触发器。

按结构和功能,触发器可以分为RS型、JK型、D型和T型,在这里,我们只讲解比较有代表性的类型,RS型和D型。

2触发器就像一个跷跷板

触发器的工作方式与日本的“起坐亲子游戏”很象,日本的“起坐亲子游戏”,指的就是公园里的跷跷板,想起跷跷板,就能想象出RS触发器的工作原理。

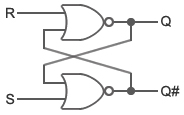

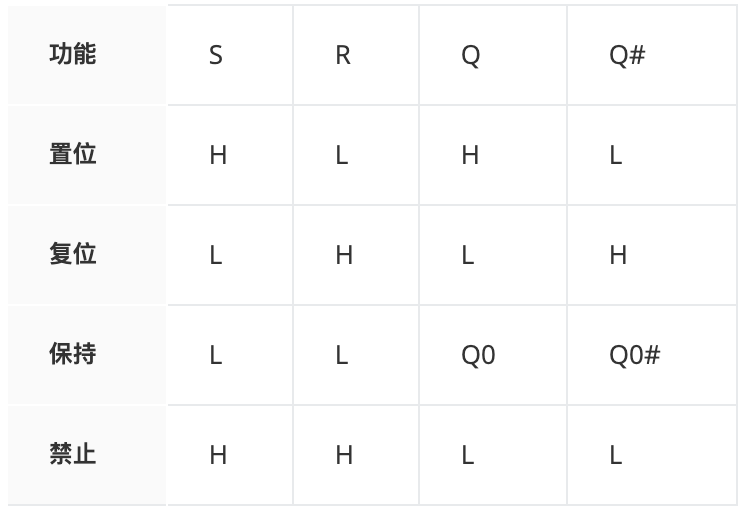

图1:RS触发器的电路图

图2就是一个跷跷板,这个跷跷板有些生锈,即使没有人坐,也不能恢复水平状态,请记住它保持倾斜的样子,假设:

跷跷板的两端是输出Q和Q#。

左右的2个人是R君和S君,表示输入,坐上跷跷板表示逻辑高H状态,没有在跷跷板上表示逻辑低L状态。

每次只允许一个人坐,两人不能同时坐。

图2:跷跷板的初始状态 Q=L、Q#=H、R=L、S=L 当S君坐上跷跷板(S=H)时,输出Q就变为H(Q#变成L)(图3 )。

图3:S君坐在跷跷板上的状态 Q=H、Q#=L、R=L、S=H 即使S君下来了,跷跷板也不会改变动作(S=L),Q#还是L,不改变(图4)。

图4:S君从跷跷板上下来的状态 Q=H、Q#=L、R=L、S=L 当R君坐上跷跷板时,Q变成L(Q#变成H),当R君从跷跷板上下来时,也会保持L状态,从这个过程来看,我们是不是可以说跷跷板记住了以前坐过它的人呢。 用真值表表示RS触发器的工作过程,就像图5所示一样,表中Q0和Q0#表示的是输入变化以前的输出。

图5:RS触发器的真值表 RS触发器是最简单的触发器,主要用于防止机械式开关的误操作。

3按时钟变化记忆的D触发器

D触发器是在时钟信号(CK)的上升沿(信号从L→H的变化)或下降沿(信号从H→L的变化)时,保持输入信号状态,改变输出信号的触发器。

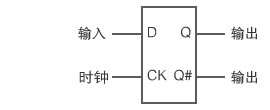

图6:D触发器

Q0:输入变化前的输出

x:H或L都可以

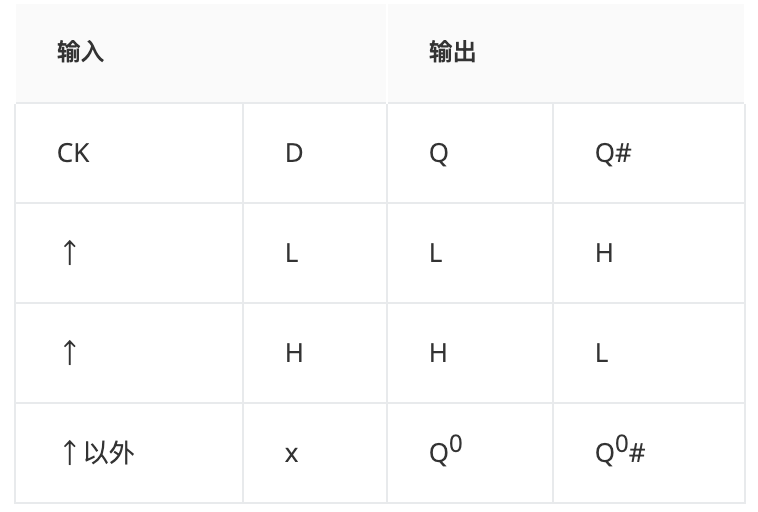

↑:L向H的转移 图7:D触发器的真值表 现在,我们用跷跷板来说明D触发器的工作原理,跷跷板的初始状态如图8所示,D君坐上跷跷板表示输入为H,从跷跷板上下来表示输入为L,跷跷板的另一边,放一个比D君轻的重物。 另外这个跷跷板与一般的跷跷板不同,只有在时钟CK上升沿时,才改变跷起的方向。

图8:D触发器的初始状态 CK=L、D=H、Q=L、Q#=H 看着图8,你不觉得有些奇怪吗?D君坐在跷跷板上,却没有变化,按理说,由于D君比重物重,D君(Q#)应该降下来,才对。 为什么跷跷板没有发生变化呢,这是因为CK还保持L状态,当CK变为H(CK上升)时,跷跷板就跷起来了,D君就下降了(图9)。

图9:D触发器的CK处于上升状态 D=H、Q=H、Q#=L 然后,CK就稳定在H状态,这时,不管D君是从跷跷板上下来,还是再坐上去,跷跷板都不动,只要不在CK的上升状态,跷跷板就一直保持以前的状态。 这种动作的触发器被称为D触发器,具有在时钟上升瞬间,保持(记忆)输入状态的功能,是一种时钟同步时序电路。 D触发器是时序电路的基本元件,用途广泛,D触发器的多级组合,可以做成移位寄存器、分频电路等,也可用于CPU内部的寄存器等。

4SRAM是触发器构成的吗?

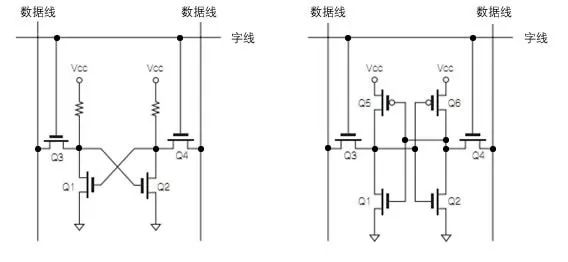

触发器可以记忆H或L,1位的信息,大量排列触发器,并使之具有可选择性后,就可以构成SRAM。

由于SRAM的输入输出速度比DRAM和闪存的访问速度高得多,所以,常用作CPU的缓存和寄存器。

尽管我们这样说,实际上CPU中内置的存储器或寄存器并非使用的是RS触发器这样的逻辑门。

由于使用逻辑门,会使电路规模变大,所以,一般使用4到6个FET,再经过优化构成存储器的1位(图A)。

图A:SRAM的基本电路

5时钟同步电路的必要性

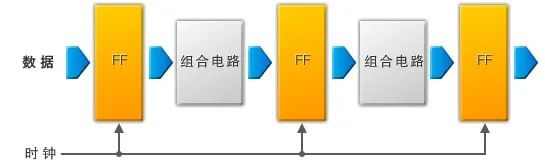

我们分两次,组合电路和时序电路,对逻辑电路的基础进行了讲解,实际上,在设计逻辑电路时,有很多应该注意的事项,其中特别重要的就是关于时钟同步电路的注意事项。 在组合电路中,微小的信号传输迟延,都有可能造成输出毛刺,尽管毛刺是一个极其短暂的信号,但也可以引起逻辑电路的误动作,为了回避这个问题,就要使用时钟同步电路。

图10:时钟同步电路的思路 图10给出了时钟同步电路的概要,如图所示,其构造是在FF(触发器)之间夹着组合电路,毛刺是组合电路在输出稳定之前,输出的短暂信号。 因此,在组合电路输出稳定以后,再改变时钟,用触发器保持这个输出,就可以回避这种误动作了。

编辑:黄飞

-

时序电路的分析与设计方法2018-08-23 0

-

时序逻辑电路的概述和触发器2018-08-23 0

-

什么是时序电路?2021-03-04 0

-

什么是时序电路?SRAM是触发器构成的吗?2021-03-17 0

-

FPGA从入门到精通——时序电路之触发器2021-07-04 0

-

怎样通过RS触发器去控制CPU的时序2021-07-22 0

-

哪些触发器时钟有效哪些无效2021-09-06 0

-

触发器与时序逻辑电路2010-08-26 866

-

触发器和时序逻辑电路教材2010-08-29 602

-

数字电路中的常见的触发器类型2019-07-05 13870

-

时序电路之触发器2021-01-06 4519

-

什么是同步时序电路和异步时序电路,同步和异步电路的区别?2023-03-25 19221

-

时序电路包括两种类型 时序电路必然存在状态循环对不对2024-02-06 479

-

时序电路的分类 时序电路的基本单元电路有哪些2024-02-06 748

-

时序电路基本原理是什么 时序电路由什么组成2024-02-06 692

全部0条评论

快来发表一下你的评论吧 !