时序逻辑电路设计之D触发器

描述

本文旨在总结近期复习的数字电路D触发器(边沿触发)的内容。

D触发器是一个具有 记忆功能 ,持有 两个稳定状态(0和1) 的信息存储器件,是数字电路初学者所能接触到最简单的 时序逻辑电路 , 也是多种时序逻辑的电路的基本逻辑单元。

边沿触发D触发器特点是可以在时钟脉冲到来时刻从一个状态翻转到另一个状态,其具有的存储特性也是时序逻辑的基本特征。

其内部结构可以由3个RS锁存器构成

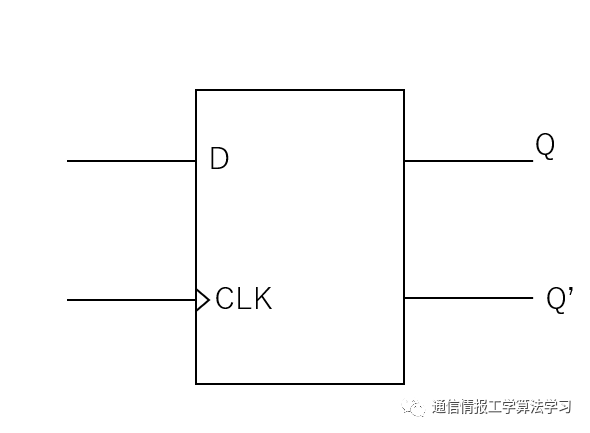

将其绘制成一个模型,最简单的如下图表示,D为数据输入端,clk为时钟输入端,Q为数据输出端口。

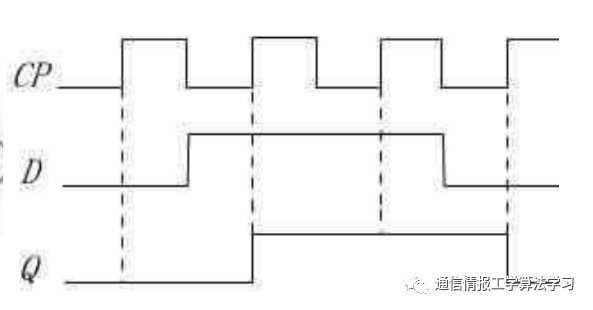

这种D触发器的功能也是相当简单的,就是当CLK上升沿到来时,Q的输出等于D,特征方程写为 Q=D* (没有任何控制输入的情况下)。 波形图如下所示:

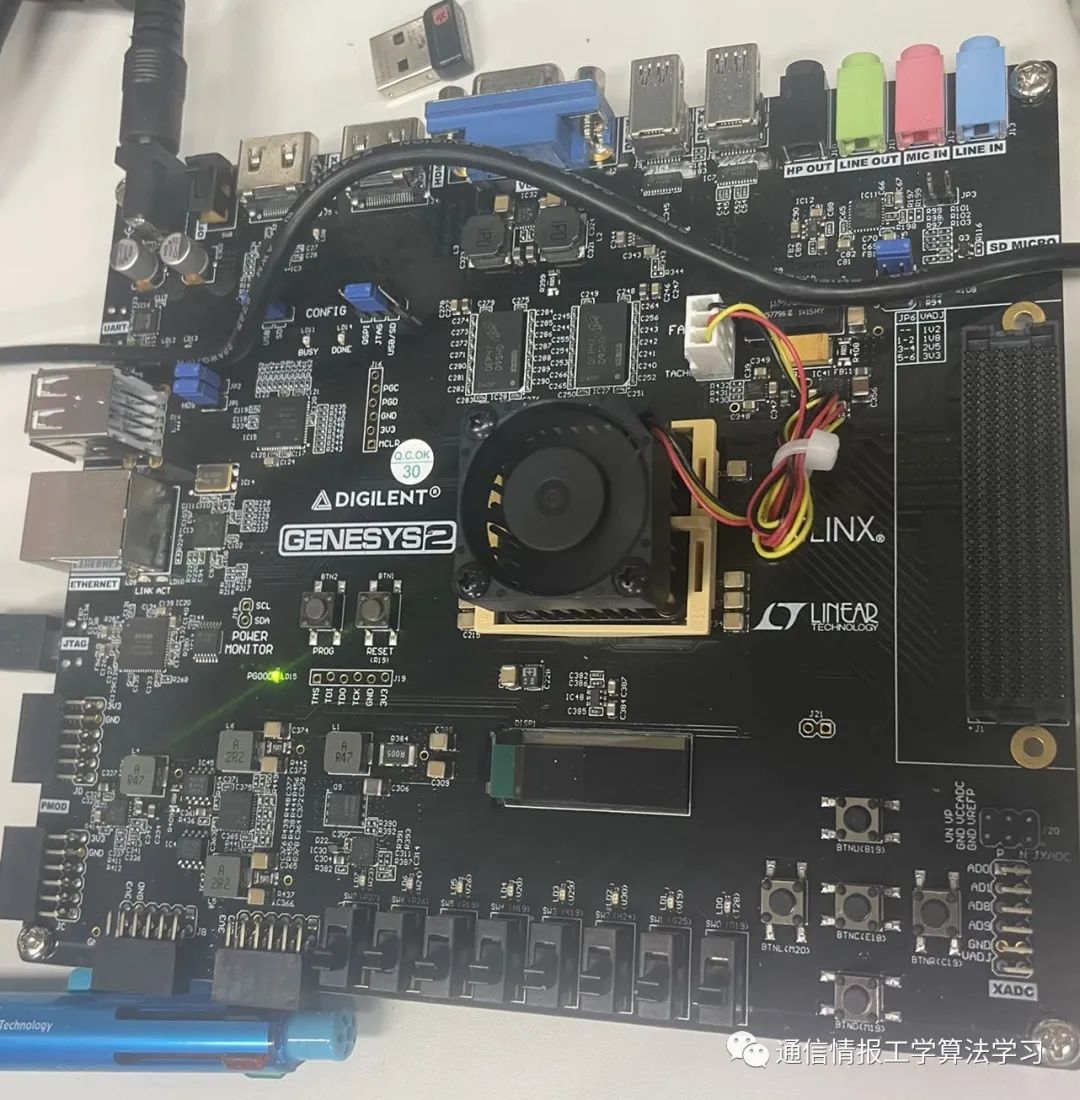

为了进一步具体得知其作用,接下来在FPGA开发板上展示其功能,使用的办卡为德致伦的genesys2,芯片为kintex-7系列的xc7k325tffg900-2。

为了更加全面一些,在此为D触发器增加复位功能(按下按钮回到初始状态),此时可以有两种复位D触发器,一种是同步复位,一种是异步复位。

同步复位:按钮按下,上升沿到来时刻复位,复位动作和系统时钟同步。

异步复位:按钮按下立刻复位,复位无需看系统时钟的脸色。

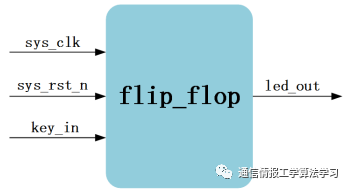

下面给出本设计的模块框图:

说明一下各个端口的作用,sys_clk为时钟,sys_rst_n为复位,key_in为按键输入,即为触发器的D,led_out为输出,本demo会将其接到开发板的灯上,用灯的亮灭展示D触发器的效果。

首先展示同步D触发器的verilog代码和testbench以及仿真结果。

module flip_flop(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in,

output reg led_out

);

always@(posedge sys_clk)

if (sys_rst_n == 1'b0)

led_out <= 1'b0;

else

led_out <= key_in;

endmodule

————————————————————testbench——————————————————————————————————

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2023/01/21 20:02:21

// Design Name:

// Module Name: tb_flip_flop

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_flip_flop(

);

reg sys_clk;

reg sys_rst_n;

reg key_in;

wire led_out;

initial begin

sys_clk = 1'b1; //时钟信号初始化为1

sys_rst_n <= 1'b0; //复位信号初始化,因为低电平有效,所以为0

key_in <= 1'b0; //输入信号的初始化

#20

sys_rst_n <= 1'b1; //20ns后,复位信号释放,因为低电平复位,所以变成高电平开始工作。

#210

sys_rst_n <= 1'b0;

#40

sys_rst_n <= 1'b1; //复位40ns再次释放

end

always #10 sys_clk = ~sys_clk;

always #20 key_in <= {$random}%2; //20ns产生一次随机数,比时钟周期大,利于波形观察

flip_flop flip_flop_inst

(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.key_in(key_in),

.led_out(led_out)

);

endmodule

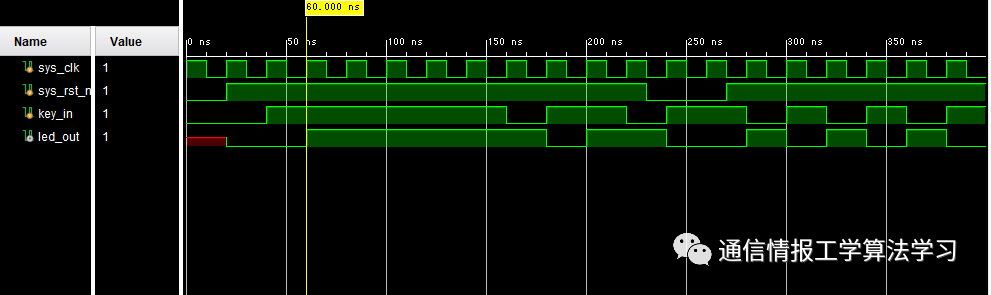

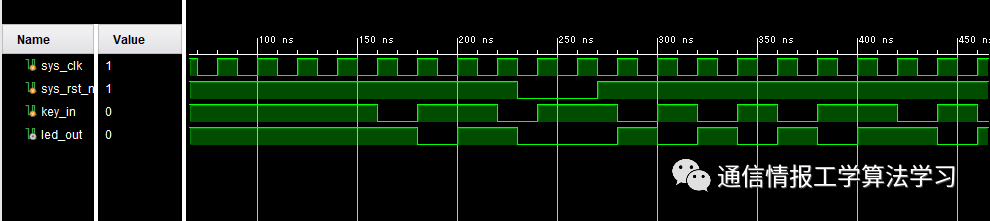

仿真结果跑500ns:

可以发现,尽管系统已经处于复位释放的状态(复位键为高电平),时钟,数据和上升沿也都到来,但是输出会在时钟的下一拍进行变化。 **即:当时钟和信号在同一时刻变化时,我们以时钟的上升沿前一时刻采集的输入信号为依据来产生输出信号。 **

下面是异步D触发器的代码,区别是增加了复位下降沿到来时刻的敏感性(always语句),testbench和同步D触发器的一致。

module flip_flop(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in,

output reg led_out

);

always@(posedge sys_clk or negedge sys_rst_n)

if (sys_rst_n == 1'b0)

led_out <= 1'b0;

else

led_out <= key_in;

endmodule

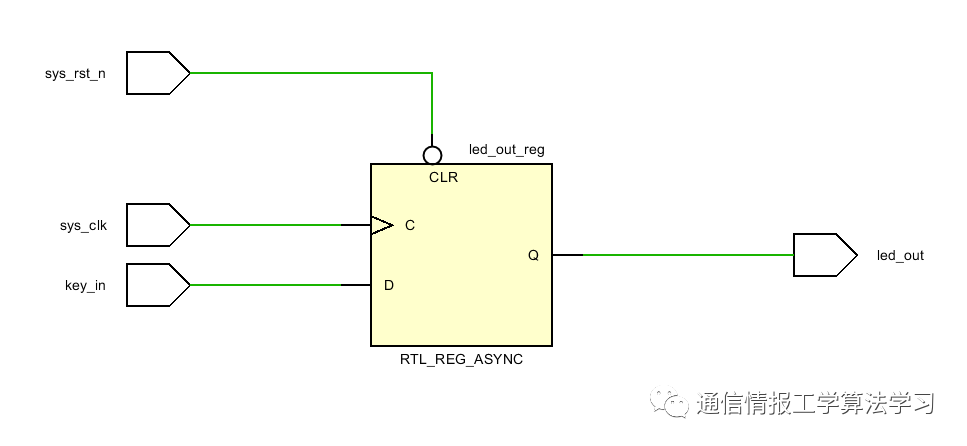

可以观察到复位下降沿到来时刻,输出即刻置为0,经过综合之后的RTL电路如图所示,和设计(异步D触发器电路,同步D触发器电路多一个MUX模块)的差不多。

然后分配管脚。

此次实验中出现的一个问题是,此次使用的FPGA已经没有单端口时钟输出,所以需要调用PLL的IP核合成输出一个单端口的时钟信号,这个准备下一篇再说。

实验设备(谢谢老板买的高级货,可惜许可证快到期了):

-

时序逻辑电路设计2009-03-20 0

-

时序逻辑电路实验2009-09-16 0

-

时序逻辑电路的概述和触发器2018-08-23 0

-

请问D触发器结构的五分频器逻辑电路怎么实现?2019-09-11 0

-

请问怎样去设计多输入时序逻辑电路?2021-04-29 0

-

触发器与时序逻辑电路2010-08-26 866

-

时序逻辑电路实例解析2010-04-15 5107

-

基于D触发器和数据选择器的多输入时序网络的电路设计2010-08-13 2900

-

时序逻辑电路有哪些(三款时序逻辑电路的设计)2018-01-31 54087

-

时序逻辑电路分为几类2019-02-26 49822

-

时序逻辑电路的分析方法2019-02-28 23666

-

D触发器与Latch锁存器电路设计2023-10-09 1499

-

FPGA学习-时序逻辑电路2023-11-02 396

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 1040

全部0条评论

快来发表一下你的评论吧 !