时序逻辑电路的分析方法

描述

时序逻辑电路分析

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

首先应该注意,时序逻辑电路之所以叫做时序,是因为电路的输出不单单与输入有关,还与电路本身的状态有关,即次态受到现态和输入的共同作用。 但是什么时候才能作用呢,是在时钟脉冲到来时电路可以作用,可能作用的是脉冲沿,也可能是整个时钟的高电平,这取决于你的触发器的选择,因而其本质上就是在时钟CP的作用下,电路状态不断被刷新的过程。

时序逻辑电路的基本结构如下图,存储电路就是由触发器组成的,实现存储功能。 设计和分析的主体即是这一部分,因为一般的组合逻辑电路较为简单,甚至可以没有。

我们从图中可以明显的看出时序逻辑电路的输出输入关系,即次态受到现态和输入的共同作用这一特点。 分析时,显然要表示出图中的未知量,也就是除了输入X之外的剩余三个量——Y(输出信号)、Z(驱动信号)、Q(状态信号)。 并且显然他们的函数关系如下,这三大方程就是时序逻辑电路分析和设计的最核心部分,其中最重要的是驱动方程(敲黑板划重点)。

同步时序逻辑电路的分析方法

所谓的同步,意思就是触发器的时钟脉冲都接入的同一个CP,触发器状态变化在同一时钟信号作用下

同时发生。 例如

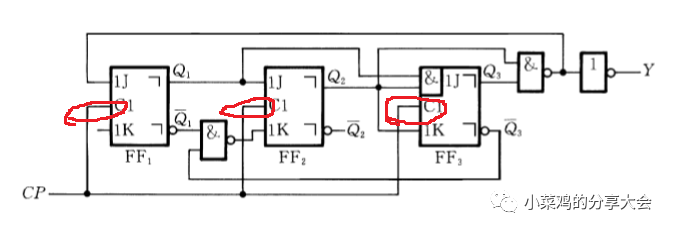

图中画圈部分就是这个电路的所有时钟信号,很明显的是他们都是同一个信号CP,因此这是一个同步电路。 接下来找三大方程,但是这里的顺序很重要,一般的步骤是:

①写出每个触发器的驱动方程;

②把驱动方程代入相应触发器的特性方程,得出每个触发器的状态方程;

③根据给定的逻辑图,写出电路的输出方程。

首先写驱动方程的意义在于,驱动方程是每个触发器的输入,比如上图就是找每个J等于什么,每个K又等于什么,是一个关于输入信号X和所有触发器现态的函数,在得到了J和

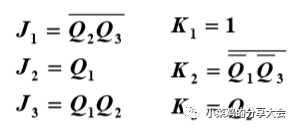

K之后代入触发器的特征方程【比如JK触发器就是Qn+1=JQn(非)+K(非)Qn】,我们就得到了触发器的状态方程,即次态,也就是真值表或者波形图中要求的最主体的部分。 最后根据整个电路分析出输出方程(这个比较简单,不赘述)。 例如这里的驱动方程如下:

从而得到状态方程

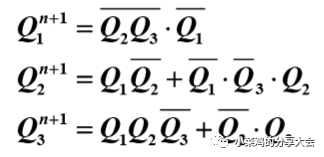

做完上述工作,分析就结束了一大半了,接下来就是分析电路功能的时候。 这里要注意的是,千万不要尝试去画波形图来解决这个事情,因为既麻烦也不好看,不如直接列真值表找主循环。 如图

很明显这是一个同步七进制加法计数器,比画波形图要直观的多。

到这里还并没有结束,还需要检查自启动问题,也就是上图最下面的那个不在主循环的红色状态(无效态),看看它是不是能进入主循环(经过多少步骤都可以),只要这些无效态自己不成循环,就是可以自启动了。 最后可以看要求画一画状态转换图,注意标定图例就好,这里不再赘述。

异步时序逻辑电路的分析方法

异步的意思就是触发器的时钟脉冲不再全都是同一个CP,它可能是另一个CP‘,也可能是某一个触发器的输出,但归根结底不是同一个CP。

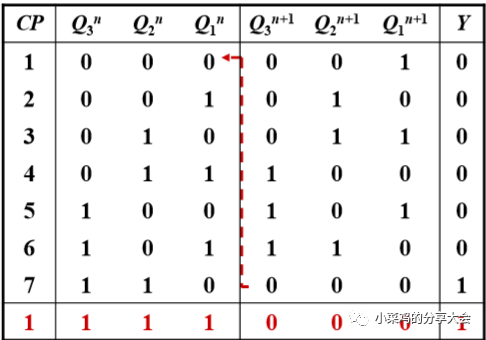

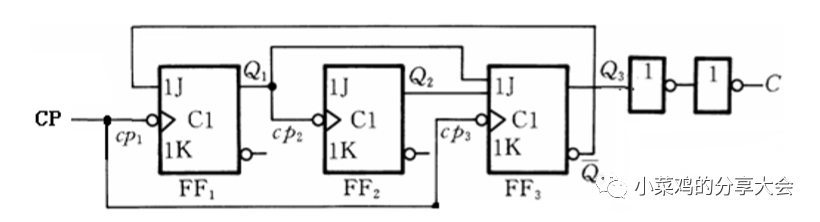

异步电路的分析方法与同步电路基本相同,唯一的不同点就是要在分析方程之前先要分析每个触发器的时钟信号CPi,并且需要在真值表中列出各个CP,在对应CP有效的情况下(如上升沿、下降沿、高电平等等),触发器的状态再去发生对应信号的变化,例如下图

很明显可以得到时钟信号:

cp1 = cp3 = cp,cp2 = Q1

余下步骤同同步电路相同,参照前文。

-

#硬声创作季 数字电子技术基础:时序逻辑电路的分析方法Mr_haohao 2022-11-06

-

#硬声创作季 卡通说解数字电子技术:异步时序逻辑电路分析方法Mr_haohao 2022-11-07

-

#硬声创作季 #无人机电子技术基础 课时154_3异步时序逻辑电路分析方法醉 2022-12-03

-

[6.5.1]--异步时序逻辑电路分析方法学习电子知识 2022-12-06

-

[7.1.1]--6.1概述+6.2同步时序逻辑电路的分析方法_clip001jf_75936199 2023-04-05

-

[7.1.1]--6.1概述+6.2同步时序逻辑电路的分析方法_clip002jf_75936199 2023-04-05

-

同步时序逻辑电路2009-09-01 796

-

第二十二讲 同步时序逻辑电路的分析方法2009-03-30 4932

-

时序逻辑电路的分析方法2009-04-07 8233

-

时序逻辑电路分析有几个步骤(同步时序逻辑电路的分析方法)2018-01-30 123437

-

数字电路教程之时序逻辑电路课件的详细资料免费下载2018-12-28 981

-

模拟电路教程之时序逻辑电路的课件资料免费下载2020-06-22 741

全部0条评论

快来发表一下你的评论吧 !