单片机系统里中断是什么呢?

控制/MCU

描述

01 什么是中断

前面的文章中我举上课的例子简单描述了中断,那么单片机系统里中断是什么呢?

中断,是指当计算机执行正常程序时,系统中出现某些急需处理的异常情况和特殊请求,CPU暂时中止正在运行的程序,转去对随机发生的更为紧迫的事件进行处理,处理完毕后,CPU自动返回原来的程序继续执行。

实现中断功能的硬件和软件系统称为中断系统。能向CPU发出中断请求的事件称为中断源。

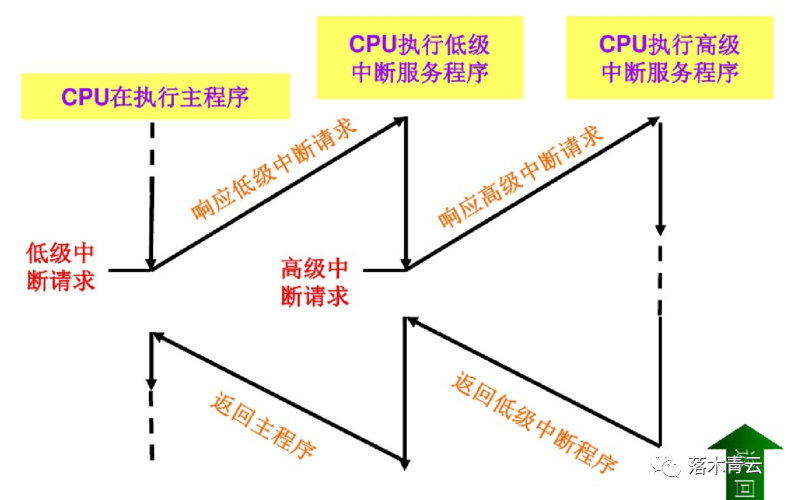

若有多个中断源同时请求中断时,或者CPU正在处理某外部事件时,又有另一外部事件申请中断,CPU通常会根据中断源的紧急程度,将其进行排列,规定每个中断源都有一个中断优先级。中断优先级可由硬件排队或软件排队来设定,CPU按其优先顺序处理中断源的中断请求。优先级高的事件可以中断CPU正在处理的低级的中断服务程序,待完成了高级中断服务程序之后,再继续执行被中断了的低级中断服务程序,这就是中断的嵌套。

02 中断源与中断优先级

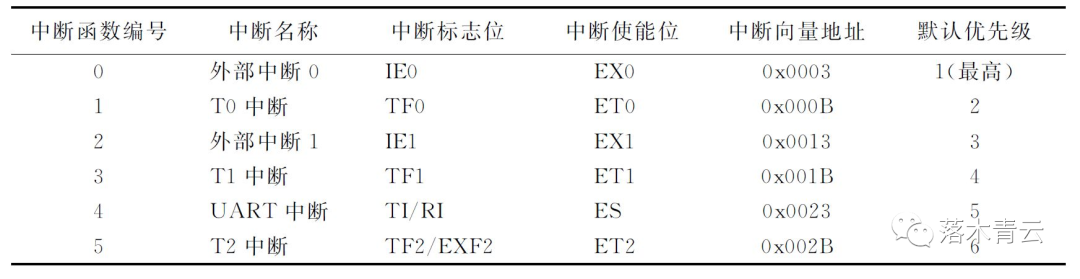

C51有如下5个中断源:

• INT0(P3.2)外部中断0。当IT0(TCON.0)=0时,低电平有效;

当IT0(TCON.0)=1时,下降沿有效。

• INT1(P3.3)外部中断1。当IT1(TCON.2)=0时,低电平有效;

当IT1(TCON.2)=1时,下降沿有效。

• TF0定时/计数器T0溢出中断。

• TF1定时/计数器T1溢出中断。

• RX,TX串行中断。

C52又增加了一个中断源,即定时/计数器T2溢出中断。

中断优先级是在列表越前面的优先级又高,表中列出了默认优先级,数字越小的优先级越高。当然也可以通过设置改变这个顺序。

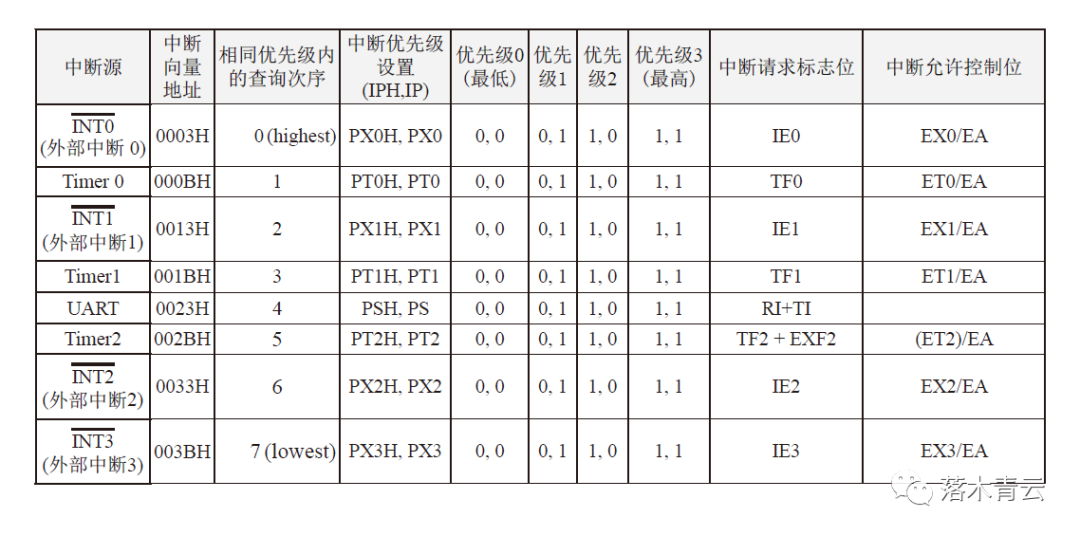

当然现在新上市的51单片机可能包含更多的中断源,但是基本的这几个肯定都有的,其他额外添加的也是大同小异,都能根据芯片手册看明白。比如STC89系列单片机就有8个中断源,如图:

03 中断控制寄存器

51单片机的中断相关控制寄存器包括了中断控制寄存器(Interrupt Enable register,IE)和中断优先级控制寄存器(Interrupt Priority register,IP),前者用于对 MCS-51单片机的中断工作状态进行控制,后者用于对MCS-51单片机的中断优先级进行控制。

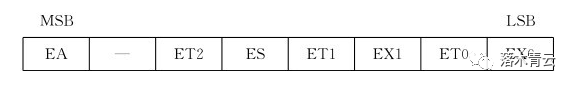

允许中断寄存器IE的各位定义如下:

EA是总中断允许位。当EA=0时,禁止所有中断;当EA=1时,每个中断源是允许还是禁止由各自的允许位确定。

ET2是定时器2中断允许位。当ET2=0时,禁止定时器2中断。

ES是串行口中断允许位。当ES=0时,禁止串行口中断。

ET1是定时器1中断允许位。当ET1=0时,禁止定时器1中断。

EX1是外部中断1允许位。当EX1=0时,禁止外部中断1。

ET0是定时器0中断允许位。当ET0=0时,禁止定时器0中断。

EX0是外部中断0允许位。当EX0=0时,禁止外部中断0。

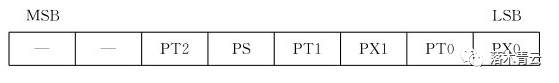

中断优先级寄存器IP的各位定义如下:

PT2是定时器2中断优先级设定位。

PS是串行口中断优先级设定位。

PT1是定时器1中断优先级设定位。

PX1是外部中断1优先级设定位。

PT0是定时器0中断优先级设定位。

PX0是外部中断0优先级设定位。

IP寄存器中各位均具有以下特点,即当为0时,为低中断优先级;当为1时,为高中断优先级。系统复位后,IP寄存器中各位均为0,即此时全部设定为低中断优先级。在中断执行过程中,低优先级中断可被高优先级中断所中断,反之不能。另外,同级的中断不能互相中断。当几个同级的中断源同时向CPU申请中断时,CPU按硬件次序排定优先权,依次为外部中断0(INT0)、定时/计数器T0溢出中断、外部中断1(INT1)、定时/计数器T1溢出中断、串行口中断、定时/计数器T2溢出中断。

04 总结

中断是我们开发项目时不可避免的一部分,就像生活中时刻都有可能发生意外一样,单片机工作时也可能随机遇到“意外”,因为单片机开发出来的产品都是服务于我们生活的,所以在程序设计时我们需要使用中断系统来完成产品的功能。后面我们在特定案例中再来讲解各中断的使用方法。

-

单片机原理及应用: 中断系统#单片机学习硬声知识 2022-11-06

-

单片机原理与应用: 中断系统应用#单片机学习硬声知识 2022-11-08

-

单片机原理及应用: 中断系统的结构#单片机学习硬声知识 2022-11-09

-

单片机的中断与定时系统2010-02-23 0

-

C51单片机学习笔记(四)——单片机的中断系统及应用 精选资料推荐2021-07-14 0

-

如何获取单片机发生程序异常的中断位置呢2021-12-02 0

-

单片机中断系统的相关资料分享2021-12-03 0

-

单片机教程十七:单片机的中断系统2009-05-15 4938

-

STM32单片机中断系统2016-11-11 1104

-

低功耗单片机系统外中断扩展技术研究2021-06-24 447

-

单片机--中断系统实验2021-11-05 628

-

C51单片机学习笔记(四)——单片机的中断系统及应用2021-11-14 747

-

51单片机的中断系统2021-11-22 516

-

单片机应用系统设计技术——中断实验12021-11-24 344

全部0条评论

快来发表一下你的评论吧 !