DRAM产品低功耗设计与演化

描述

前期我们从工作电压,频率,容量等产品规格,prefetch/burst length内部访问方式的角度介绍了DDR3/DDR4/LPDDR4(X)的一些主要feature及区别。

【芯科普】从DDR3到LPDDR4(X),看产品细分差异优化发展

话题一

DDR3/DDR4/LPDDR4接口差异

今天我们从接口实现上看一下其差异,通过上一篇对于其三者区别的分析,可以看到三者的不同点从外部来看主要是通过不同的接口来实现。因此我们今天具体来从接口实现上来分析之间的差异。

1DDR3

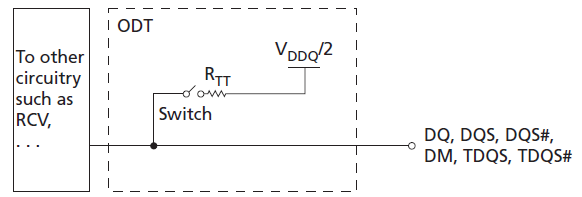

DDR3的接口为SSTL(Stub Series Terminated Logic),匹配电阻上拉到VDDQ/2。

2DDR4

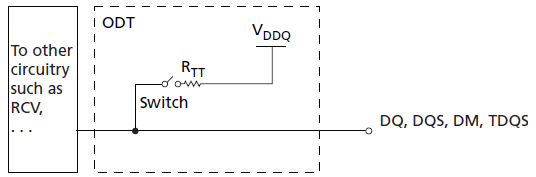

DDR4匹配电阻上拉到VDDQ,可称为POD(Pseudo Open Drain),用以减少IO电流消耗。对DDR4的POD来说,drive High(logic level ”1” )几乎不耗电,可以用这特点搭配DBI(Data bus inversion)来降低功耗。当一个字节里的 ”0” bits比 ”1” bits多时,可以使能DBI,将整个字节的“0”和“1”反转,这样 “1” bits就会比“0” bits多,达到省电的效果。

3LPDDR4

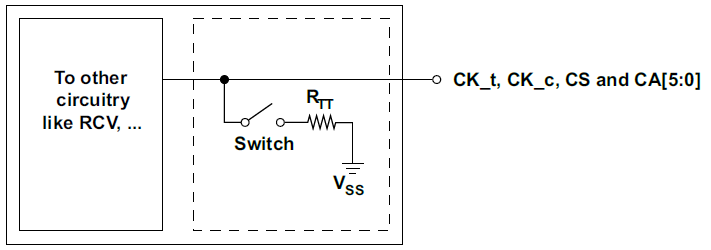

LPDDR4的匹配电阻下拉到VSSQ, 称为LVSTL(Low Voltage Swing Terminated Logic), 这样可以更省电,LPDDR4靠NMOS 晶体管pull up,也可以工作在更低的电压。

从上述DDR3到LPDDR4接口设计的演变的呈现,其目的主要是是为了满足产品对低功耗的要求,因此其工作电压也变得越来越低。

除此之外,对速度的要求需要越来越高的频率来实现,这对信号质量要求就会更高,因此用ODT(On Die Termination) 来实现impedance matching,减少反射波的影响,优化数据眼(Data eye),在高速信号的传输中提高信号质量。DDR2的termination开始放在芯片上,之后output driver可与ODT的电路共用,靠电路控制实现Output driver与ODT的电路切换。信号质量有多方面因素的影响,DDRPHY上的skew及Jitter,cross talk,inter symbol interface等等。

话题二

什么是DQS信号?

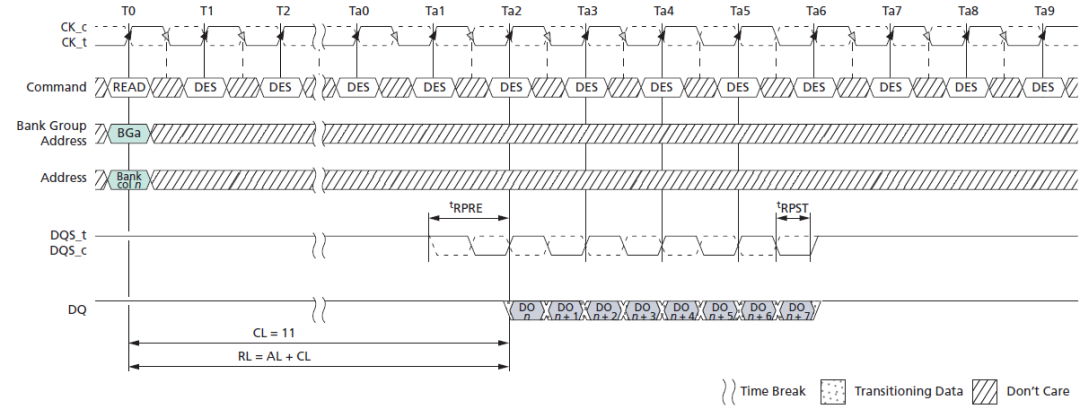

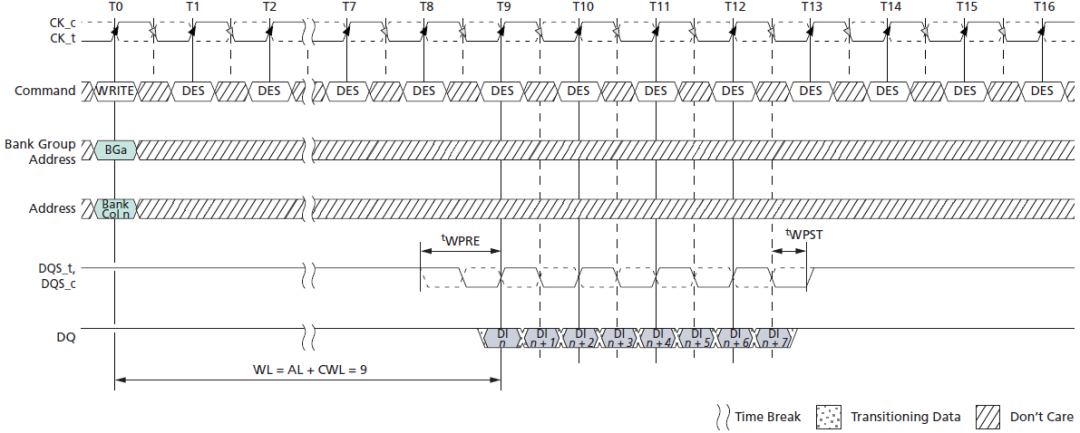

DDR(Double Data Rate) 在访问时接口上的DQS信号是源同步时钟,在接收端使用DQS来读出相应的数据DQ, 上升沿和下降沿都能读写,称为Double data rate。

读

1在读的阶段

DQS由DRAM产生并发送给DDRPHY的控制器,DQS和DQ都和CLK的边沿对齐(edge aligned),然后将数据传给DDRPHY。

依时序从DRAM读出数据传给DDRPHY,在DDRPHY的接收器(Receiver)接收到信号后,会将DQS delay 90°,delay后的DQS边沿和DQ的中心对齐(center-aligned),最后用DQS的上升沿与下降沿来采样数据。

写

在写的阶段

DQS由DDRPHY控制器产生并发送给DRAM,DQS和CLK的边沿对齐(edge aligned),而DQ和CLK是中心对齐的(edge-aligned),DRAM就可以直接用DQS的上升沿和下降沿来采样数据。

这期我们简单介绍了DDR接口的一些实现方式,主要区别以及高速信号的基本读写操作。东芯半导体的DRAM产品都是符合国际接口规范的标品,替换无压力。具体的规格如下,欢迎关注并咨询。

·DDR3(L)

| 密度/Density | 1Gb/2Gb/4Gb |

| 电压/Voltage | 1.5V/1.35V |

| 温度/Temperature | 0℃/-40℃~95℃ |

| 线宽/Bus Width | x8/x16 |

| 速度/Speed | 800Mhz/933Mhz |

| 封装/Package | 78/96ball FBGA |

· LPDDR

| 密度/Density |

LPDDR1 128Mb/256Mb/512Mb/1Gb/2Gb LPDDR2 1Gb/2Gb/4Gb LPDDR4X 1Gb/2Gb |

| 电压/Voltage |

LPDDR1 1.8V LPDDR2 1.8V/1.2V LPDDR4X 1.1V/0.6V |

| 温度/Temperature | -40℃~85℃ |

| 线宽/Bus Width |

LPDDR1 x16/x32 LPDDR2 x16/x32 LPDDR4X x16/x32 |

| 速度/Speed |

LPDDR1 166Mhz/200MHz LPDDR2 400MHz/533MHz LPDDR4X 1600Mhz/1866Mhz/2133MHz |

| 封装/Package |

LPDDR1 60/90ball FBGA/KGD LPDDR2 134ball FBGA LPDDR4X 200ball FBGA |

东芯,为日益发展的存储需求提供高效可靠的解决方案。

关于东芯

东芯半导体以卓越的MEMORY设计技术,专业的技术服务实力,通过国内外技术引进和合作,致力打造成为中国本土优秀的具有自主知识产权的存储芯片设计公司。

-

#硬声创作季 #STM32 手把手教你学STM32-044 待机唤醒实验-低功耗-M4-2水管工 2022-10-29

-

#硬声创作季 #STM32 手把手教你学STM32-044 待机唤醒实验-低功耗-M4-3水管工 2022-10-29

-

低功耗蓝牙怎么低功耗?如何界定2018-02-06 0

-

低功耗加密产品推荐2019-08-01 0

-

低功耗唤醒无线电产品的需求是什么?2021-04-19 0

-

介绍无线通信产品的低功耗设计2021-11-03 0

-

电子产品的低功耗问题2021-11-10 0

-

做低功耗产品主要把握哪几点呢2022-02-23 0

-

STM32L4产品的低功耗特性及应用2023-09-07 0

-

便携式产品具有低功耗意识的FPGA设计方法2009-11-30 696

-

MCU产品如何来实现低功耗2020-03-09 1256

-

美光低功耗DDR5 DRAM芯片助力5G网络2020-04-27 850

-

专为5G和AI设计的低功耗DDR5 DRAM2021-11-11 575

-

MCU低功耗设计(三)产品2021-10-28 549

-

低功耗产品的关键组件是设计师2022-12-29 514

全部0条评论

快来发表一下你的评论吧 !