浅析电源DDR硬件设计技巧

电源/新能源

描述

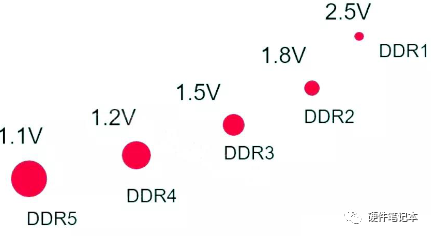

1、电源DDR的分类

A、 主电源VDD和VDDQ

主电源的要求是VDDQ=VDD,VDDQ是给IO buffer供电的电源,VDD是给内核供电。但是一般的使用中都是把VDDQ和VDD合成一个电源使用。

有的芯片还有专门的VDDL,是给DLL供电的,也和VDD使用同一电源即可。

电源设计时,需要考虑电压、电流是否满足要求。

电源的上电顺序和电源的上电时间,单调性等。

电源电压的要求一般在±5%以内。电流需要根据使用的不同芯片,及芯片个数等进行计算。由于DDR的电流一般都比较大,所以PCB设计时,如果有一个完整的电源平面铺到管脚上,是最理想的状态,并且在电源入口加大电容储能,每个管脚上加一个100nF~10nF的小电容滤波。

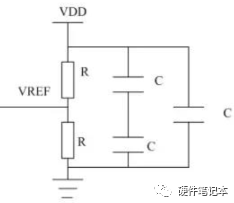

B、 参考电源Vref

参考电源Vref要求跟随VDDQ,并且Vref=VDDQ/2,所以可以使用电源芯片提供,也可以采用电阻分压的方式得到。由于Vref一般电流较小,在几个mA~几十mA的数量级,所以用电阻分压的方式,即节约成本,又能在布局上比较灵活,放置的离Vref管脚比较近,紧密的跟随VDDQ电压,所以建议使用此种方式。需要注意分压用的电阻在100Ω~10kΩ均可,需要使用1%精度的电阻。Vref参考电压的每个管脚上需要加10nF的电容滤波,并且每个分压电阻上也并联一个电容较好。

C、 用于匹配的电压VVT

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2。DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。并且VTT要求电源即可以吸电流,又可以灌电流才可以。一般情况下可以使用专门为DDR设计的产生VTT的电源芯片来满足要求。

而且,每个拉到VTT的电阻旁一般放一个10nF~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。 一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。DDR2的地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T型的结构,所以常常需要使用VTT进行信号质量的匹配控制。

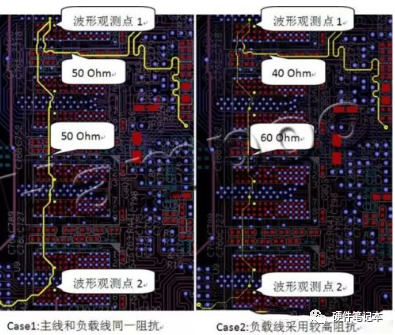

DDR3可以采用Fly-by方式走线: 一个DDR3设计案例,来分析对比采用高阻抗负载走线和采用主线和负载走线同阻抗两种情况的差异。

如上图,Case1采用的是从内层控制器到各个SDRAM均为50ohm的阻抗设计。Case2则采用了主线40ohm,负载线60ohm的设计。对此通过仿真工具进行对比分析。

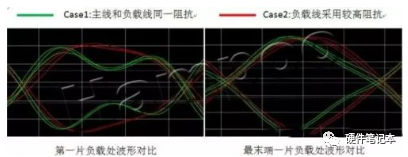

从以上仿真波形可以看出,使用较高阻抗负载走线的Case2在信号质量上明显优于分支主线都采用同一种阻抗的Case1设计。 而且对靠近驱动端的负载影响最大,远离驱动端的最末端的负载影响较小。这个正是前面所分析到的,负载的分布电容导致了负载线部分的阻抗降低,如果采用主线和负载线同阻抗设计,反而导致了阻抗不连续的发生。把负载走线设计为较高的阻抗,用于平衡负载引入的分布电容,从而可以达到整条走线阻抗平衡的目的。 通过提高负载走线阻抗来平衡负载电容的做法,其实在以往的菊花链设计中是经常用到的方法。DDR3称这种拓扑为fly-by,其实是有一定的含义的,意在强调负载stub走线足够的短。

编辑:黄飞

-

DDR系列内存详解及硬件设计规范l2015-11-16 727

-

浅析开关型稳压电源结构原理2012-08-06 0

-

电源滤波电路浅析2013-02-06 0

-

【转帖】一文读懂电源DDR硬件设计要点2018-08-09 0

-

关于计算机的硬件维护的浅析2021-09-08 0

-

浅析高频开关电源的热设计2009-07-15 833

-

UPS电源输入跳闸浅析及解决办法2011-11-10 1069

-

DDR硬件设计要点2015-10-28 656

-

DDR3-硬件设计和-Layout-设计2016-09-09 1862

-

一文轻松让你秒懂DDR硬件设计2018-07-17 19740

-

浅析电源DDR硬件设计要点2018-08-22 4287

-

DDR电源设计,什么是拉电流什么是灌电流?2021-08-18 4243

-

DDR4相比DDR3的变更点2021-11-06 834

-

基于高云半导体FPGA的DDR2/DDR3硬件设计参考手册2022-09-15 345

-

VTT电源对DDR有什么作用?2023-11-27 999

全部0条评论

快来发表一下你的评论吧 !