时钟抖动会影响建立时间和保持时间违例吗?

描述

首先,我们需要理解什么是时钟抖动。简而言之,时钟抖动(Jitter)反映的是时钟源在时钟边沿的不确定性(Clock Uncertainty)。例如,假定我们现在有一个频率为100MHz的时钟,那么时钟周期就是10ns,理想情况下,时钟的上升沿将会出现在0ns,10ns,20ns……基于此,如果已知时钟上升沿出现在30ns,这样我们就可以得出下一个上升沿将会出现在40ns。但实际情况是,下一个上升沿很可能介于39.9ns到40.1ns之间。也就是说,有0.1ns对时钟周期构成了影响。就FPGA设计而言,对于抖动我们理解这么多就足够了。

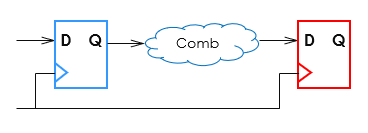

接下来我们看一下时钟抖动对时序性能的影响。以经典的单周期时序路径为例(收发时钟为同一个时钟且建立时间Requirement为一个时钟周期),如下图所示。

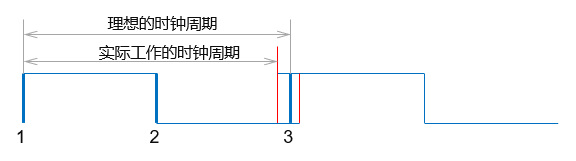

就建立时间而言,基于静态时序分析(STA)理论,假定数据发起沿为下图边沿1,那么捕获沿将是边沿3。如果边沿1出现在20ns这一时刻,那么边沿3可能出现在以下两个时刻:

20+Clock Period+Jitter

20+Clock Period-Jitter

考虑最坏情况,我们应该按照20+Clock Period-Jitter来评估建立时间裕量。换言之,实际的时钟周期为Clock Period-Jitter。

再看保持时间,发起沿和捕获沿都是边沿1,或都是边沿3,即发起沿和捕获沿是同一时钟的同一个上升沿,故抖动不会对保持时间裕量产生影响。

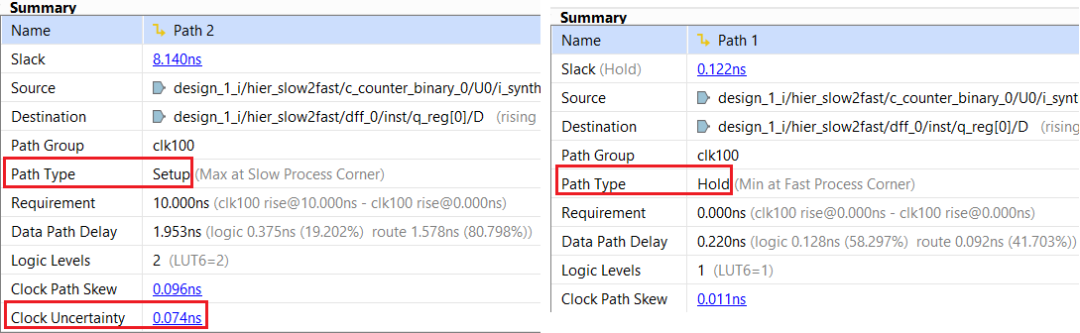

基于此,我们可以得出如下结论:对于发送时钟和接收时钟是同一时钟的单周期路径,时钟抖动对建立时间有负面影响,但对保持时间没有影响。这一点,在Vivado的时序报告中也可以看到。如下图所示,图中左侧为建立时间时序报告,可以看到Clock Uncertainty,而右侧为保持时间时序报告,是没有Clock Uncertainty。

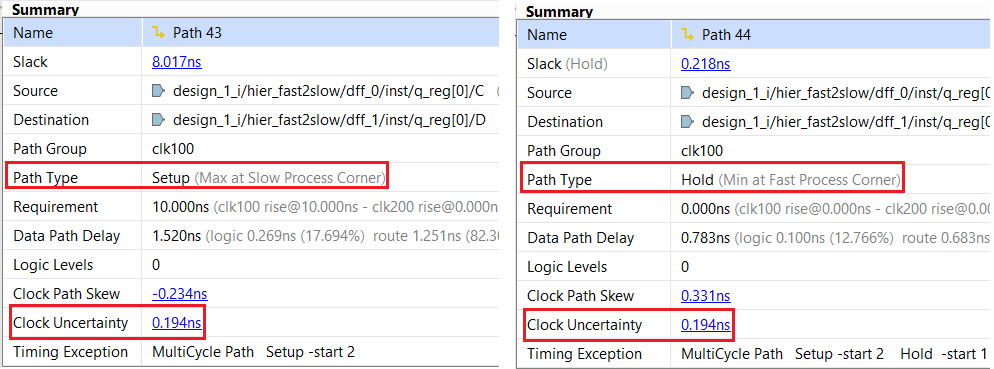

如果发送时钟和接收时钟是不同时钟呢?假定发送时钟为200MHz,接收时钟为100MHz,两者由同一个MMCM生成,故二者为同步时钟。两者之间的跨时钟域路径可采按多周期路径进行约束。毋庸置疑,抖动仍然会对建立时间有负面影响。对于保持时间,发起沿是200MHz时钟的上升沿,捕获沿是100MHz的上升沿,不是同一个边沿,故要将100MHz的时钟抖动考虑在内。

根据保持时间的定义:数据被时钟有效沿采样到之后仍要稳定保持一段时间,这个时间即为保持时间。考虑最坏情况,抖动使得时钟采样沿后移,意味着数据需要保持更长的时间即Th+Jitter。因此,此时,抖动对保持时间也是一种恶化。这一点在Vivado的时序报告中也会有所体现。

审核编辑:刘清

-

数字电路中,建立时间和保持时间对于触发器的时钟信号有2012-01-27 0

-

什么叫建立时间,保持时间,和恢复时间2017-04-08 0

-

为什么触发器要满足建立时间和保持时间2021-09-28 0

-

静态时序之建立时间和保持时间分析2022-08-22 3408

-

建立时间和保持时间讨论2015-03-10 0

-

FPGA实战演练逻辑篇51:建立时间和保持时间2015-07-17 0

-

保持时间与建立时间2018-11-29 0

-

数字 IC 笔试面试必考点(9)建立时间以及保持时间 精选资料分享2021-07-26 0

-

芯片设计进阶之路—从CMOS到建立时间和保持时间2023-06-21 998

-

数字IC设计中的建立时间和保持时间2023-06-21 1272

-

到底什么是建立时间/保持时间?2023-06-27 5895

-

FPGA时序分析-建立时间和保持时间裕量都是inf怎么解决呢?2023-07-30 748

-

SOC设计中的建立时间和保持时间2023-08-23 444

-

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量2023-09-04 423

-

浅析D触发器的建立时间和保持时间物理含义2023-12-04 456

全部0条评论

快来发表一下你的评论吧 !