高质量VerilogHDL描述方法

电子说

描述

刚刚初学VerilogHDL的时候,感觉语言风格很像C语言,编程也是完全用软件的思想去写,但是使用过FPGA和学习了数集之后,才醒悟出何为“硬件思想”,本节主要介绍一下西交邱志雄老师一门课中的VerilogHDL描述方法。

VerilogHDL可综合的四大法宝:always、if-else、case、assign ,本文将围绕这四大法宝来讲述。

有可综合的法宝,那么可综合风格禁止出现的情况:function、for、fork-join、while等。

** If-else的硬件映射及优化**

01

if-else的映射硬件结构是多路选择器Multiplexing Hardware(简称Mux)。

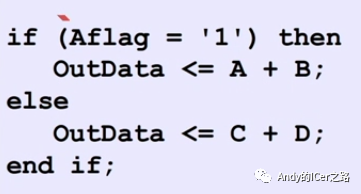

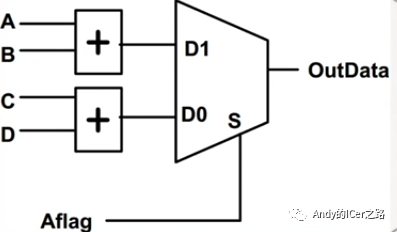

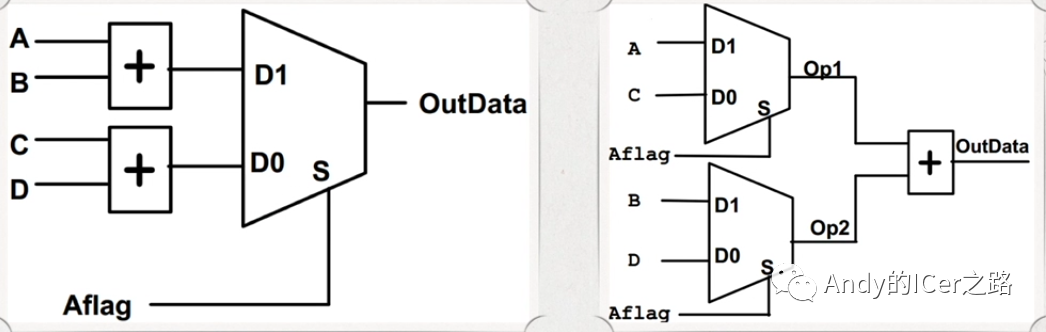

我们来看看上面的第一段代码,我们心中要出现该代码描述的电路,该电路由两个加法器和一个Mux组成。

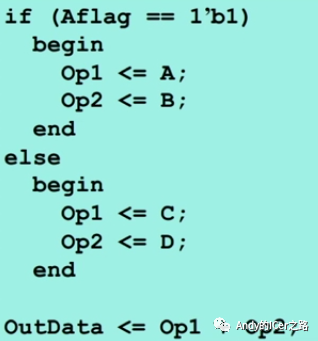

接下来我们看第二段代码:

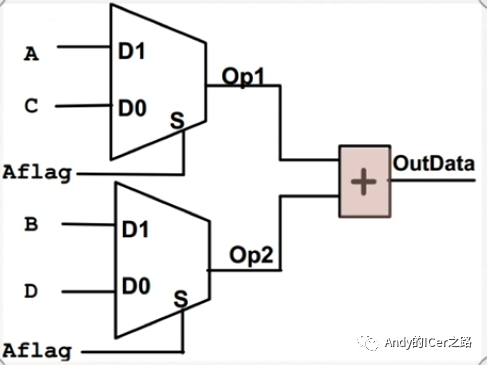

该段代码描述的电路应该是两个Mux和一个加法器组成:

两段代码描述的功能都一样,但是电路面积却不一样,第二段代码描述的电路少了一个加法器多了一个Mux,在同一个工艺库下,二输入Mux的晶体管数量比一位半加器少,因此第二段代码描述的电路减少了硬件的面积。

从面积的角度看,第二段代码更优,但是真的可以说第二段代码比第一段代码好吗?很显然,一般这么问,答案都为否定。

我们从传播延迟的角度再来分析一下这两个电路:

1、左图的数据通道的延迟是一个加法器和一个Mux,控制通道的延迟是一个Mux。

2、右图的数据通道的延迟依然是一个加法器和一个Mux,控制通道的延迟却是一个加法器和一个Mux。

很显然第二段代码描述电路(右图)的控制通道延迟比较大,如果Aflag到来的延迟比较晚的话,那么第二种电路的性能就会比第一种差。

综上所述,在设计的时候要根据输入约束,再来选择两种不同的设计:是先加后选,还是先选后加。

** If的优先级问题**

02

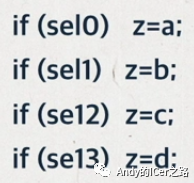

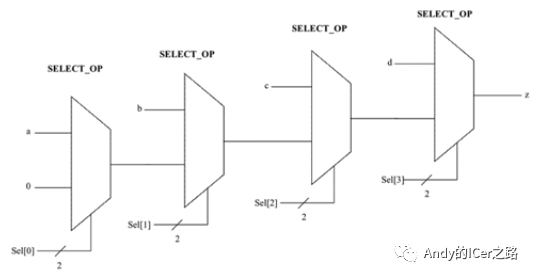

多if语句具有优先级的判断结构,即输入信号是有不平等关系的,最后一级选择信号具有最高优先级,具有优先级的多选结构会消耗组合逻辑,而且这种写法比较乱,一般不推荐这种写法。(case语句是无优先级的)

但是在某些设计中,有些信号要求先到达(如关键使能信号、选择信号等),而有些信号需要后到达(如慢速信号、有效时间较长的信号等),此时则需要用if...if... 或者 if...else if...结构,一般最高优先级给最迟到的关键信号。

电路之大敌——Latch

03

latch由电平触发,非同步控制,所以非常 容易产生毛刺(glitch) ,这是很大的危害,这对于下一级电路是极其危险的,而且静态时序分析会变得极为复杂,因此只要能用D触发器的地方就不用latch。

易引入latch的途径:使用不完备的条件判断语句,如if缺少else,case缺少default。

逻辑复制 均衡负载

04

通过逻辑复制,降低关键信号的扇出,进而降低该信号的传播延迟,提高电路的性能。

资源共享 减小面积

05

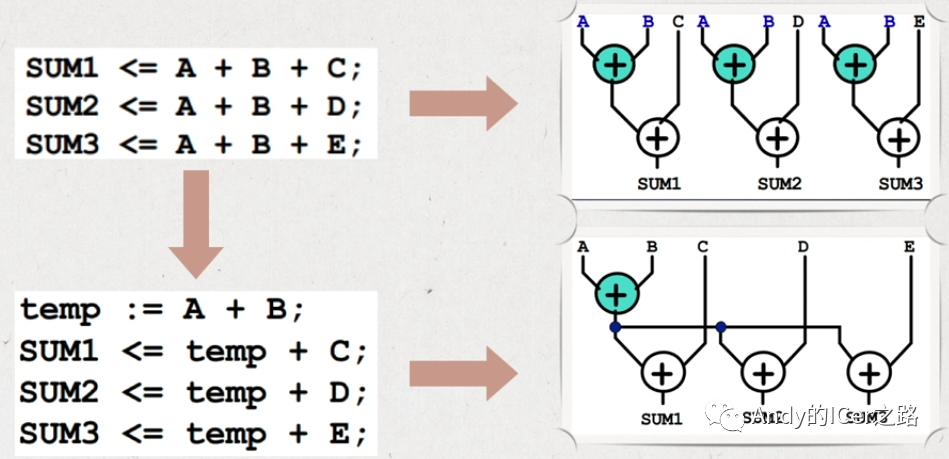

如果电路中存在较多的公共单元,可以通过资源共享,来减小电路的面积,但是一般来说,共享会降低电路性能,所以还是要根据性能和面积而进行取舍。

逻辑重组 降低延时

06

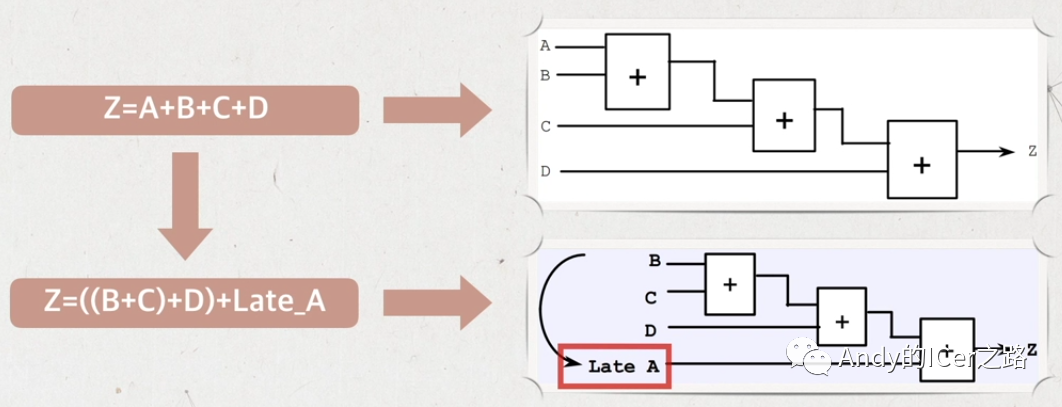

在电路设计中,可以根据信号的延时,对这些资源进行顺序的重排,以降低传播延时。如下图所示,信号A延迟比较高,可以把它尽可能地放到后面隐藏其延迟。

逻辑赋值

07

在时序电路中必须使用非阻塞赋值(<=), 组合逻辑电路必须使用阻塞赋值(=)。

-

protel输出高质量gerber2011-12-12 0

-

高质量C编程指南—林锐2012-08-03 0

-

高质量C++、C编程指南2012-08-06 0

-

高质量C&C++2012-08-16 0

-

高质量C++&C 编程指南2012-08-19 0

-

原版PIC实战项目-C(高质量PDF版本)2013-07-10 0

-

高质量C语言编程2013-07-22 0

-

编写高质量C语言代码2013-07-31 0

-

林锐《高质量C语言编程》2013-08-17 0

-

高质量C++与C编程指南2014-03-09 0

-

高质量编程2016-02-27 0

-

图书推荐:高质量C++编程指南2016-06-12 0

-

【下载】高质量干货-22本高质量EMC电磁兼容性设计资料2020-03-20 0

-

请问怎么才能设计出高质量的印制线路板?2021-04-23 0

-

高质量的c编程指南2017-10-26 757

全部0条评论

快来发表一下你的评论吧 !