RAM/ROM存储器的设计

存储技术

描述

随机访问存储器(RAM)

01

(1)随机访问存储器(RAM)概述

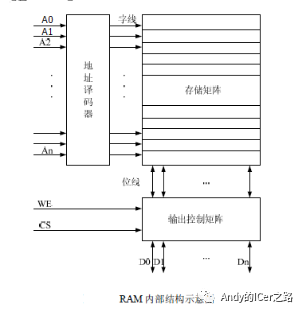

①随机存储器可以随时从任何一个指定地址中读出数据,也可以随时将数据写入任何一个指定的存储单元中,RAM的结构如下:

②RAM 单元根据地址总线、数据总线以及读写控制线的数目可以分为单口RAM、双口RAM 两大类:

单口RAM只有一套数据总线、地址总线和读写控制线,因此当多个外设需要访问同一块单口RAM 时,需要通过仲裁电路来判断。

双口RAM具有两套完全独立的数据线、地址线和读写控制线,从而实现了大量数据的高速访问以及不同时钟域的数据交换。

(2)随机存储器设计基础

①在Verilog HDL 中,若干个相同宽度的向量构成数组,其中reg 型数组变量就代表着存储器。例如:

reg [7:0] memory[1023:0];

该语句定义了1024 个字的存储器变量memory,每个字的字长为8 位,(说白了,就是有1024个8bit宽的寄存器)经过定义后的memory 型变量可以用下面的语句对存储器单元赋值:

memory [7] = 90;

//存储器memory 的第7 个字被赋值为90

②存储器单元中的数据也可以读出,因此存储器型变量相当于一个RAM。由于存储器由逻辑资源产生,因此存储容量越大,所需要的逻辑资源就越多。

(3)单口RAM 单元的实现

①单口RAM,只有一套地址总线,读和写是分开(至少不能在同一个周期内完成)。8× 8 位RAM 的设计举例实现如下:

②部分信号说明:

addm 为3 比特地址线,可以实现8 个存储单元的寻址;

cs_n 为片选信号,低有效,当cs_n 为低时,存储器处于工作状态(可以读或写);当cs_n 为高时,存储器处于禁止状态(强制输出0)。

we_n 为写使能信号,低有效,当we_n为高时,存储器处于读状态,否则处于写状态。

dout 为存储器的输出端口,din 为存储器的输入端口。

module ram_single(

input clk,

input [2:0] addm,

input cs_n,

input we_n,

input [7:0] din,

output reg [7:0] dout

);

reg [7:0] ram1[7:0];

always @(posedge clk) begin

if(cs_n)

dout <= 8'b0000_0000;

else

if(we_n)

dout <= ram1[addm];

else

ram1[addm] <= din;

end

endmodule

(4)双口同步RAM 单元

①双口同步RAM 具有两套地址总线,一套用于读数据,一套用于写数据,二者可分别独立操作。128× 8 位双口RAM 的实现举例:

②代码如下所示:

module rom_test(

output reg [7:0] q,

input [7:0] d,

input [6:0] addr_in,

input [6:0] addr_out,

input we, clk1, clk2

);

reg [6:0] addr_out_reg;

reg [7:0] mem[127:0];

always @(posedge clk1)begin

if (we)

mem[addr_in] <= d;

end

always @(posedge clk2) begin

q <= mem[addr_out_reg];

addr_out_reg <= addr_out;

end

endmodule

只读存储器(ROM)

02

①在数字系统中,由于ROM 掉电后数据不会丢失,对于容量不大的ROM,在Verilog HDL 中可以通过case 语句来实现。

②在应用中,case 语句中的数值可以根据实际需要修改,其中addm 为地址输入信号,cs_n为片选信号,8× 8 位的ROM 模块的实现:

module rom_test(

input clk,

input [2:0] addm,

input cs_n,

output reg [7:0] dout

);

always @(posedge clk) begin

if(cs_n)

dout <= 8'b0000_0000;

else

case(addm)

3'b000: dout <= 1;

3'b001: dout <= 2;

3'b010: dout <= 4;

3'b011: dout <= 8;

3'b100: dout <= 16;

3'b101: dout <= 32;

3'b110: dout <= 64;

3'b111: dout <= 128;

endcase

end

endmodule

-

存储器的分类介绍 各种存储器功能分类大全2017-12-21 0

-

存储器 IC 分类的纠结2012-01-06 0

-

ROM程序存储器2021-07-13 0

-

内存(RAM或ROM)和FLASH存储的区别2021-07-30 0

-

存储器的ram和rom分类2022-01-26 0

-

80C51单片机中存储器是RAM和ROM分开编址的吗?2023-05-09 0

-

ROM、RAM、DRAM、SRAM和FLASH的区别2017-12-04 1941

-

对ROM和RAM以及FLASH存储器的详细解析2018-01-19 10599

-

ram和rom的区别之处2020-05-10 2924

-

如何区分各种存储器(ROM、RAM、FLASH)2020-12-17 10710

-

聊聊RAM和ROM2023-02-15 1959

-

手机上的ROM和RAM技术原理2023-03-30 2032

-

ROM与RAM的主要区别 存储器rom的功能是什么2023-06-20 2298

-

随机访问存储器(RAM)和只读存储器(ROM)的区别2023-12-05 936

-

rom与ram的主要区别 rom断电后数据会丢失吗2024-01-25 956

全部0条评论

快来发表一下你的评论吧 !