如何在Post Synthesis工程中加入XCI文件

描述

本文作者:AMD 赛灵思工程师 Hong Han

当使用第三方综合器比如 Synopsys Synplify Pro 或 Mentor Graphics Precision 来综合包含 AMD Xilinx IP 的设计时,UG896 推荐的方式是创建并定制 IP,生成这些 IP 的 output product (包括 IP 的 dcp);然后把第三方生成的网表文件和 IP XCI 的相关文件都加到 Vivado 的 post-synthesis 工程中。

此时第三方综合器只是综合用户的 RTL 代码,IP 代码的综合实际还是由 Vivado 完成,然后在新的 Vivado 工程中把这些 IP 的网表和第三方综合器生成的顶层网表合并(在 Vivado 中的 link_design 步骤实现)。

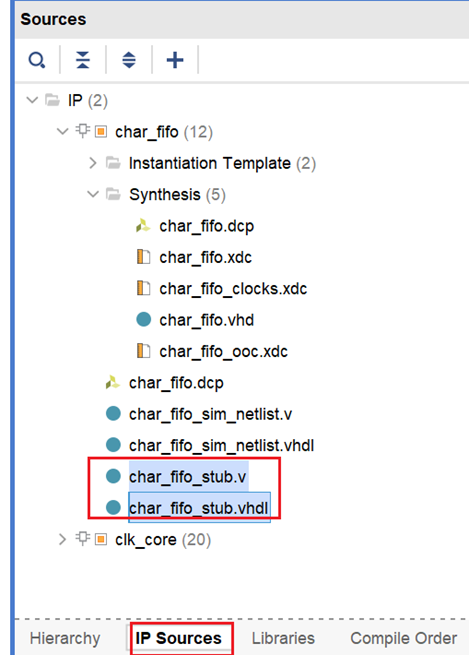

第三方综合器由于并不实际综合 IP 的代码,在第三方综合器综合的过程中,只需要提供 IP 的黑盒文件,让第三方综合器了解 IP 模块的接口即可,生成 IP output product 时得到的 stub 文件就是黑盒文件(_stub.v /_stub.vhdl)。

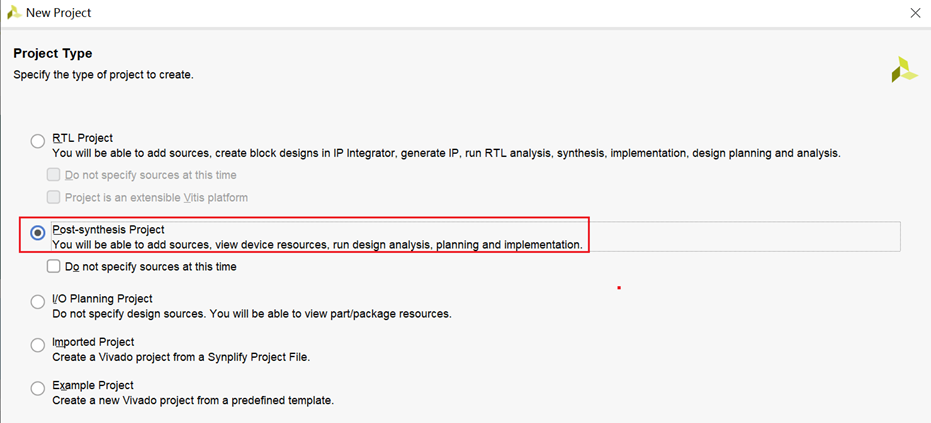

以下是在 GUI 下创建 Post-synthesis 工程的界面:

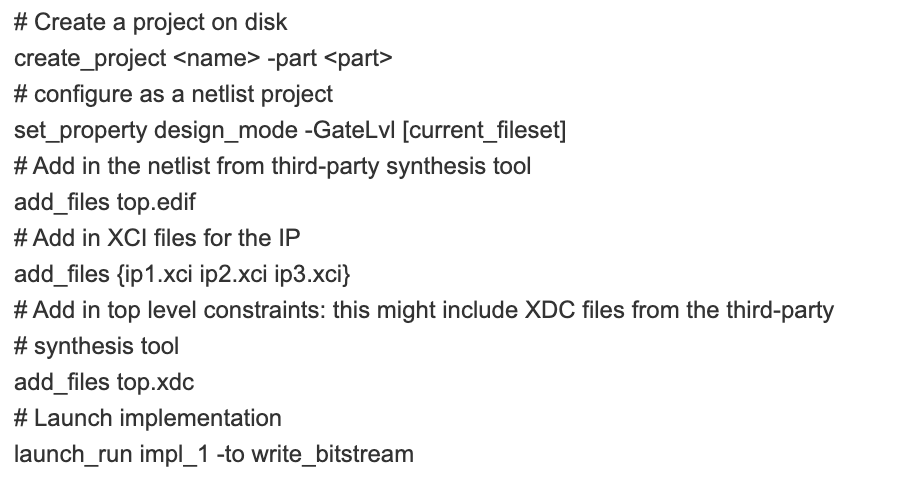

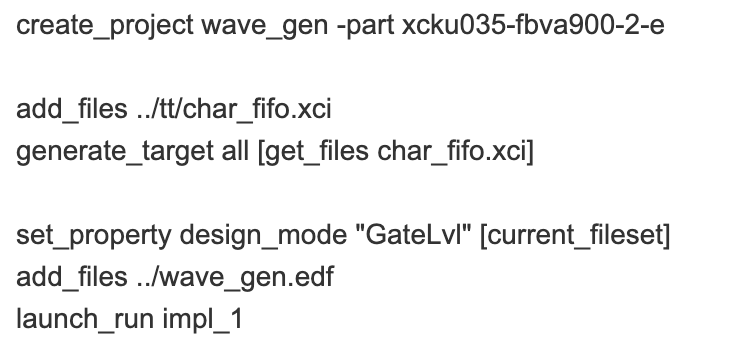

UG896 中提供的示意 Tcl 脚本如下:

在 Vivado 2022.2,尝试使用以上的脚本编译一个例子工程看看是否会遇到困难。

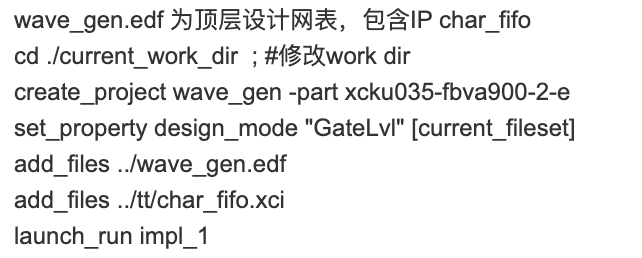

实验使用的脚本如下:

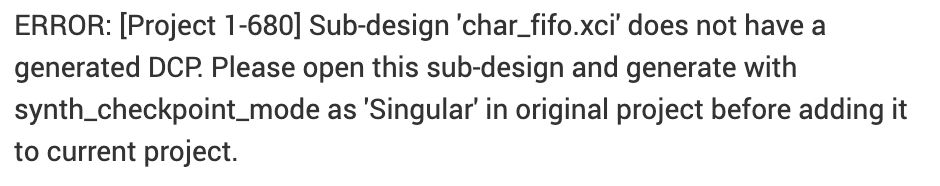

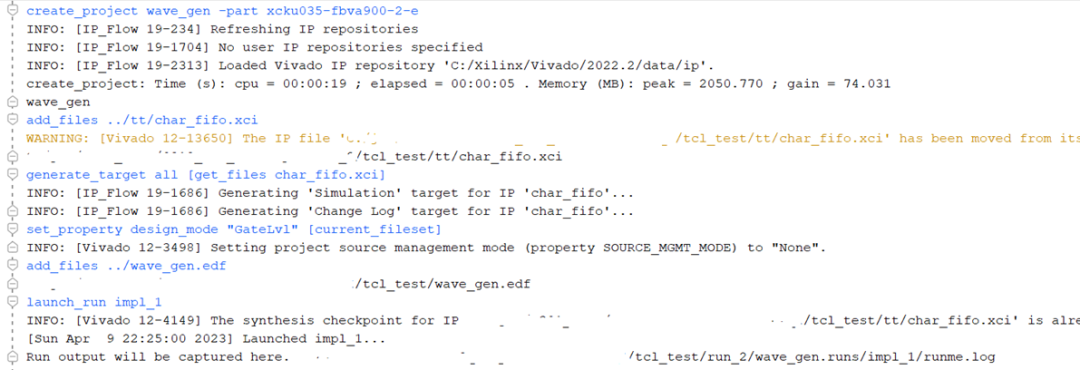

结果 IP char_fifo 没能加到新的工程中,并报出以下的错误:

之所以报错的原因是为了新建工程,我们移动了 IP 的 XCI 文件,但是却没有移动 IP 原来生成在 gen 目录的 output product。

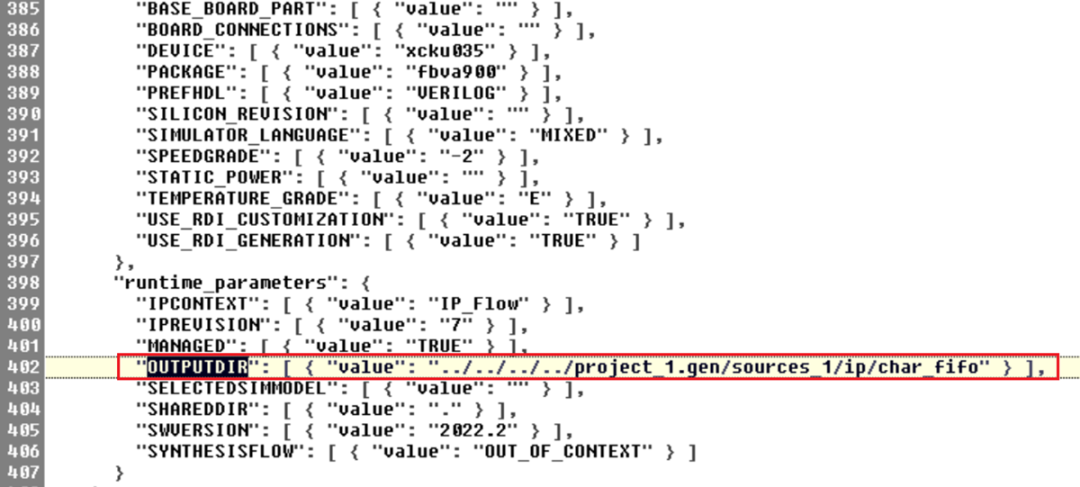

直接用第三方编译器打开 XCI 文件,查看 outputdir。这是之前的 output product 所在的目录相对于 XCI 文件的目录。

在这里我们尝试手动修改一下 outputdir,改成当前 IP 的 output product 所在的目录 "OUTPUTDIR": [ { "value": "../char_fifo" } ],同时把原来工程中生成的 output product 复制到这个目录中。

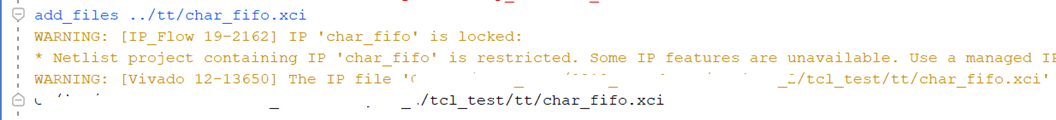

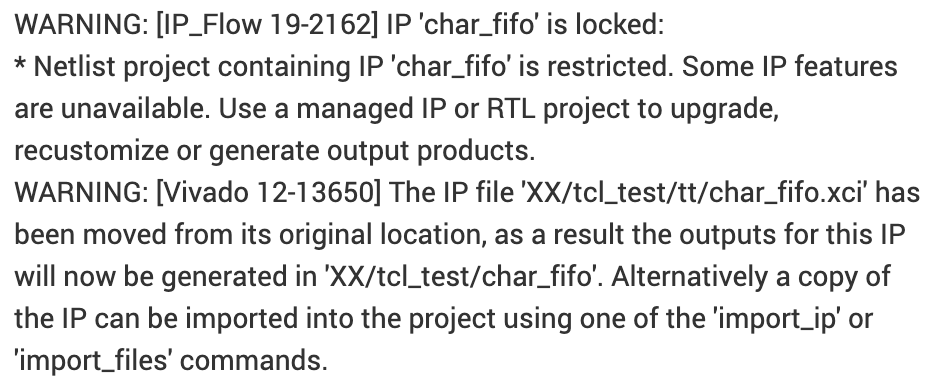

在 Vivado TCL CONSOLE 中重新运行一下加 XCI 文件的命令,可以看到以下输出:

这里可以看到 XCI 文件已经加到工程中,同时看到的 warning 是正常的,提醒用户在 post-synthesis 工程中,IP 是锁定的,无法修改。

在一些早期的 Vivado 版本中(Vivado 2022.2没有这个问题),即使 IP XCI 文件中 OUTPUTDIR 所指向的目录的确是 IP output product 存放的目录,依然会报 ERROR: [Project 1-680]。这里给大家介绍一下如何微调脚本解决这个问题。

新的脚本:

这里差异在于在新工程设置为 post-synthesis 工程之前,先读入 XCI 文件并重新生成 IP 的 output product。这样就不必修改 XCI 文件的 OUTPUTDIR 去指向之前 output product 的目录。

使用 tcl 命令生成的工程文件 .xpr 文件可以在 Vivado 界面直接打开(File -> Project -> Open)。

-

STM32程序HEX文件中加入固件版本信息2022-08-14 3959

-

请教各位大侠如何在protel99中加入图片或公司LOGO2012-11-26 0

-

如何在cadence中加入中文丝印2012-12-21 0

-

如何在protues元件库中加入AD7755?2013-04-18 0

-

【求助】labview图像显示中加入标签的问题2016-04-22 0

-

IO Planning (PlanAhead) post-synthesis时报错2018-12-20 0

-

如何在根文件系统中加入ssh命令?2019-10-24 0

-

请问如何在SoC设计中加入音频处理功能?2021-06-03 0

-

华大单片机是如何向MDK中加入头文件和库文件的2021-07-13 0

-

请问如何在RTTHREAD STUDIO 中加入W601 MCU?2023-02-22 0

-

Protel在线教程:如何在PCB文件中加汉字2010-04-22 4061

-

Vivado技巧:.dcp 文件代替 .xci 文件2018-05-02 4823

-

如何在XHTML网页中加入CSS详细的五种方式说明2019-06-13 755

-

赛灵思建议:使用IP xci文件代替dcp格式的文件2019-07-27 3520

-

华大单片机如何向MDK中加入头文件和库文件2021-11-23 555

全部0条评论

快来发表一下你的评论吧 !