哈佛结构和冯诺依曼结构的区别

处理器/DSP

描述

0. 前言

哈佛结构和冯诺依曼结构都是针对于CPU来说的。

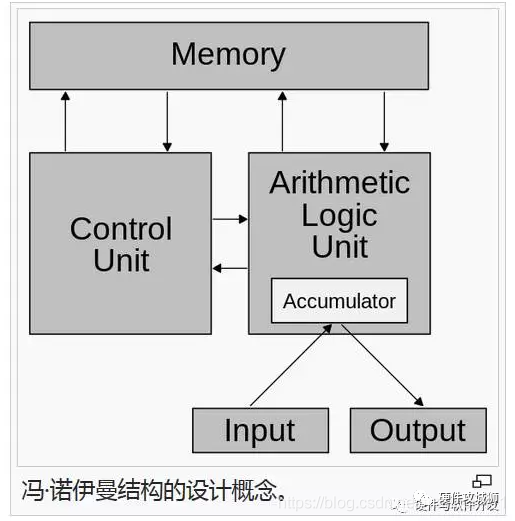

1. 冯诺依曼结构

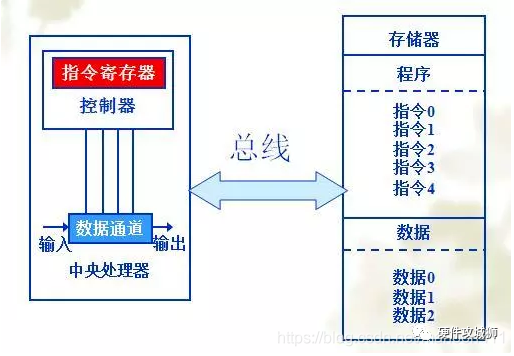

冯诺伊曼结构又称为普林斯顿体系结构,是一种将程序存储器和数据存储器合并在一起的处理器架构设计,使用同一个存储器,经由同一个总线传输。由于取指令和存取数据要从同一个存储空间存取,并经同一总线传输,无法重叠执行,只能step by step,因此影响了数据处理速度的提高。冯诺伊曼结构处理器具有以下特点:

必须有一个存储器;

必须有一个控制器;

必须有一个运算器(算术运算与逻辑运算);

必须有输入输出设备(人机通信)。

冯诺依曼结构中不独立区分程序和数据空间,处理器只有一套总线,即程序和数据空间共用地址和数据总线,取指令和取数据不能同时进行。

早期的微处理器大多采用冯·诺依曼结构,如:英特尔公司的8086,英特尔公司的其他中央处理器,ARM的ARM7,MIPS公司的MIPS处理器。其中,典型代表是Intel公司的X86微处理器,广泛用于桌面端(台式/笔记本/服务器/工作站等)。

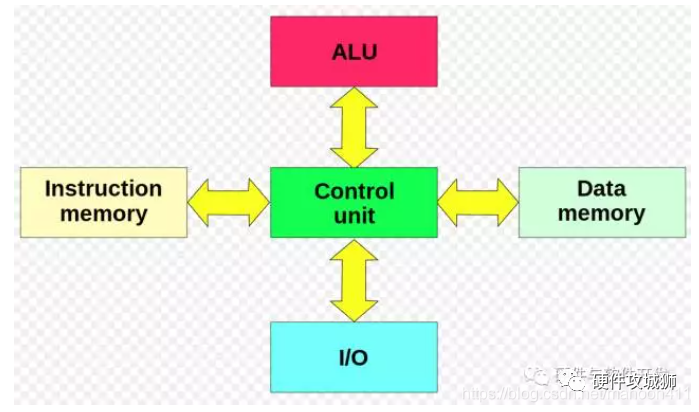

2. 哈佛结构

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构,数据和指令的储存可以同时进行,可以使指令和数据有不同的数据宽度,例如Microchip公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度。哈佛结构处理器具有如下特点:

程序存储器与数据存储器分开。

提供了较大的存储器带宽,各自有自己的总线。

适合于数字信号处理。

哈佛结构的出现是为了减轻程序运行时的访存瓶颈,哈佛架构的微处理器通常具有较高的执行效率。其程序指令和数据指令分开组织和储存的,执行时可以预先读取下一条指令。

哈佛结构中程序空间和数据空间是独立的,具有各自独立的地址线和数据总线,即处理器有两套总线,一套是程序存储器的数据和地址总线,一套是数据存储器的数据和地址总线。取址和取数据能并发进行。

目前使用哈佛架构的中央处理器和微控制器有很多,有 Microchip公司的PIC系列芯片、摩托罗拉公司的MC68系列、Zilog公司的Z8系列、Atmel公司的AVR系列和ARM公司的ARM9、ARM10和ARM11,自ARM11以后,ARM公司的内核均以Cortex命名。

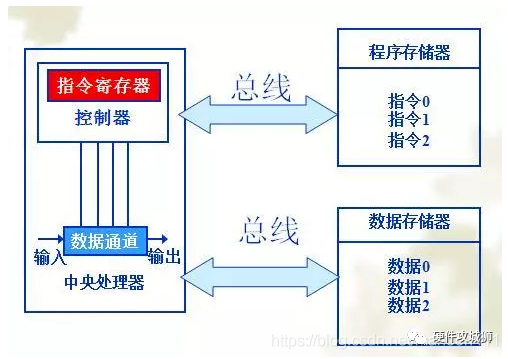

3. 改进的哈佛结构

改进的哈佛结构使用两个独立的存储器模块(程序存储器和数据存储器),处理器只有一套总线,分时访问程序存储器和数据存储器,但是在处理器中有指令cache和数据cache将程序和数据分开(冯诺依曼结构中没有指令cache和数据cache),所以处理器仍然可以并步执行取指令和取数据,从这点看处理器仍然属于哈佛结构。

改进型哈佛结构是在普通哈佛结构的基础上加上独立的缓冲区cache, 虽然处理器只有一套总线,但由于cache的存在,CPU直接访问的是cache,而cache又分为指令cache和数据cache,这两个cache是独立的,所以可以同时访问指令和数据,也就是说能够并行运行。

从ARM9开始以后所有的ARM处理器内核都是改进型的哈佛结构。

4. 总结

哈佛结构和冯诺依曼结构的主要区别就是处理器能不能实现取指令和取数据的并发进行,程序空间和数据空间是否是一体。

冯·诺依曼结构:冯·诺依曼结构中,取指令与取操作数都在同一条总线上,总线结构简单,所以成本也低,早期该结构的处理器能迅速抢占市场。但也是因为取指令与取操作数都在同一条总线上,只能通过分时复用进行,所以在高速运行时,不能达到同时取指令与取操作数,从而造成传输过程的瓶颈。

哈佛结构:哈佛结构具有复杂而又强大的总线结构,其芯片内部程序空间和数据空间是分开的,可以同时取指令与取操作数,数据吞吐率高,运算速度更快。但是设计实现复杂,成本较高。

改进型的哈佛结构:改进型的哈佛结构结合了两者的长处,将其融合到一起,实现了优化。

编辑:黄飞

-

冯诺依曼和哈佛结构的比较2012-08-20 0

-

冯诺依曼体系结构和组成2019-06-11 0

-

冯·诺依曼体系和哈佛总线体系的区别是什么2020-07-08 0

-

你的CPU属于哈佛结构还是冯诺依曼结构?2021-05-11 0

-

单片机工作笔记002---认识CPU的结构_哈佛结构和冯·诺依曼结构的区别 精选资料推荐2021-07-15 0

-

浅析冯·诺依曼体系结构2021-09-16 0

-

基于哈佛结构的Flash介绍2021-11-03 0

-

介绍嵌入式微处理器体系结构冯诺依曼结构2021-12-17 0

-

冯·诺依曼计算机体系结构缺陷有哪些?2021-12-24 0

-

哈佛结构和冯诺依曼结构的差别是什么?2021-12-27 0

-

冯诺依曼计算机体系结构是怎样组成的2022-02-10 0

-

单片机中哈佛结构和冯诺依曼结构的区别是什么?2023-10-28 0

-

简单介绍哈佛结构和冯·诺依曼结构的区别2017-11-13 47342

-

单片机工作笔记002---认识CPU的结构_哈佛结构和冯·诺依曼结构的区别2021-11-15 424

-

CPU中哈佛结构和冯诺依曼结构的区别2023-02-03 4521

全部0条评论

快来发表一下你的评论吧 !