改善带有ECC奇数负载的DDR2信号质量的方法

存储技术

描述

01

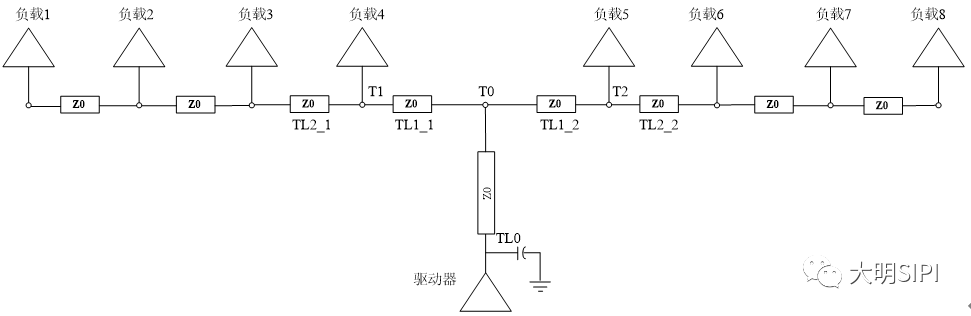

树型拓扑信号质量的改善

这里介绍两种方式改善带有ECC的奇数负载的DDR2信号质量。一种不需要改变拓扑结构,另一种需要对拓扑结构进行调整。

方法一:拓扑结构不变,直接在驱动端加一个10pF电容到地

既然负载9放在拓扑中间,受反射影响而边沿不单调。究其原因和驱动器的上升沿太快有关系。那么我们就在驱动器端加一个15pF左右的电容到地,使输出信号的上升沿变缓一些,有可能将回沟消除。

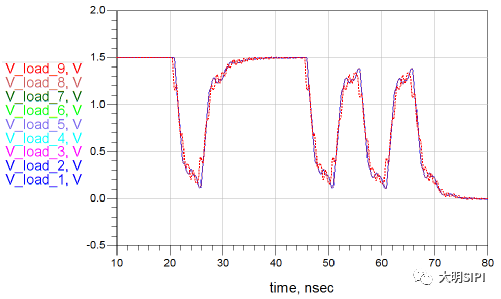

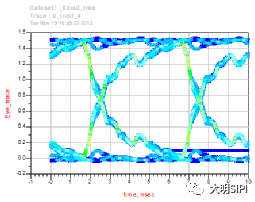

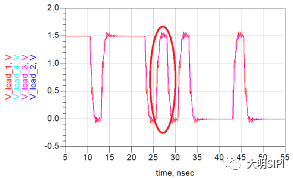

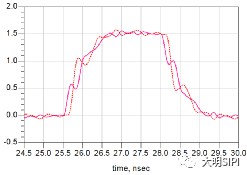

上图所示为在驱动端增加电容后的9个负载的仿真波形,可以看到负载9上的回沟明显减小,使信号的有效位宽明显增大。但是也需要注意:

(1)虽然增加电容消除了负载9边沿的回沟,但是电容也带来了一定的高频分量的衰减,这有可能会加重码间干扰(ISI)。

(2)这种方式有助于改善信号质量,但是由于每个地址、命令线都增加了一个电容占用了额外的布局空间,在布局紧张的情况下无法使用。

方法二:调整负载9在拓扑结构中的位置

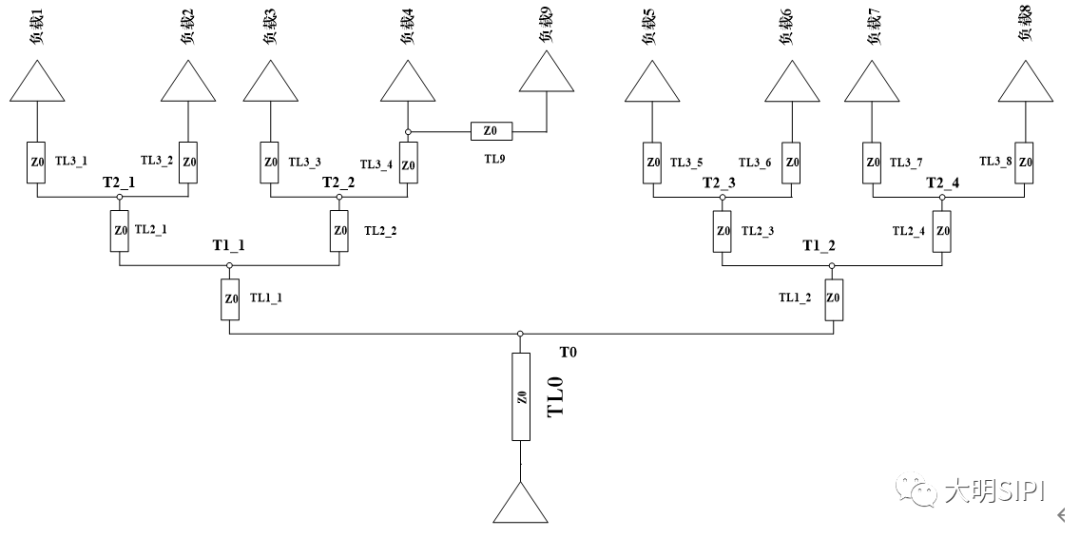

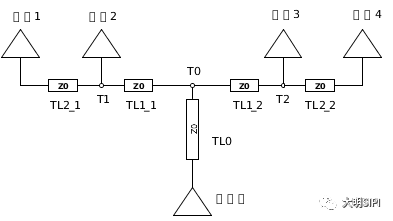

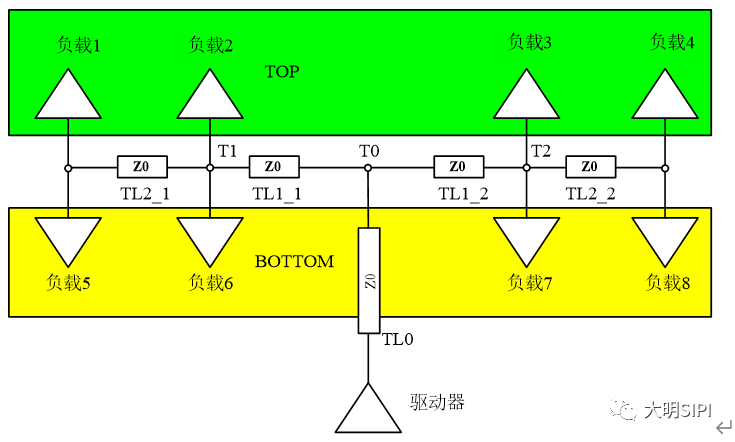

既然第一个分支点T0处受反射影响最大,那我们就选择一个受反射影响小的点将ECC芯片挂在这个地方就可以了。我们将负载9放在负载4(或者负载5)所在的分支上,从负载4(或者负载5)的fanout过孔处再引出一段线接到负载9即可,这样同样布局也不需要调整,而且对布线也没有太大的影响。更改后的拓扑如下所示:

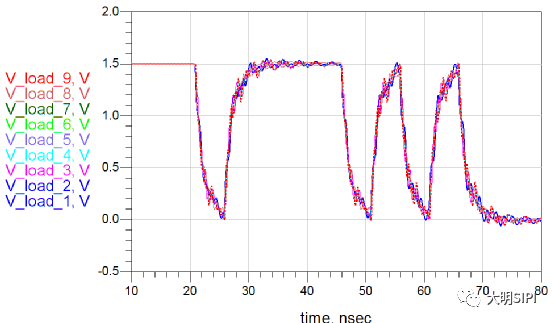

这种拓扑带来的好处就是所有负载都远离了T0点,受其反射的影响比较小了。但是另一方面也导致了整个拓扑的对称性受到破坏,波形的一致性有所降低。受到影响最大的应该是负载4。但从仿真结果来看这个影响是比较小的。

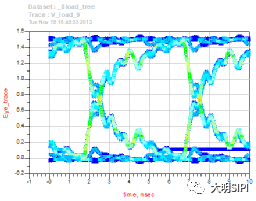

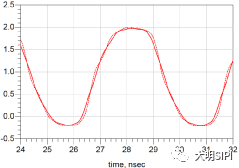

图7.(左)负载9的接收眼图;(右)负载4的接收眼图

从仿真结果来看,调整拓扑后的负载9的接收波形要比将ECC挂在T0点上有了很大的改善,同时负载4的信号质量并没有很大的恶化。但是负载9的边沿还存在着一些回沟和振铃,但对时序和噪声余量的影响已经降低。

这两种方法都可以解决负载9边沿的回沟反射问题,设计的时候可以根据实际情况灵活选择。总之对于多负载的DDR接口、尤其是带ECC的DDR接口,地址控制信号的拓扑必须通过精细的仿真分析来确定,否则很可能导致设计失败或者ECC功能无法使用。

另外需要注意的就是驱动器的驱动能力到底能带多少负载我们在设计之初必须有一个大体的估计。上面的例子中驱动器本身输出的上升下降时间都是260ps左右的,当带8(9)个负载之后边沿明显变缓了甚至达到2ns以上。因此,我们必须在设计开始时就充分地考虑到整个系统的总的容性负载有多大,包括所有的布线、过孔以及负载的容性效应。这样才能估算出容性负载会对上升下降时间产生什么样的影响。对于一定速率的信号来说,当信号的上升下降时间超过或者接近一个信号位宽之后就会是码间干扰加重并极大的影响信号的噪声和时序裕量,此时我们就需要增加驱动器的驱动能力或者降频设计、或者更改设计方案减少负载数量。

还有就是对于多负载情况的树型拓扑匹配方式只可能使用源端匹配或者不添加任何匹配器件。因为戴维南匹配加在拓扑的最末段才会起到良好的匹配效果,但是由于拓扑中存在非常多的分支匹配加在哪里好像都不太合适。也有的设计中将戴维南匹配加到第一个分支点T0处,这样也能起到一定的效果毕竟可以抑制反射最严重的点的阻抗不连续。当然最终还是需要通过仿真来确定。

02

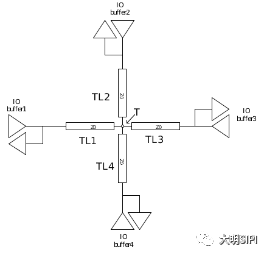

T型拓扑介绍

T型拓扑也是一种对称性非常好的拓扑,它可以看作是两个菊花链的组合,也可以看作是树型拓扑的简化,4个负载的T型示意图如下所示。

T型拓扑具有如下特点:

(1)相对于树型拓扑而言其布线要简单很多,TL1_1/2、TL2_1/2这几段横向布线理想情况下(负载fanout设计合理)可以一层完成。在DDR接口的设计中地址控制信号采用这种拓扑TL1_1/2、TL2_1/2这几段布线可以和部分数据信号共用布线层,TL0布线也可以和数据信号共用布线层。这种拓扑对于降低信号线布线层数很有帮助。

(2)具有树型拓扑对称性的特点,负载1和4以及负载2和3分别对称波形也具有一定的一致性给信号完整性仿真带来方便;

(3)T型拓扑相当于两个菊花链组合在一起,靠近发送端的负载可能会存在回沟、台阶导致信号边沿不单调影响时序裕量。

我们在ADS中搭建DDR2地址信号的仿真电路进行分析。驱动器为Virtex-4的SSTL buffer上升时间600ps、下降时间800ps。负载为美光DDR2芯片MT47H128M4CF。对拓扑结构中的线长做如下设置:(1)TL0=2000mil,(2) TL1_1\\TL1_2长度为500mil;(3)TL2_1~TL2_2长度为700mil;仿真速率400MHz。

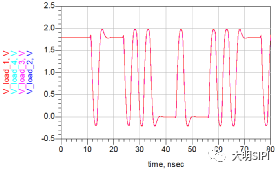

负载1和4(点虚线)以及负载2和3(实线),从上面的仿真结果可以看出4个负载的接收波形基本上一致,这是由于DDR2本身的上升下降时间并不是很快。将驱动器更改为上升下降时间为260ps的1.5V DDR3驱动器后仿真结果如下所示:

仿真结果显示负载1和4(点虚线)以及负载2和3(实线)的接收波形边沿都存在着回沟。因此,这种T型的拓扑结构通常只是应用于相对低速的DDR和DDR2接口,对于更高速率的DDR3接口这一回沟将会显著影响信号的时序裕量。即便是在DDR2接口中应用,在533MHz、667MHz情况下也需要妥善解决回沟和边沿的问题。

当拓扑中存在更多负载的情况下我们是否还可以使用T型的拓扑呢?答案是肯定的。实际上我们可以采取的方式很多,下面以8颗DDR2芯片的地址控制信号为例简单介绍几种处理办法:

Ø正反对贴布局

八片DDR2颗粒两两正反对贴布局,如下所示。

这种布局方式,地址控制信号布线采用T型拓扑。相对于四片DDR2颗粒的情况并没有增加额外的布线分支,只相当于拓扑中的负载电容增大了。由此导致的影响主要是地址控制信号的边沿会略有变缓。但这种布局方式也有一定的缺陷,那就是DDR2对贴之后数据信号的密度增加了,给PCB布线带来了难度。因此在产品设计时需要综合考虑布线、布局密度选择合适的拓扑。当布局面积不是瓶颈而更加关注PCB层数的时候我们就需要使用单面布局的方式。

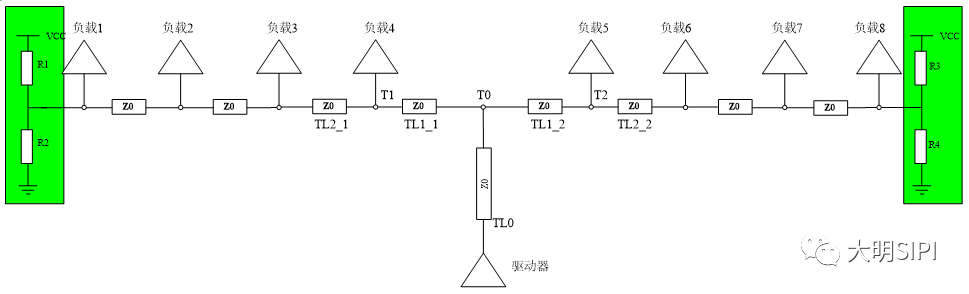

Ø单面布局使用戴维南匹配

在负载较多又采用单面布局的情况下,T型拓扑的阻抗不连续点就会很多,此时如果没有任何匹配的话信号质量无疑将不能满足要求。使用源端匹配并不能解决分支点处、以及每个负载处的阻抗不连续问题,因此只能考虑使用终端端接的方式。由于拓扑中存在左右两个分支,在两个分支的末端就都需要使用戴维南匹配。

这种端接方式需要注意的是,两组戴维南端接之间是并联关系,会极大程度地降低信号的幅值进而使噪声裕量减小。因此,端接电阻的阻值需要通过详细的SI仿真确定以保证足够的噪声裕量。此外,这种戴维南端接方式的缺点就是一个信号需要4个电阻,对于一组DDR2地址控制信号一般会有二十几个信号需要添加的电阻太多了,同时也会占用大量的布局面积。

Ø单面布局驱动器端加对地电容

当然,除了戴维南匹配之外也可以考虑其它的方式,如前面提到的在驱动器输出端加一个到地的电容,以降低输出信号的高频分量也是解决问题的一个办法。

03

星型拓扑介绍

上面讨论的多负载拓扑,无论是菊花链、远端簇还是树型拓扑针对的都是单向的一驱多的情况。在通信系统的设计中经常会用到需要多个处理器之间共享资源的情况,任何一个处理器都可以作为驱动器也可以作为接收器。对于这样的双向信号再使用上面介绍的拓扑结构就可能会产生信号完整性问题了,此时就需要使用下图所示的星型拓扑。

星型拓扑的设计要求就是保证多个器件到分支点T的延时、负载效应都大致相等。此时任意一个器件作为发送端,其它器件接收的波形都是一致的。由于任意负载到T点的延时都相同,不同负载之间的影响会比较小。

-

DDR2设计原理 DDR2 design2009-11-19 0

-

详解:SDR/DDR/DDR2/SDRAM的功能及异同2014-12-30 0

-

Altera DDR2仿真2016-06-29 0

-

ddr2和nand走线2016-10-10 0

-

关于Altera Cyclone IV GX连接DDR2 SDRAM的问题~~!!2017-09-25 0

-

请教个关于ddr2选型的问题2018-01-31 0

-

仿真DDR2时,DM368的DDR2地址信号和其它控制信号,以及DQ信号均是input 模式,为什么不是output 和inout?2018-05-25 0

-

找不到DDR2信号2019-05-10 0

-

DDR2布线寄存器设置2019-05-30 0

-

如何使用DDR2 SDRAM?2019-07-31 0

-

DDR2和DDR有什么区别2019-08-08 0

-

DDR2内存与Microblaze如何连接?2020-06-18 0

-

什么是DDR2 SDRAM2009-12-17 627

-

DDR2,DDR2是什么意思2010-03-24 1391

-

DDR和DDR2与DDR3的设计资料总结2020-05-29 1975

全部0条评论

快来发表一下你的评论吧 !