关于QE位与IO功能复用关联设计

描述

大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家讲的是几家主流QuadSPI NOR Flash厂商关于QE位与IO功能复用关联设计。

痞子衡之前写过一篇文章 《串行NOR Flash下载/启动常见影响因素之QE bit》,这篇文章介绍了几家主流厂商关于 QE bit 在 Flash 内部寄存器位置以及写入命令上的差异。今天这篇文章,咱们接着往下聊,讲一讲这几家厂商在 QE bit 与 I/O 引脚功能复用关系设计上的差异。

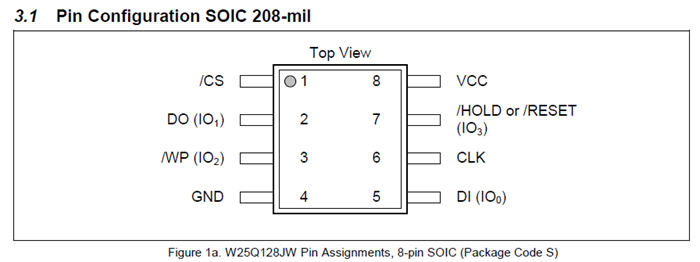

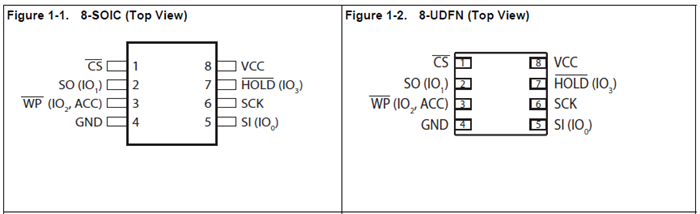

QuadSPI NOR Flash 的常见封装形式有:8-Pin SOIC/SOP/DIP/WSON/USON、16-Pin SOIC/SOP、WLCSP-21、TFBGA-24 等,本文主题是关于 I/O 引脚功能复用,显然只有引脚较少的型号才会做引脚复用设计,所以咱们主要聊得是如下典型芯片的那些 8-Pin 封装的型号:

华邦 W25Q128JWSIM 旺宏 MX25L12833F 兆易创新 GD25LE128D 镁光 MT25QL128ABA 芯成 IS25WP128 英飞凌 S25FL128L 瑞萨 AT25SL128A

一、各厂商设计

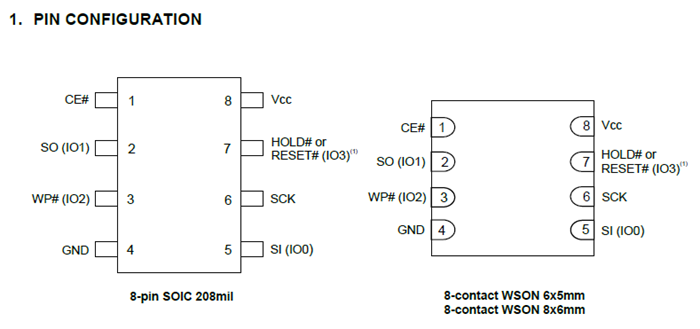

1.1 华邦 Winbond

华邦的芯片引脚复用主要是 IO2 上加了 WP# 功能,IO3 上加了 HOLD# 或者 RESET# 功能。

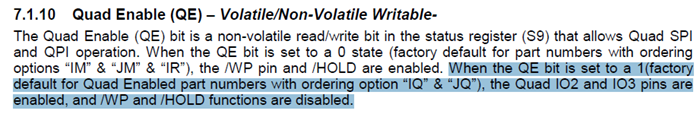

芯片内部 Status Register-2[1] 是 QE 控制位,决定了 IO2/3 到底是数据传输信号还是复用的WP#、HOLD#/RESET# 信号。这里有一个注意点,芯片丝印末位为 Q 的型号(比如W25Q128JWSSIQ)出厂默认 QE 为 1,并且不可更改为 0 (据说这是华邦为了某大客户省去 IO2/3 上拉烦恼而特意做的设计,并顺便推广了)。

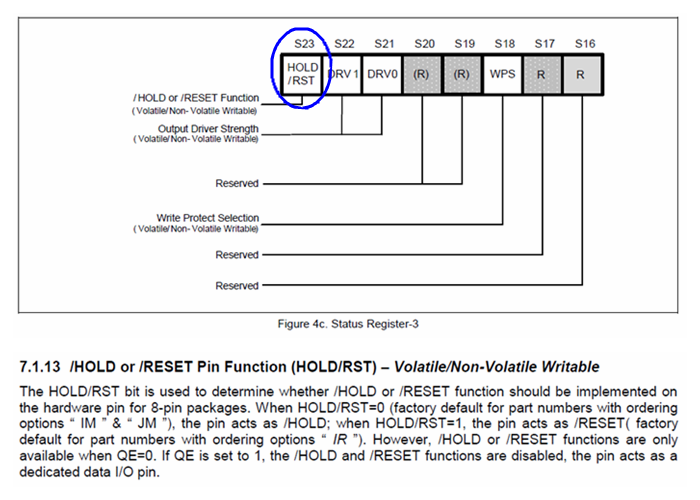

当 QE = 0 时,IO3 引脚到底是 HOLD# 功能还是 RESET#,这是 Status Register -3[7] 来决定的:

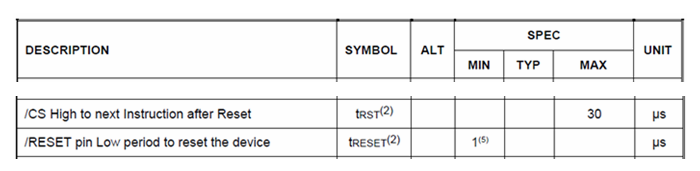

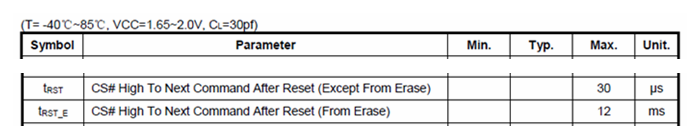

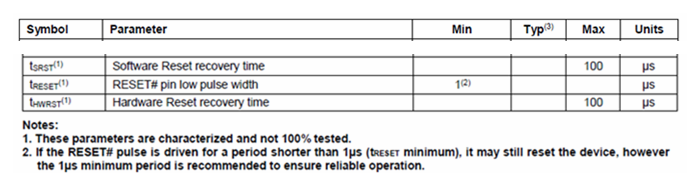

当 QE = 0 且 IO3 被配置为 RESET# 时,因为是低电平有效,为了保证不会误复位 Flash,需要给 IO3 加外部上拉(Flash 内部没有上拉)。如果此时想利用这个 RESET# 引脚复位 Flash,需持续拉低至少 tRESET 时间,Flash 会在最长 tRST 时间后才能正常响应读写操作。

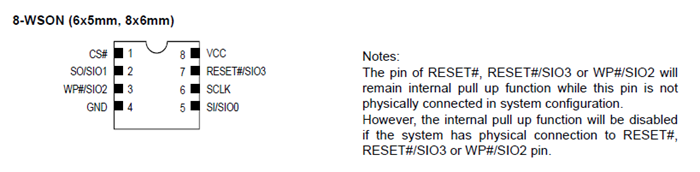

1.2 旺宏 Macronix

旺宏的芯片引脚复用主要是 IO2 上加了 WP# 功能,IO3 上加了 RESET# 功能(是的,没有 HOLD# 功能)。旺宏家有一个特色就是当 IO2/3 没有物理上的信号连接时,其会保持内部弱上拉状态。

芯片内部 Status Register[6] 是 QE 控制位,决定了 IO2/3 到底是数据传输信号还是复用的WP#、RESET# 信号。

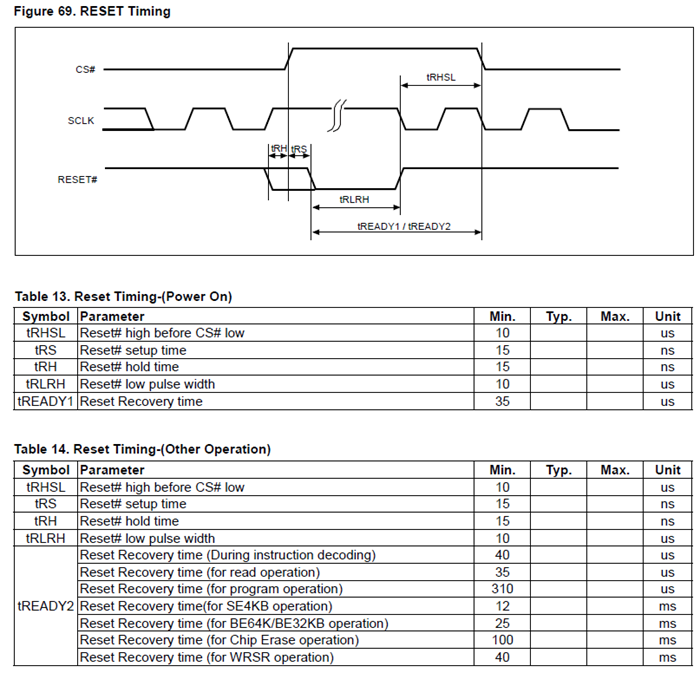

如果要借助 RESET# 引脚做 Flash 复位,旺宏家数据手册里这部分写得特别详细,还区别了不同 Flash 状态下做复位后所需要的 tREADY2 时间。

1.3 兆易创新 GigaDevice

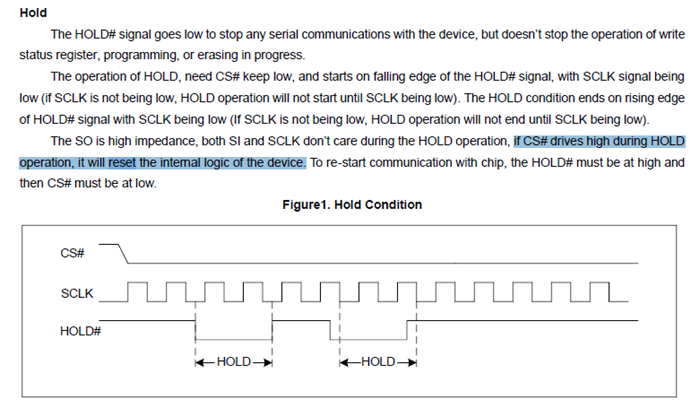

兆易创新的芯片引脚复用主要是 IO2 上加了 WP# 功能,IO3 上加了 HOLD# 功能(是的,没有名义上的 RESET# 功能)。Flash 厂商前三强关于这里的设计都不同。

需要注意的是兆易创新家也有一个特色就是当 CS# 拉高且 HOLD# 拉低时,也有 Flash 复位效果,这感觉 IO3 的复用功能是根据 CS# 信号状态来切换的。

芯片内部 Status Register-2[1] 是 QE 控制位,决定了 IO2/3 到底是数据传输信号还是复用的WP#、HOLD# 信号。

因为没有名义上的 RESET# 功能,所以数据手册里的 AC 表主要是为软件 Reset 命令写的,但是相信也适用隐藏的 RESET# 功能。

1.4 镁光 Micron

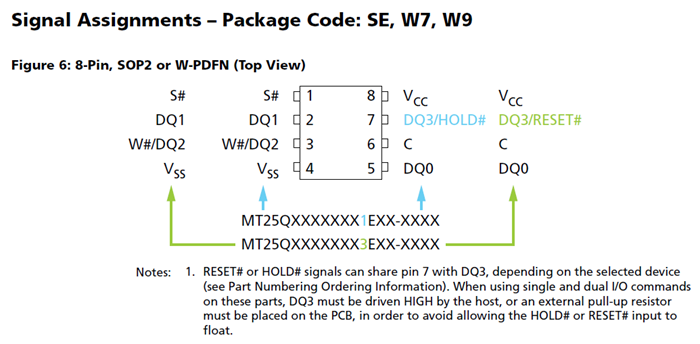

镁光家的做法就更有意思了,IO2 上加了 WP# 功能这个没异议,IO3 上功能复用直接提供两种不同型号,要么是 HOLD#,要么是 RESET#。

当然镁光家最大的特色是并没有 QE 控制位,IO2/3 具体功能主要靠当前命令类型来决定:如果是 Single SPI 或者 Dual I/O SPI 传输,则 IO2/3 是 WP#/RESET#/HOLD# 功能;如果是 Quad I/O SPI 传输,则 IO2/3 用于传输数据。

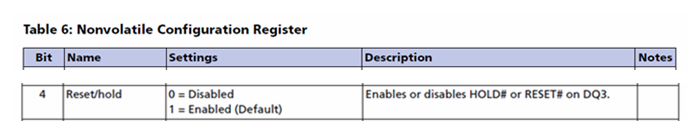

此外,镁光家还在 Configuration Register[4] 里让用户可以选择是否关闭 IO3 的 Reset/Hold 复用功能。

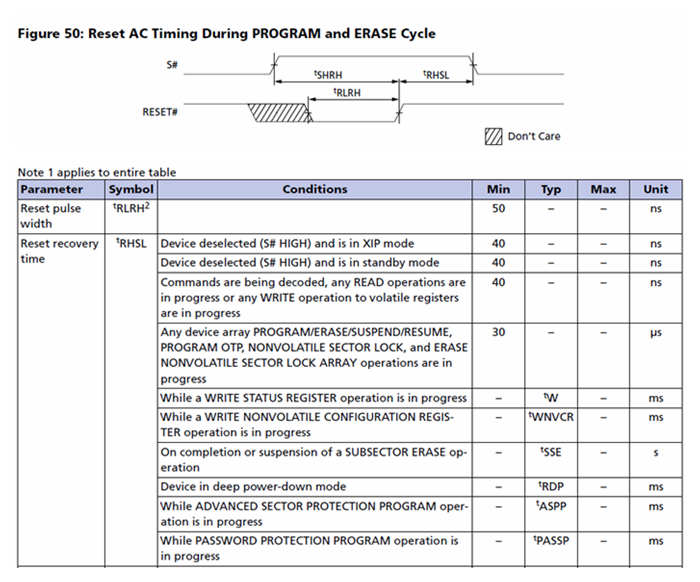

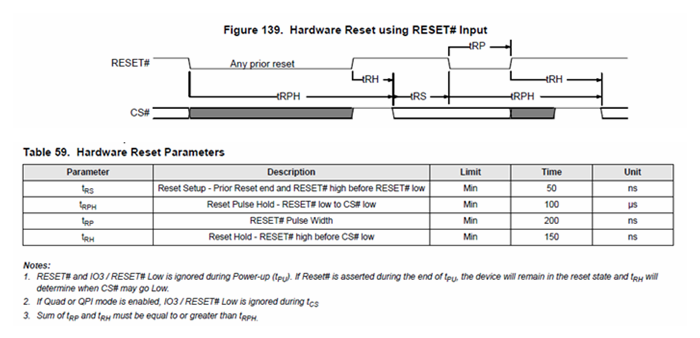

关于 RESET# 信号时序,镁光数据手册里也写得比较详细。

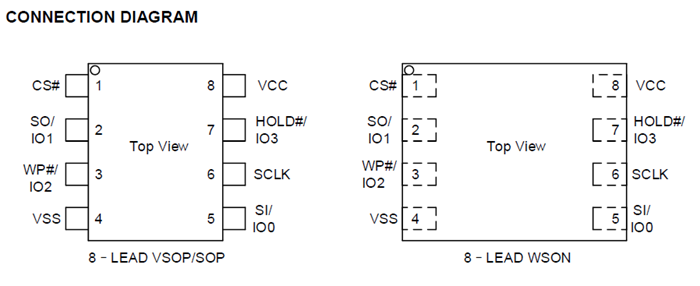

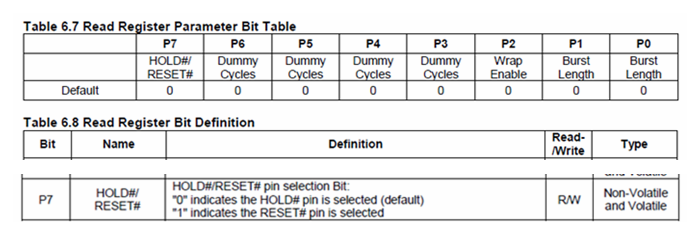

1.5 芯成 ISSI

芯成的芯片引脚复用主要是 IO2 上加了 WP# 功能,IO3 上加了 HOLD# 或者 RESET# 功能。跟华邦家设计一致。

芯片内部 Status Register[6] 是 QE 控制位,决定了 IO2/3 到底是数据传输信号还是复用的WP#、HOLD#/RESET# 信号。

当 QE = 0 时,IO3 引脚到底是 HOLD# 功能还是 RESET#,这是 Read Register[7] 来决定的:

关于 RESET# 信号时序,芯成数据手册里写得与华邦、兆易创新一样比较粗略。

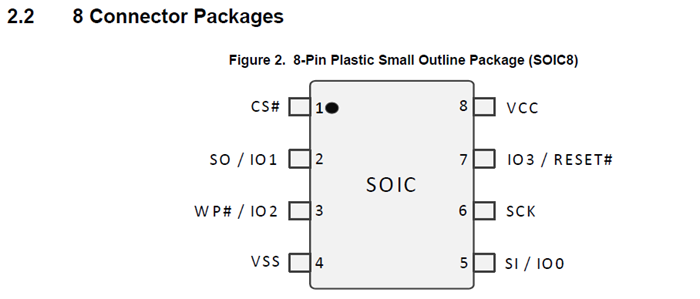

1.6 英飞凌(原Spansion)

英飞凌的芯片引脚复用主要是 IO2 上加了 WP# 功能,IO3 上加了 RESET# 功能。跟旺宏家设计一致。英飞凌家明确地给 IO2/3 内部加了上拉,不用可以直接悬空。

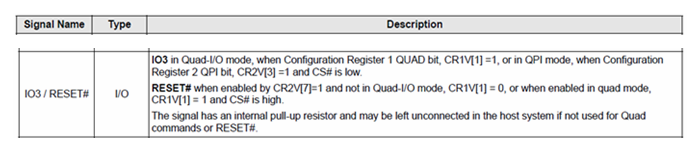

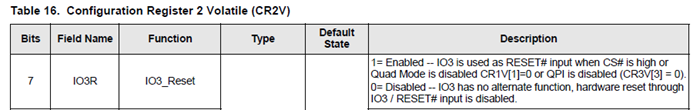

芯片内部 Configuration Register-1 Volatile[1] 是 QE 控制位,决定了 IO2/3 到底是数据传输信号还是复用的WP#、RESET# 信号。

此外,英飞凌家还在 Configuration Register-2 Volatile[7] 里让用户可以选择是否关闭 IO3 的 RESET# 复用功能。

关于 RESET# 信号时序,英飞凌数据手册里写得比较简洁。

1.7 瑞萨(原Adesto)

瑞萨的芯片引脚复用主要是 IO2 上加了 WP# 功能,IO3 上加了 HOLD# 功能。IO2/3 内部也加了上拉。

芯片内部 Status Register-2[1] 是 QE 控制位,决定了 IO2/3 到底是数据传输信号还是复用的WP#、HOLD# 信号。

因为 8-Pin 封装完全没有硬件 RESET# 信号设计,所以就不介绍复位时序了。

二、快速对比表

| 厂商型号 | 复用情况 | QE位控制 | IO3复用功能选择 | IO2/3上拉情况 |

|---|---|---|---|---|

| 华邦 W25Q128JWSIM |

IO2与WP# IO3与HOLD#/RESET# |

Status Register-2[1] | Status Register-3[7] | 无内部上拉 |

| 旺宏 MX25L12833F |

IO2与WP# IO3与RESET# |

Status Register[6] | N/A | 内部弱上拉(仅当悬空时) |

| 兆易创新 GD25LE128D |

IO2与WP# IO3与HOLD# |

Status Register-2[1] | CS# | 无内部上拉 |

| 镁光 MT25QL128ABA |

IO2与WP# IO3与HOLD# IO3与RESET# |

传输命令类型 | Config Register[4]开关 | 无内部上拉 |

| 芯成 IS25WP128 |

IO2与WP# IO3与HOLD#/RESET# |

Status Register[6] | Read Register[7] | 无内部上拉 |

| 英飞凌 S25FL128L |

IO2与WP# IO3与RESET# |

Config Register-1[1] | Config Register-2[7] | 内部上拉 |

| 瑞萨 AT25SL128A |

IO2与WP# IO3与HOLD# |

Status Register-2[1] | N/A | 内部上拉 |

至此,主流QuadSPI NOR Flash厂商关于QE位与IO功能复用关联设计痞子衡便介绍完毕了,掌声在哪里~~~

责任编辑:彭菁

-

stm32功能复用 IO 时钟2016-01-17 0

-

STM32-IO-AFIO(复用功能IO和调试配置)2018-07-06 0

-

为什么开启IO复用功能时钟才能使用外部中断2019-05-21 0

-

请问这里IO口“复用”的是什么呢?2019-06-18 0

-

IO复用问题2019-07-18 0

-

GPIO的功能复用2021-08-05 0

-

浅析IO引脚复用和映射2021-11-01 0

-

端口复用映射原理及GPIO外设复用功能配置过程2021-12-09 0

-

怎么去设置不同的STM32 IO复用2022-01-07 0

-

IO复用功能使用2022-01-18 0

-

Segger flasher对于RT1061的生产编程,QE位不能用闪光灯设置怎么解决?2023-05-05 0

-

Boot rom如何启用nor flash中的QE位?2023-05-30 0

-

MCU学习笔记_IO引脚复用和映射2021-10-26 701

-

IO引脚复用与映射2021-11-26 469

-

关于STM32的 I/O 复用功能2022-10-20 3037

全部0条评论

快来发表一下你的评论吧 !