基于PN结隔离(JI)技术的驱动芯片简介及设计指导

描述

引言

自从1989年国际整流器公司(IR)率先推出首款单片式高压驱动产品以来,高压集成电路(HVIC)技术就开始利用获得专利的单片式结构,集成双极器件、CMOS及横向DMOS器件,设计出了击穿电压分别高于700V和1400V的产品;这些高压驱动芯片可以工作在600V和1200V偏置电压下。

2016年英飞凌完全收购IR后,英飞凌拥有了这项经过多年市场验证的PN结隔离(JI)技术,该技术是一项成熟的、可靠的且经过市场验证的技术。特有的HVIC和抗闩锁CMOS技术可打造出可靠的单片式构造。先进的制造工艺生产出性价比最佳的产品,可面向电机控制,开关电源等多种应用。

英飞凌PN结隔离(JI)技术的主要益处:

❖

最大驱动电流可达4A

❖

精密模拟电路(严格的时序/传输延迟)

❖

拥有行业内数量最多的标准级门极驱动产品

❖

电压等级:1200V、600V、500V、200V和100V

❖

驱动结构类型:三相、半桥、单通道等

❖

最佳性价比

PN结隔离(JI)技术介绍

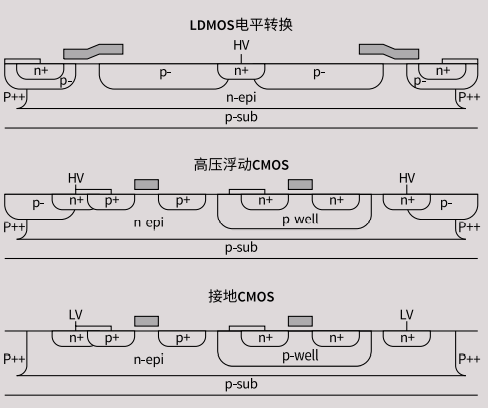

一个完整的半桥驱动芯片包含了耐高压的高边驱动电路和低边驱动电路,其中高边驱动电路包含高压电平转换电路和高压浮动驱动电路。PN结隔离技术(JI)通过多晶硅环形成的“井”型高压浮动开关,将可“浮动”600V或1200V的高压电路与其他低压电路在同一硅片上隔离,从而通过对地的低压数字信号直接驱动需要高压浮动开关的功率器件IGBT和MOSFET。广泛应用于各种常见电路拓扑中,包括降压电路、同步升压电路、半桥电路、全桥电路和三相全桥电路等等。

下图分别是LDMOS电平转换电路以及高低边驱动CMOS的横切面图。

电平转移式高压驱动芯片的

内部框图和工作原理

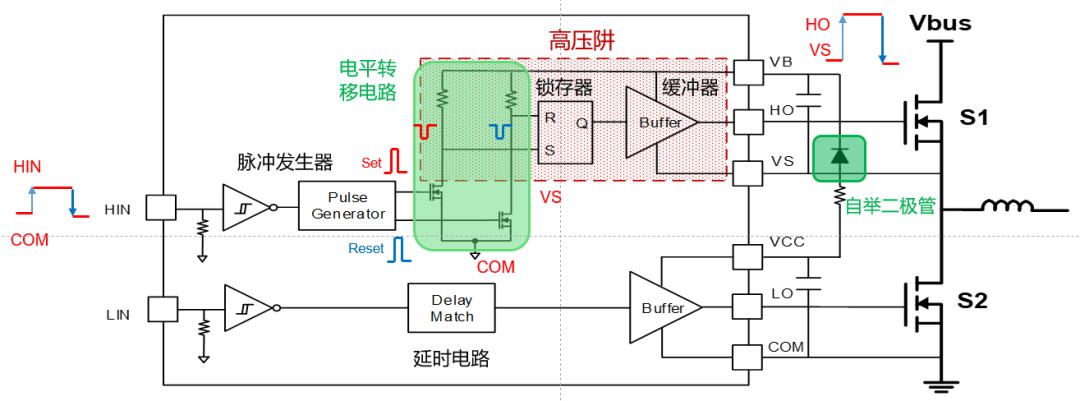

下图是一个典型半桥驱动芯片的内部设计原理和结构。

这个半桥驱动芯片高边HVIC包含了:

❖

脉冲发生器:在输入信号HIN的上升沿和下降沿产生脉冲信号;

❖

电平转移电路:把以COM为参考的信号转换成以VS为参考的信号;

❖

SR锁存器:锁存从电平转移电路传输过来的脉冲信号;

❖

缓冲器:放大输入信号

❖

延时电路:补偿高边信号的传输延时;

❖

自举二极管:在S2开通时对自举电容进行充电。通过电平转换电路,使相对于地(COM)的Hin信号转换成同步的相对对于悬浮地(VS)的Ho信号,从而控制高边S1的开关。

VS负压和闩锁效应

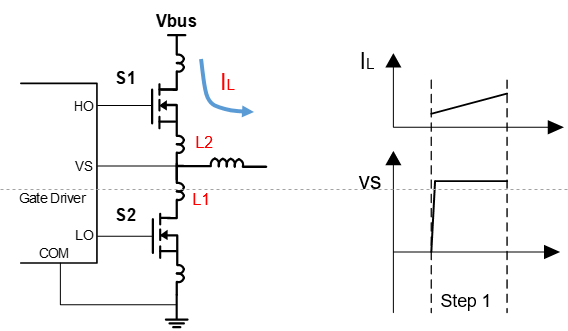

在半桥电路中,感性负载、寄生电感和下管反向续流可能在VS脚产生负压。基于HVIC的构造,VS负压可能导致HVIC失效。因此,如何抑制VS负压,将是HVIC应用中的重要课题。

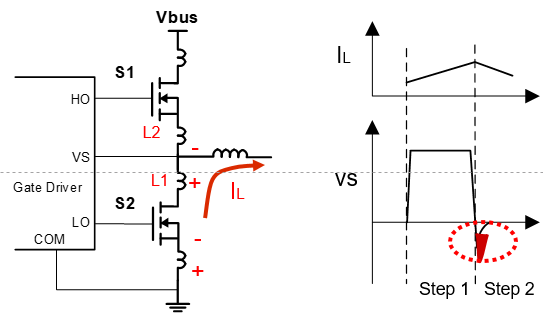

L1,L2分别是上下管上功率器件的封装电感和电路走线的寄生电感,当上管开通时,电流经过上管流过负载电感;上管关断换流时,续流电流经过S2的体二极管,并在L1L2寄生电感上产生电压,导致VS端产生了低于地线电压的负压。该负电压的大小正比于寄生电感的大小和开关器件的电流关断速度di/dt;di/dt由栅极驱动电阻Rg和开关器件的输入电容Ciss决定。

VS负压除了使Vbs超过芯片的绝对最大额定值,导致芯片过压损坏;更多的时候是产生闩锁效应,导致不可预测的结果。

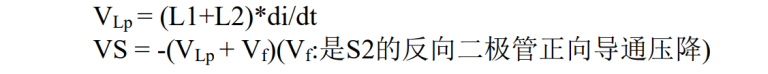

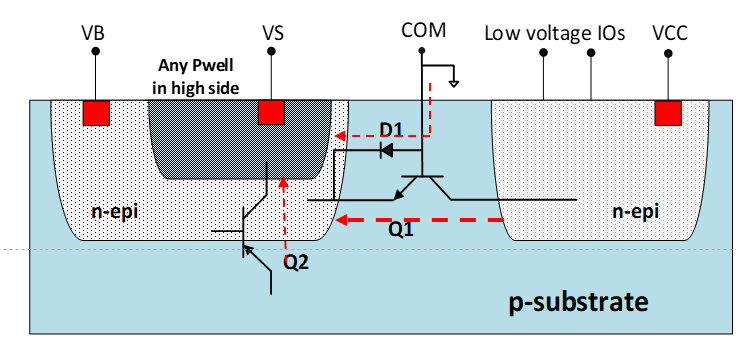

如上图,驱动芯片外延层到衬底有一个等效二极管D1(VB-COM),外延层-衬底-外延层有一个等效NPN三极管Q1(VCC-COM-VB)。当VS产生负压时,D1/Q1可能导通,会引起HO跳变(在没有输入信号时,HO可能从低电平跳到高电平),从而导致半桥功率管短路使系统失效,或者引起驱动芯片的内部CMOS结构发生闩锁效应,从而导致驱动芯片失效。

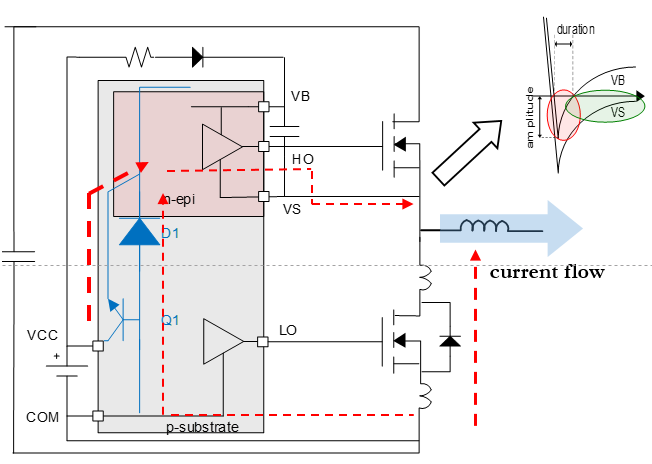

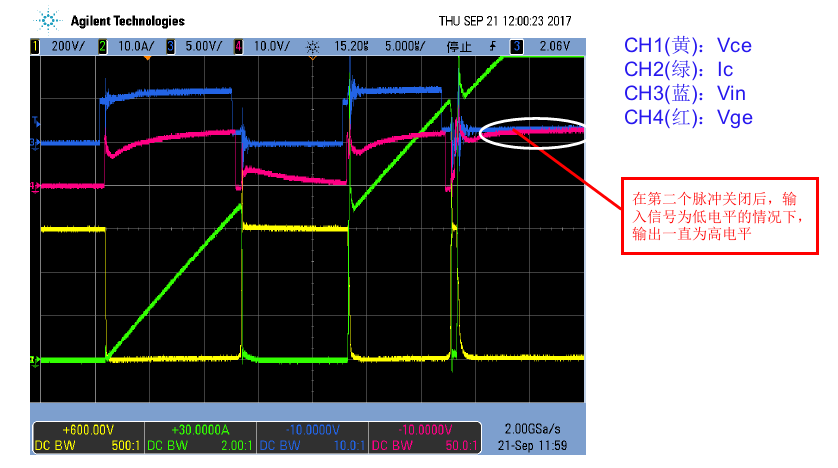

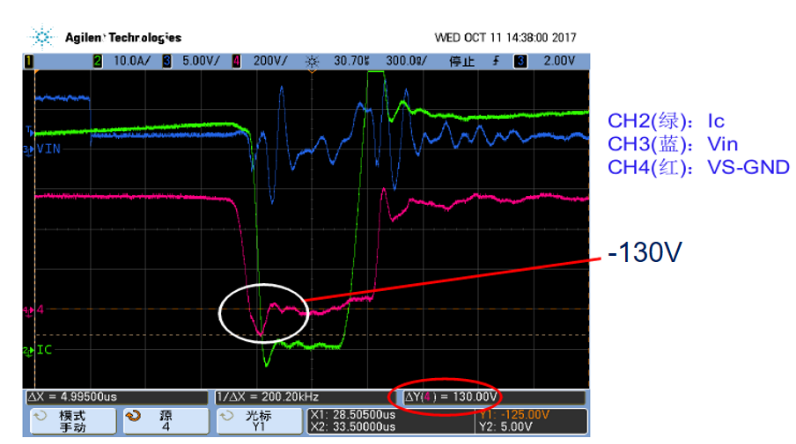

上两图是来自客户的一个实测双脉冲波形,驱动芯片的输入信号是低电平,但是输出跳变成高电平,在上管关断的时候VS脚的瞬变电压达到了-130V,这个负压使得HO从低电平跳变成高电平。

JI技术驱动芯片

周边电路设计指导

为了减小-VS(VS=-(Lp*di/dt+Vf)),在电路设计中需要做到:

1.使寄生电感最小化,减小驱动回路的走线,避免交错走线。

2.半桥电路两个功率管尽可能靠近安装,它们之间连接尽量用粗短线

3.驱动芯片尽量靠近功率管

4.母线电源上的退耦电容尽量靠近功率管和电流检测电阻

5.使用低寄生电感的电阻作为电流检测电阻,并尽量靠近下面的功率管

6.VB-VS之间使用低寄生电感的瓷片电容

7.VCC-COM之间也要使用低寄生电感的瓷片电容,推荐使用的VCC-COM之间的电容容量是VB-VS之间的电容容量的十倍以上

8.退耦电容尽量靠近驱动芯片引脚

如果注意了上述事项,VS脚负压仍然很大的话,可以考虑降低功率管的开关速度,以便降低开关时的电流变化率di/dt,例如:

1.外加缓冲电路

2.增大驱动电阻(注意:这种方法会增加功率管开关损耗)

-

对 PN结 的认识2024-02-25 0

-

PN结的电容特性2008-09-10 0

-

关于pn结的疑惑2012-12-08 0

-

pin结与pn结的特性比较2013-05-20 0

-

pn结是如何形成的?2016-11-29 0

-

PN结 耗尽层2017-04-13 0

-

PN结2017-07-28 0

-

[中阶科普向]PN结曲率效应——边缘结构2019-07-11 0

-

PN结的原理是什么?是怎样形成的?特征是什么?有什么应用?2021-03-16 0

-

PN结是如何形成的?什么是pn结二极管?2023-02-08 0

-

关于形成的pn结的常见问题有哪些2023-02-15 0

-

基于PN结隔离(JI)技术的驱动芯片简介及设计指导2022-04-12 2016

-

绝缘体上硅(SOI)驱动芯片技术优势及产品系列2022-04-02 950

-

无磁芯变压器(CT)隔离驱动芯片技术优势及产品系列2022-04-20 841

全部0条评论

快来发表一下你的评论吧 !