小型化晶振如何进行电路设计?

描述

你知道吗?小型化已经是电子行业的一个持续趋势。那么,石英晶体尺寸减小会在电路设计过程中引起不同的问题。为了帮助解决这些问题,本文重点介绍对缩小石英晶体尺寸时对电路设计有什么要注意的。

频率

晶体的尺寸越小,谐振频率就越高。对于石英来说,石英毛坯的厚度与谐振频率成反比关系。这意味着当晶片变薄时,频率会增加。相反,这意味着需要更厚的空白来获得更低的频率。

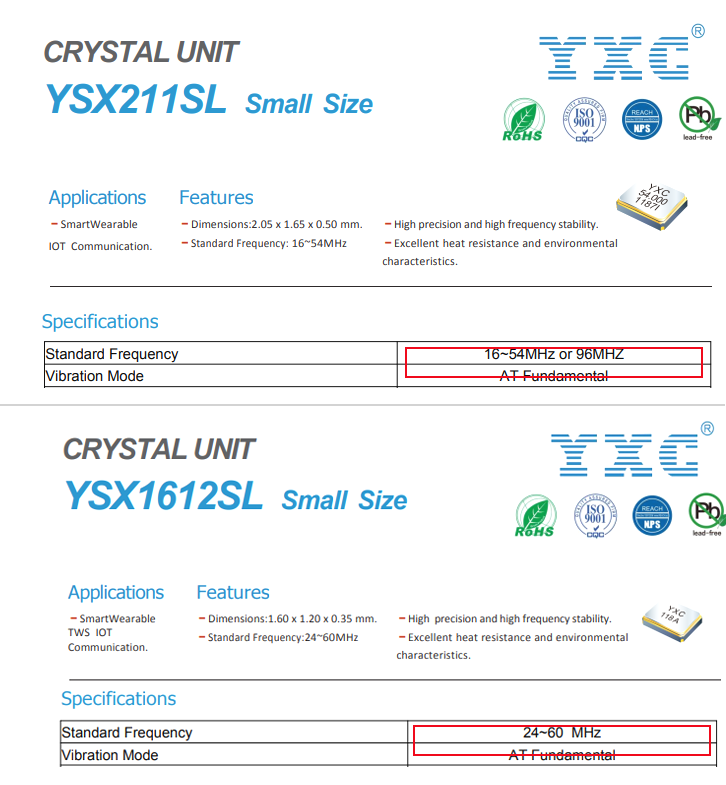

因此物理上石英晶体(指无源谐振器)在2.0x1.6mm封装中提供不能低于16MHz的频率或在1.6x1.2mm封装中不能提供低于24MHz的频率。在电路设计中,从较大尺寸的石英晶体更换到较小尺寸的石英晶体时需要考虑到这一点。

2016&1612晶振封装频率

等效串联电阻

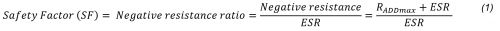

较小晶体的另一个特点是等效串联电阻(ESR)更高。晶体的ESR取决于几个参数,例如频率、晶体尺寸、电极尺寸和安装结构。一般规则,晶体越小,ESR越高。在电路设计评估期间,需要考虑ESR以确保可以保证稳定的振荡。稳定振荡的特点是安全系数为5或更高。安全系数,通常也称为负电阻比,由负电阻与ESR的比值定义。

安全系数公式见公式

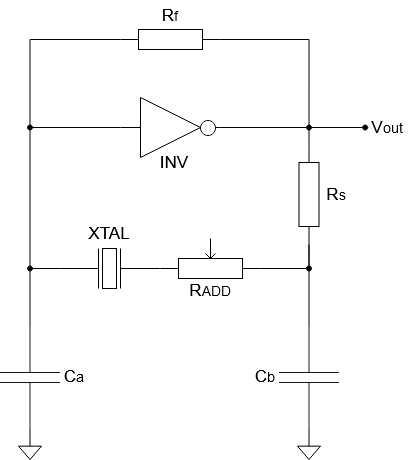

电路中的负电阻可以通过添加一个与晶体串联的电位器来测量,如图所示。电位器的电阻需要增加,直到晶体停止振荡-这个电阻值标记为RADDmax。使用RADDmax和晶体的最大ESR可以计算出负电阻和安全系数。

带RADD的电路图

如果ESR增加,则安全系数会降低,就不能再保证晶体的安全振荡(SF<5)。如果在旧电路设计中使用较小的晶体代替较大的晶体,这种现象很容易发生。

在这种情况下,如何提高安全系数并保证稳定的振荡呢?最简单方法是降低Ca和Cb。当降低Ca和Cb时,会导致RADD在振荡停止的点更高,使负电阻的改善和安全系数的增加。

这就是为什么较小的晶体通常以较低的负载电容出售。因此,在考虑从较大晶体更换到较小晶体时,应注意它也需要更换电容器。

- 相关推荐

- 晶振

-

ECEC推出超小型化宽温贴片封装石英晶振2011-07-14 0

-

小型化电子市场领域哪些晶振面临优胜劣汰2015-08-26 0

-

电路中晶振注重超小型化空间的选择方案2016-07-28 0

-

请问晶振对小型汽车起了什么作用?2018-06-28 0

-

一款小型化L波段射频收发前端模块的设计过程讲解2019-06-24 0

-

怎样去解决小型化DC/DC应用设计的问题?2021-04-21 0

-

机载计算机电源的小型化设计2021-11-12 0

-

晶振电路设计指南2022-07-05 0

-

小型化晶振对电路设计的影响2023-04-04 411

-

小型化射频收发前端的电路设计2023-11-08 137

全部0条评论

快来发表一下你的评论吧 !