RA6快速设计指南 [9] 存储器 (1)

描述

8

存储器

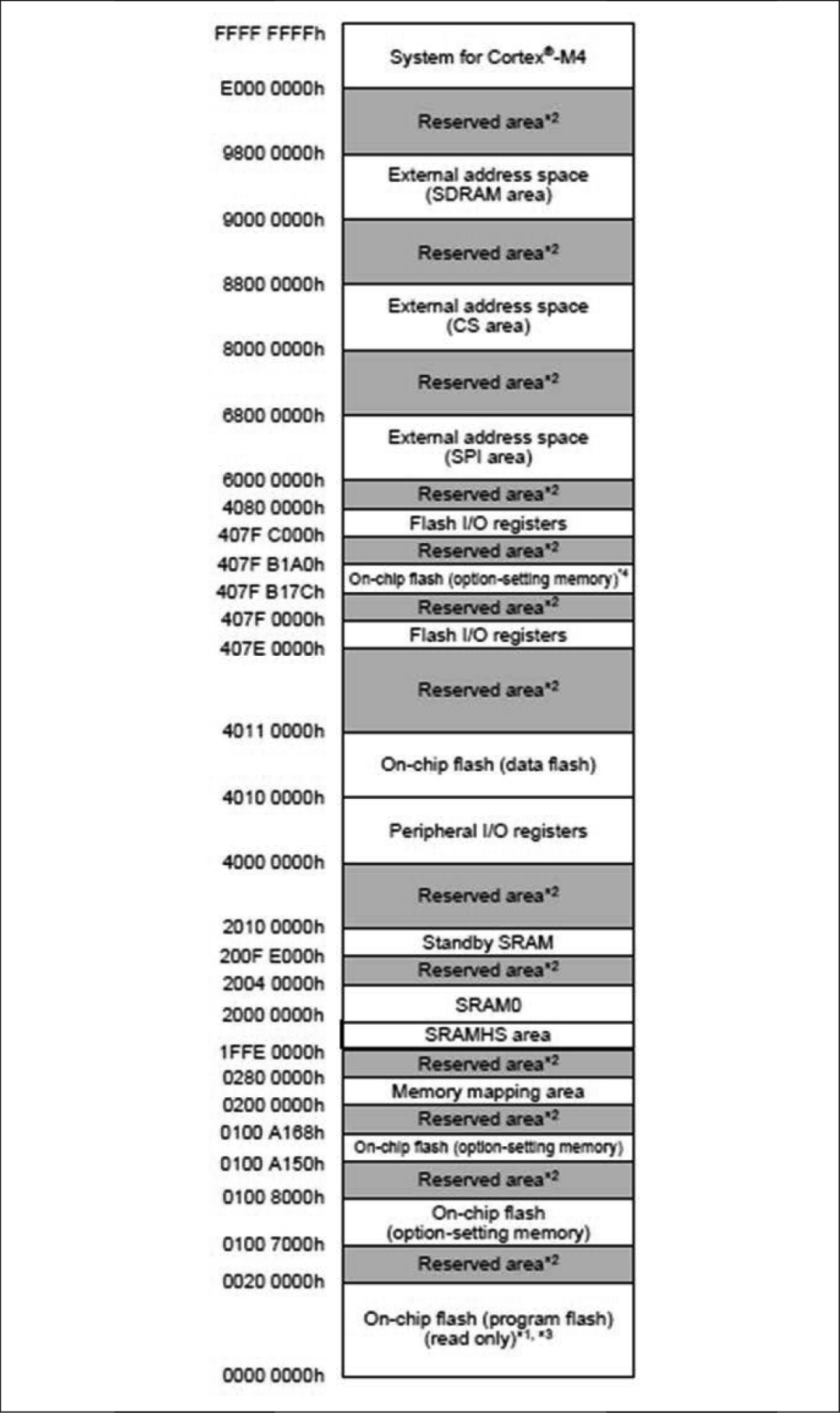

RA6 MCU支持4GB的线性地址空间,范围为0000 0000h到FFFF FFFFh,其中包含程序、数据和外部存储器总线。该系列的某些产品包括一个SDRAM控制器,可利用该控制器访问连接到外部存储器总线的SDRAM器件。程序和数据存储器共用地址空间;使用单独的总线分别访问这两个存储器,从而提高性能并允许在同一个周期访问程序和数据。存储器映射中包含片上RAM、外设I/O寄存器、程序ROM、数据闪存和外部存储器区域。

图16. RA6M3存储器映射

8.1 SRAM

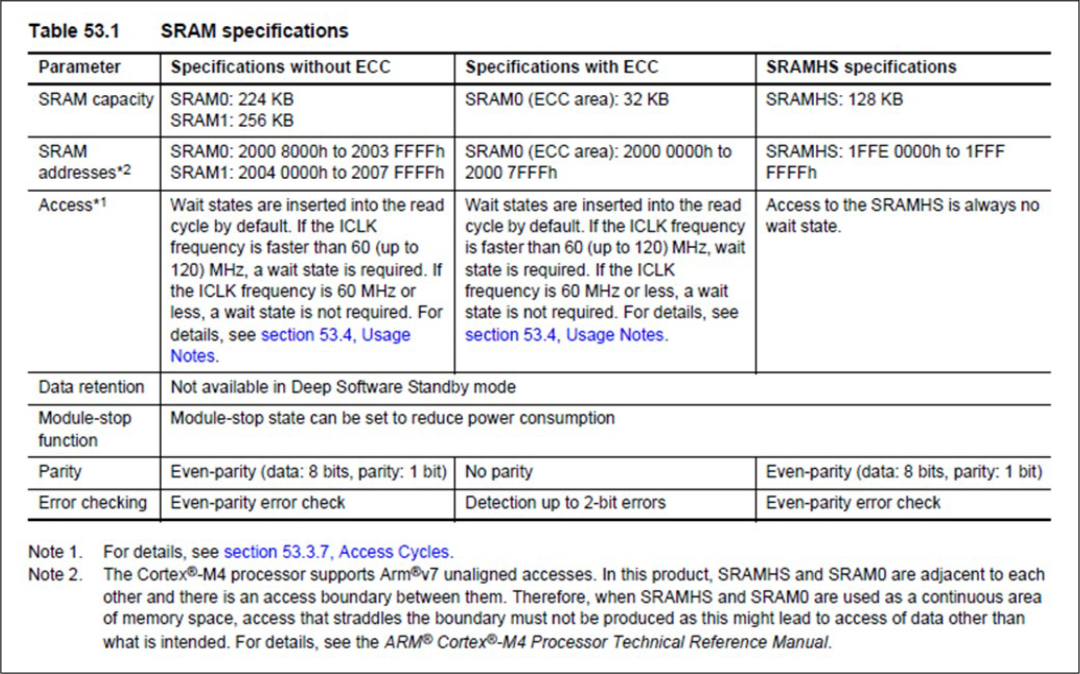

RA6 MCU提供带奇偶校验位或ECC(纠错码)的片上高速SRAM模块。SRAM0的前32KB区域受ECC控制。奇偶校验在其他区域执行。下表列出了SRAM规范。SRAM模块的数量和容量因器件而异。有关详细信息,请参见《硬件用户手册》。

图17. RA6M3 SRAM规范示例

8.2 待机SRAM

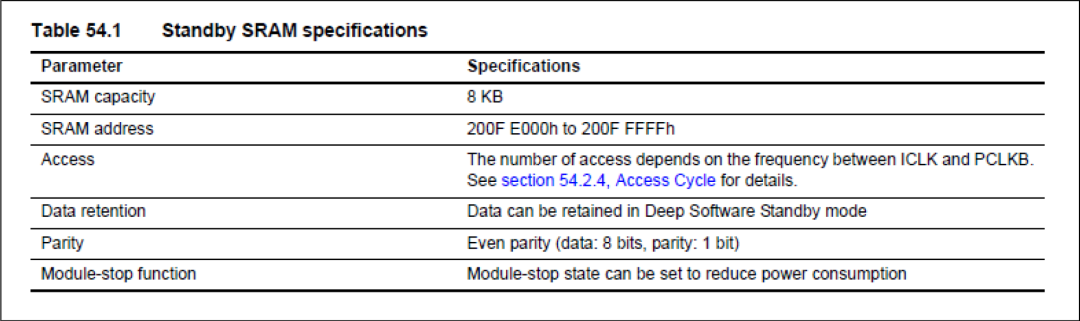

RA6 MCU提供了一个片上SRAM,支持在深度软件待机模式下保留数据。下表列出了备用SRAM规范。

在深度软件待机模式下,待机SRAM的电源由DPSBYCR.DEEPCUT[1:0]位使能。如果DPSBYCR.DEEPCUT[1:0]位设置为00b,则将在深度软件待机模式下保留待机SRAM中的数据。有关DPSBYCR.DEEPCUT[1:0]位的详细信息,请参见后文第11节“低功耗模式”。

图18. RA6M3待机SRAM规范示例

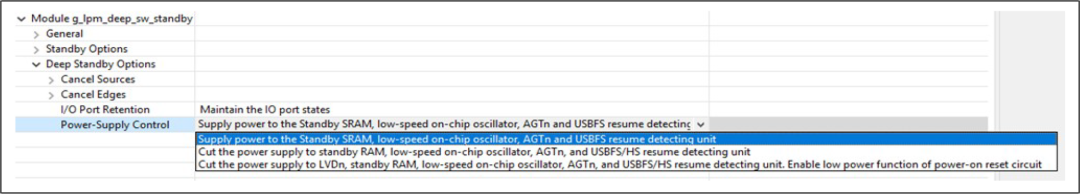

Renesas FSP中的LPM(低功耗模式)驱动程序提供了一个用于切断或保持待机SRAM电源的选项,如下图所示。仍然需要调用LPM驱动程序的API才能将所选设置写入MCU寄存器。

图19. 使用Renesas FSP配置器使能/禁用待机SRAM的电源

8.3 外设I/O寄存器

外设I/O寄存器块出现在存储器映射中的不同位置,具体取决于器件和当前的工作模式。大多数外设I/O寄存器占用的地址范围为4000 0000h到400F FFFFh。但是,位置和大小可能会因器件而异。有关详细信息,请参见《硬件用户手册》。有关详细信息,可参见“I/O寄存器”附录,也可参见每个外设功能的寄存器说明。该区域包含在所有工作模式下始终可用的寄存器。用于控制访问闪存的闪存I/O寄存器占据两个区域,即407E 0000h至407E FFFFh和407F C000h至407F FFFFh。

Renesas FSP包含采用CMSIS数据结构的C语言头文件,这些文件将特定器件的所有外设I/O寄存器映射到易于访问的I/O数据结构。

未完待续

-

PIC18F45k20内部Osc和RA6输出2020-04-15 0

-

RA MCU快速设计指南2022-11-07 183

-

瑞萨RA6系列芯片外扩SRAM方法2023-02-11 1270

-

RA2快速设计指南 [6] 存储器2023-04-06 499

-

RA6快速设计指南 [1] 简介,电源,仿真器支持(1)2023-06-04 677

-

RA6快速设计指南 [3] 选项设置存储器,时钟电路(1)2023-06-08 455

-

RA6快速设计指南 [4] 时钟电路 (2)2023-06-09 382

-

RA6 MCU设计之时钟电路2023-06-09 222

-

RA6快速设计指南 [5] 时钟电路 (3)2023-06-12 439

-

RA6快速设计指南 [8] 使用TrustZone®2023-06-19 365

-

RA6快速设计指南 [10] 存储器 (2)2023-06-26 415

-

RA6快速设计指南 [11] 存储器 (3)2023-06-28 377

-

RA6快速设计指南 [13] I/O端口配置 (2)2023-07-03 761

-

RA6快速设计指南 [17] 外部总线,一般布线实践 (上)2023-07-14 360

-

RA2快速设计指南 [5] 存储器2023-10-24 300

全部0条评论

快来发表一下你的评论吧 !