SC6301低功耗超低噪声时钟抖动消除器简介

描述

芯炽集团·新品发布

SC6301

低功耗超低噪声时钟抖动消除器

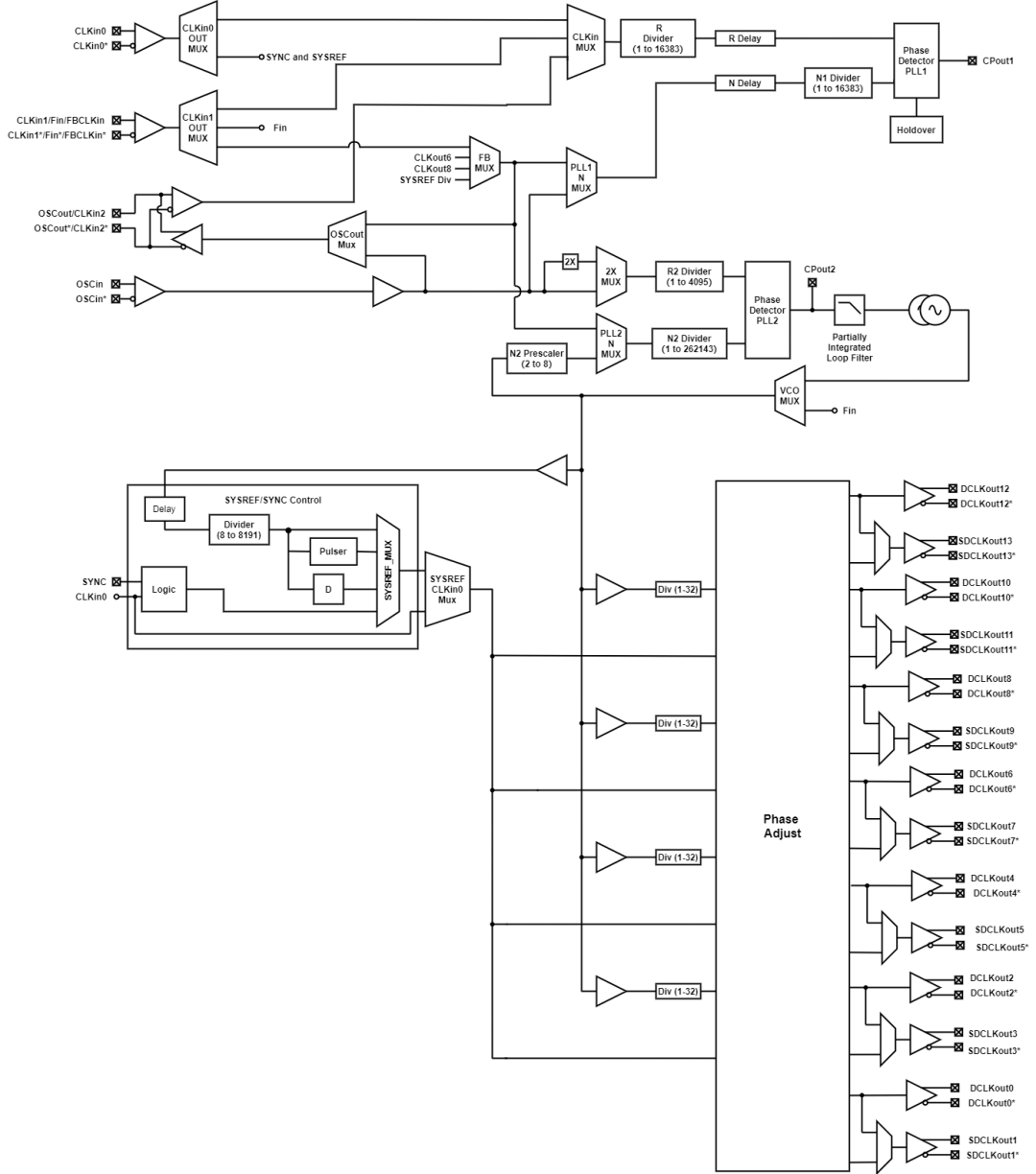

SC6301是高性能时钟调节器,支持JEDEC JESD204B。当使用设备和SYSREF时钟时,PLL2的14个时钟输出可配置去驱动7个JESD204B转换器或其他逻辑设备。SYSREF可以使用直流和交流耦合来提供。不仅限于JESD204B应用,14个输出均可单独配置为传统高性能时钟系统输出。

SC6301具有高性能、低功耗、双VCO、动态数字延迟、信号丢失保持等特性。因此,SC6301是提供灵活的高性能时钟树的理想选择。

新品简介

01主要性能

支持JEDEC JESD204B

超低RMS抖动

76fs RMS Jitter (10kHz到20MHz)

-162dBc/Hz@245.76 MHz

PLL2可提供多达14路差分时钟

最多7个SYSREF时钟

时钟最大输出频率3.1GHz

支持LVPECL, LVDS, HSDS, LCPECL等输出接口

PLL1 提供一个VCXO/Crystal缓冲输出

支持LVPECL, LVDS, 2路LVCMOS等输出接口

PLL1

3个备用的输入时钟

手动切换模式

无中断切换和LOS

集成低噪声的晶体振荡电路

具有输入时钟丢失的保持模式

PLL2

相位检测速率:=<155MHz

2路集成低噪声VCO

输出支持1到32整数分频,占空比50%

高精度数字延迟,可自适应性

23ps步进模拟延迟

模式:双PLL, 单PLL, 时钟分布

工作温度:-40℃到85℃

工作电压:3.15V到3.45V

QFN-64封装

02应用场景

无线基础设施

数据交换时钟

网络, SONET/SDH, DSLAM

医疗/视频

测量

03功能框图

审核编辑:汤梓红

-

低噪声和低功耗可兼得2018-10-29 0

-

低噪声和低功耗可兼得吗?2018-10-30 0

-

基于级联PLL的超低噪声精密时钟抖动滤除技术仿真和研究设计2019-07-05 0

-

超低功耗转换器的控制方案可消除可听开关噪声2019-08-07 0

-

低噪声和低功耗怎么同时获得?2019-08-08 0

-

超低功耗嵌入式的隐患怎么消除?2020-03-09 0

-

低噪声和低功耗可以兼得吗?2021-01-25 0

-

三分钟教会你,级联PLL超低噪声精密时钟抖动滤除技术研究2018-05-30 5302

-

低噪声和低功耗也不可兼得吗2022-02-22 882

-

ADA4075-2:低功耗、超低噪声放大器2021-03-19 658

-

ADA4857-1/ADA4857-2: 超低失真、低功耗、低噪声、高速运算放大器2021-03-19 592

-

超低功耗 MCU 的能量收集如何消除电池2022-12-28 671

-

SC6301低功耗超低噪声时钟抖动消除器2023-06-21 560

-

支持204B,输出频率高达3.1G,支持14路差分时钟输出,超低抖动,首颗正向国产替代时钟调节器SC63012024-04-02 181

-

高性价比的时钟解决方案——SC6301,兼容LMK048282024-04-12 124

全部0条评论

快来发表一下你的评论吧 !