异步复位同步释放问题解析

电子说

描述

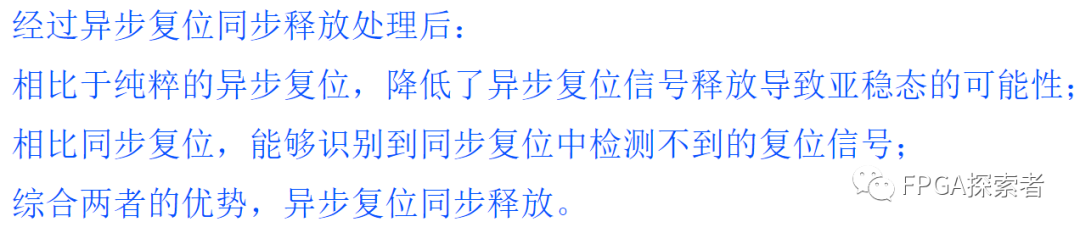

(1)异步复位同步释放的优势

(2)D 触发器搭建电路

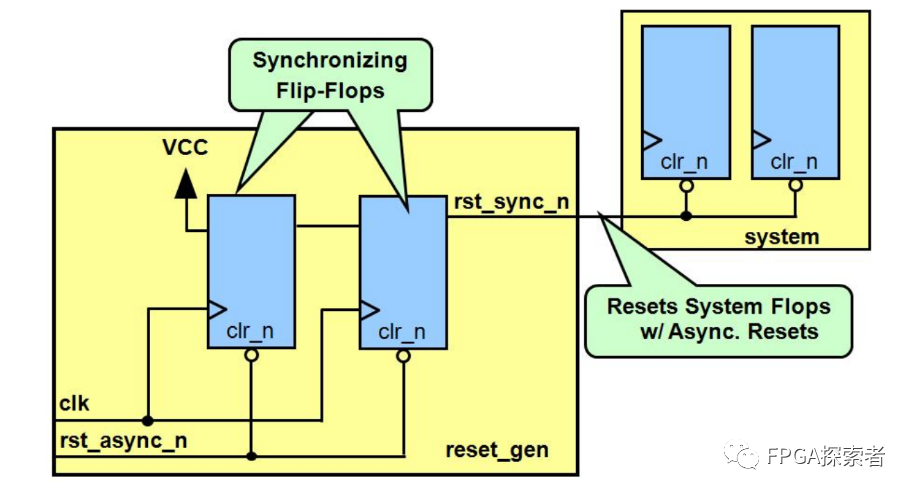

使用 2 个带异步复位的寄存器,D端输入逻辑 1(VCC)。

当异步复位无效(rst_async_n = 1)时,同步后的复位信号 rst_sync_n 也为 1;

当异步复位有效(rst_async_n = 0)时,同步后的复位信号 rst_sync_n 立刻为 0,即实现了“异步复位”,但是会在时钟上升沿来临时恢复为 1,实现“同步释放”;

(以下图片来自Altera FPGA)

第一级触发器的输入 D 接电源,即高电平1’b1。

第一级触发器的输出,很可能存在亚稳态,使用两级触发器做同步。

(3)Verilog 代码

reg rst_n_1 = 1'b1;

reg rst_n_2 = 1'b1;

always @ (posedge clk or negedge rst_async_n)

begin

if( !rst_async_n ) begin

rst_n_1 <= 1'b0;

rst_n_2 <= 1'b0;

end

else begin

rst_n_1 <= 1'b1;

rst_n_2 <= rst_n_1;

end

end

assign rst_sync_n = rst_n_2;

总结

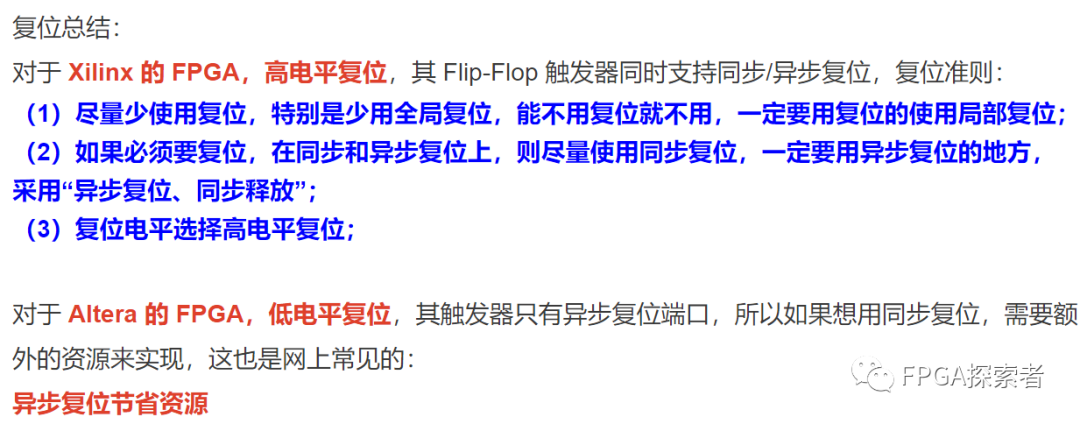

针对 Altera 的 FPGA ,没有做其他资源消耗时的具体考证,仅从上述来看,确实能够节省一些资源。

针对 Xilinx 的 FPGA :

(1)对于同一个触发器逻辑,因为同时支持异步和同步复位,所以异步复位并不会节省资源;

(2)对于其他的资源,比如 DSP48 等,同步复位更加节省资源。

首先,对于 DSP48,其内部还带有一些寄存器(只支持同步复位),如果使用异步复位,则会额外使用外部 Slice 中带异步复位的寄存器,而使用同步复位时,可以利用 DSP48 内部的寄存器;

Xilinx 的 FPGA,对于 DSP48、BRAM 资源,使用同步复位比异步复位更节省资源。

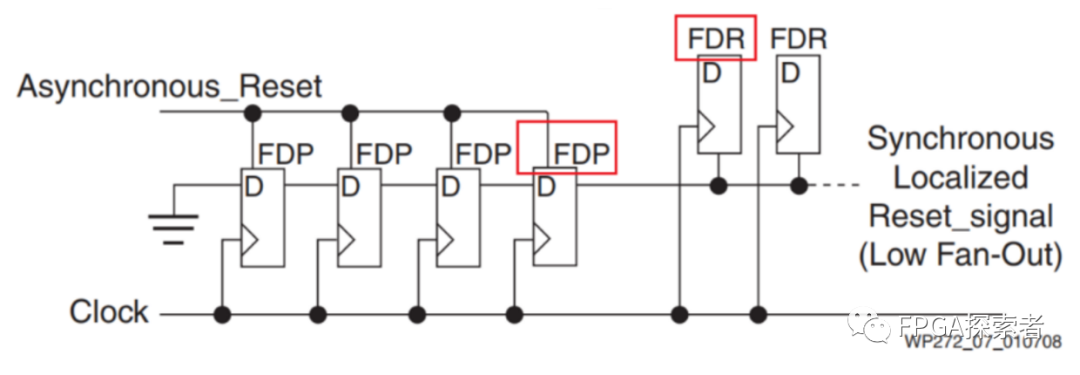

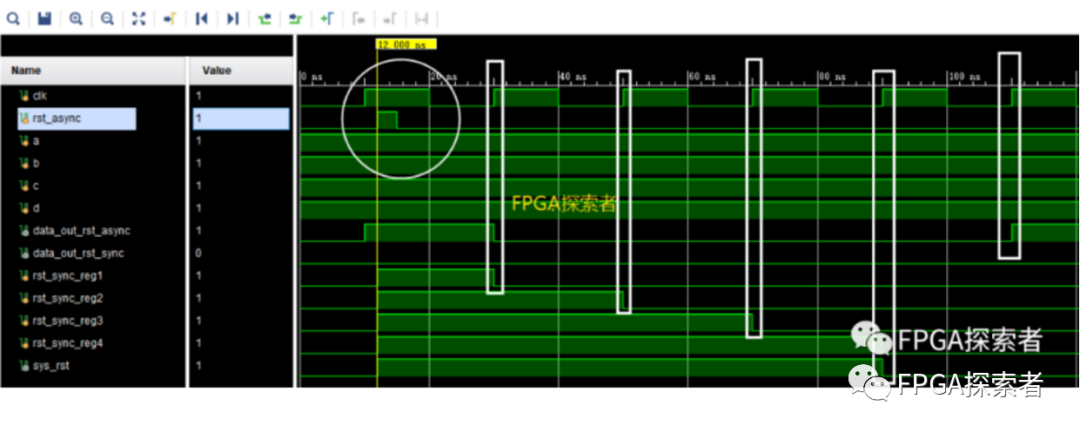

对于【高电平复位】,使用异步复位同步释放,则第一个寄存器的 D 输入是 0,这里使用了 4 个触发器打拍同步。

(参考 Xilinx 白皮书 WP272,【FPGA探索者】公众号回复【wp272】获取)。

异步复位同步释放,既能很快的检测到复位信号,不需要复位保持超过一个时钟周期,又能解决释放时的亚稳态问题(降低亚稳态发生的概率)。

-

同步复位和异步复位到底孰优孰劣呢2022-01-17 0

-

关于异步复位同步释放理解与分析2017-11-30 23724

-

同步复位sync和异步复位async2011-11-14 0

-

verilog 异步复位同步释放2013-05-28 0

-

同步复位与异步复位,同步释放的对比疑问2014-04-16 0

-

FPGA设计中的异步复位同步释放问题2018-06-07 2005

-

如何区分同步复位和异步复位?2018-06-11 6464

-

异步复位同步释放的基本原理与代码举例2019-11-20 3759

-

详细讲解同步后的复位是同步复位还是异步复位?2021-04-27 4245

-

【FPGA】异步复位,同步释放的理解2022-01-17 399

-

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?2023-06-21 810

-

异步复位同步释放有多个时钟域时如何处理 异步复位同步释放的策略2023-07-20 1288

-

同步复位与异步复位的区别2023-08-14 4100

-

浅析异步复位同步释放与同步复位打拍模块2023-08-21 572

-

FPGA学习-异步复位,同步释放2023-09-09 304

全部0条评论

快来发表一下你的评论吧 !