CTS时钟树综合对uncertainty的影响

电子说

描述

在时钟电路的设计中,存在 jitter 和 skew 问题。请解释下:

- 什么是 jitter,什么是 skew?

- 在 pre-CTS 的时序约束中,setup 和 hold 的 clock uncertainty 分别由什么组成。

解析:

(1)名词解释

jitter,时钟抖动;

skew,时钟偏斜;

uncertainty,时钟不确定性,包括 jitter 和 skew;

Clock Tree Synthesis,时钟树综合,简称CTS;

(2)具体分析

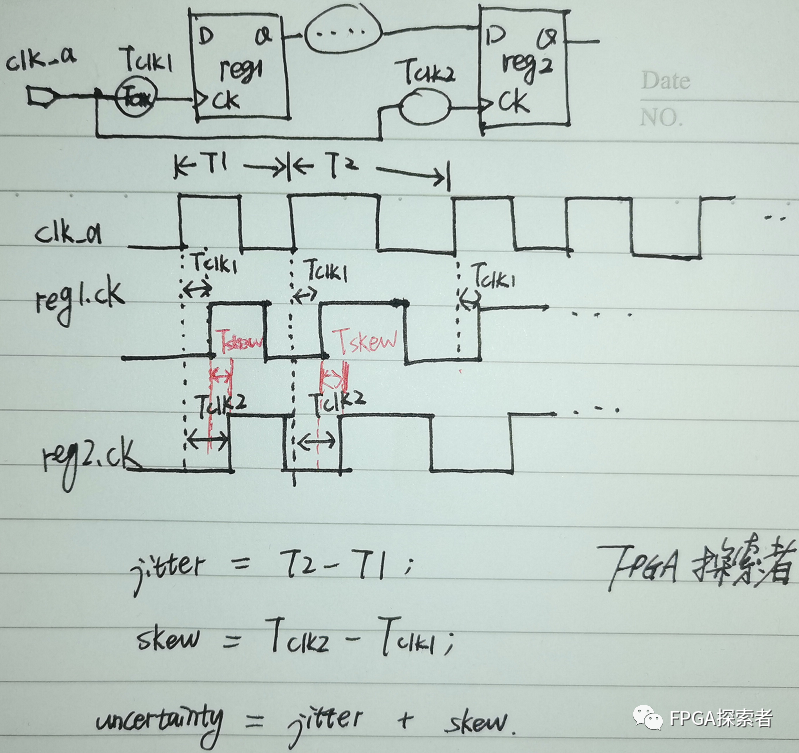

clock 时钟有不确定性(clock uncertainty),其中包括 clock jitter(时钟抖动)和 clock skew(时钟偏斜)。

clock jitter ,抖动来自时钟的产生源,比如晶振、PLL,可以理解为 PLL jitter, 是频率上的不确定性,是频偏,即针对这一个时钟,前后周期在变 ,jitter = T2 - T1(或者也存在占空比上的不确定性);

clock skew ,偏斜来自时钟树的延迟,是 一个时钟到达不同时序逻辑单元的时刻不同 ,但是周期是不变的, 存在相位差,是相偏 ,可以理解为 clock tree skew, 是相位上的不确定性 ;

对于 jitter,是晶振本身或者 PLL 电路带来的,受到温度等影响,有一定的振荡频率偏移,设计者可以更换稳定性更好的晶振来降低 jitter;

对于 skew,是时钟树上的延迟,可以通过插入 buffer 来改变,时钟树综合布线后,skew 值确定;

对于同****一个时钟到达不同的时序逻辑单元 :

pre-CTS 预布局阶段 ,时钟树 clock tree 还没有综合,所以 clock tree 的 skew 还不确定,在分析 setup 和 hold 的时候都需要考虑 skew;

对于 setup ,由于发射沿和捕获沿是相邻的两个沿,所以 要考虑 skew,也要考虑 jitter ;

对于 hold ,由于发射沿和捕获沿是同一个沿,所以 只要考虑 skew,不需要要考虑 jitter ;

如下图所示:

post-CTS 后布局阶段 ,时钟树 clock tree 已经综合,所以 clock tree 的 skew 已经确定 ,在分析 setup 和 hold 时的clock uncertainty 不确定性时,不需要将 skew 作为时钟不确定性的一部分(clock uncertainty);

对于 setup ,由于发射沿和捕获沿是相邻的两个沿,所以不确定性要 考虑 jitter ;

对于 hold ,由于发射沿和捕获沿是同一个沿,不需要要考虑 jitter, 没有时钟不确定性 。

-

解析STM32的时钟树2011-10-21 0

-

CTS的前世今生2019-01-18 0

-

系统框图和时钟树2021-08-03 0

-

介绍主时钟树2021-08-06 0

-

介绍时钟树的构成2021-08-12 0

-

为什么要了解时钟树2021-08-12 0

-

时钟树分析2021-08-12 0

-

STM32时钟树案例详解2021-08-20 0

-

什么是时钟树?2021-09-27 0

-

如何做好ARM Cortex-A7时钟树呢2022-05-31 0

-

!大量收购/回收CTS60综合测试仪CTS60 孙峰/何S:135494699212018-03-27 1165

-

芯片设计之逻辑综合过程(下)2022-08-15 1374

-

评价时钟树质量的方法2022-09-05 1594

-

时钟树综合CTS阶段如何去降低Latency和Skew2023-05-22 2206

-

时序分析基本概念介绍<Uncertainty>2023-07-07 2094

全部0条评论

快来发表一下你的评论吧 !