xilinx FPGA复位方法讲解

可编程逻辑

描述

推荐复位方法

➀ 能不复位尽量不用复位,如何判断呢?如果某个模块只需要上电的时候复位一次,工作中不需要再有复位操作,那么这个模块可以不用复位,用上电初始化所有寄存器默认值,比如reg [1:0] ff = 2'b01;这种verilog2001的方法vivado是支持的,上电后寄存器ff的值就是2'b01和你定义的是一样的。

➁ 如果要复位就统一同步高复位。也就是说复位要跟所在时钟同步,在时钟上升沿的时候复位逻辑,同时还要是高电平复位逻辑,低电平正常工作。

异步复位的缺点

异步复位中最严重的问题是,如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无效)的话,可能会导致触发器输出的亚稳态。

触发器有2个重要特点:

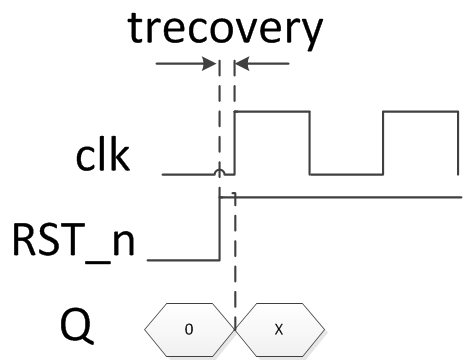

1.异步复位信号释放(对低电平有效的复位来说就是上跳沿)与紧跟其后的第一个时钟有效沿之间,有一个必须间隔的最小时间称为trecovery(recovery time,恢复时间)。

重点!

如果异步复位释放后马上来了一个时钟有效边沿,触发器的输出端的值将是不确定的,可能是高电平,可能是低电平,可能处于高低电平之间,也可能处于震荡状态,这就叫亚稳态!!!如图1所示,Q为触发器输出,复位后输出为X。

图1. 恢复时间不够造成的亚稳态

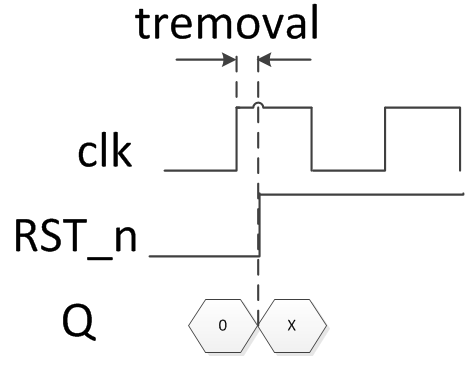

2.时钟有效沿与紧跟其后的异步复位信号释放之间所必须的最小时间称为tremoval(removal time消除时间)。,触发器的输出端的值将是不确定的,可能是高电平,可能是低电平,可能处于高低电平之间,也可能处于震荡状态,并且在未知的时刻会固定到高电平或低电平。这种状态就称为亚稳态。

重点!

如果时钟有效沿到来后,马上来了异步复位信号的上跳沿(以低电平有效为例),触发器将处于亚稳态!!!。如图2所示。

图2. 消除时间不够造成的亚稳态

同步复位缺点

总的来说同步复位并不像异步复位那样有“硬伤”,他唯一的缺点就是复位信号持续时长必须大于一个时钟周期才能保证被采到,从而能成功复位,异步复位信号只要一旦到来,立马复位,和边沿没关系。所以异步复位信号更容易被识别。其实这个缺点也算不得缺点,同步复位时长一般是可以保证的,所以多数设计用同步复位是完全没问题 的。

完美的复位方案

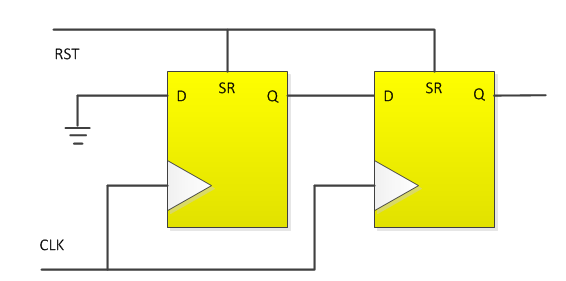

同步复位检测有缺陷,释放不会有风险;异步复位检测很灵敏,释放风险大,所以结合上述特点,采用异步复位,同步释放的方式是最完美可靠的复位方案。也就是说异步复位信号要被同步器同步一下输出,从而保证复位信号跟所在时钟域同步。如下图,复位信号到来后两个触发器被复位,解复位后,触发器输出由输入D端打拍输出:

图3 . 异步高复位同步低释放原理图

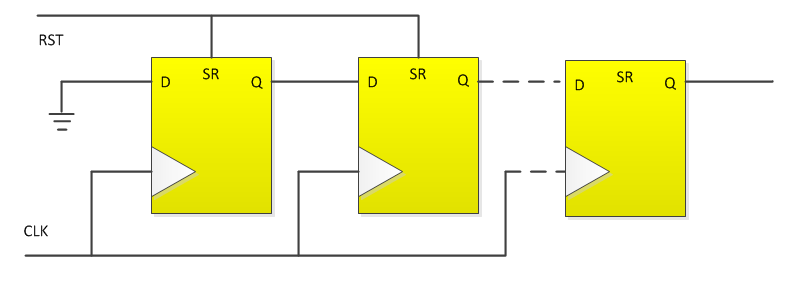

这种方式还可以扩展为下面的模式,虚线代表中间有n个触发器。经过多级打拍,复位更稳定。但是打拍太多也没必要,浪费资源。

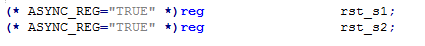

注意,两个触发器在代码里面要添加如下约束,目的是为了让这两个触发器尽量被编译到同一个slice里面,减少触发器之间的走线延迟。

完整的代码在以下百度网盘链接,里面有注释,建议大家编译出来看看总合成了什么样的电路,再次提醒,请把它当做硬件电路看,一个always一个电路

友情提示:复位的使用对时序的影响很大,滥用复位极有可能引起时序问题。

-

在FPGA开发中尽量避免全局复位的使用?(2)2017-02-11 902

-

基于FPGA的小波滤波抑制复位噪声方法2021-07-01 510

-

十分钟学会Xilinx FPGA 设计2010-03-15 774

-

Synopsys和Xilinx合作出版FPGA的SoC设计原型方法手册2011-03-21 821

-

Xilinx FPGA开发实用教程(第2版)-徐文波、田耘2012-07-31 11371

-

FPGA复位的可靠性设计方法2014-08-28 8253

-

FPGA的理想的复位方法和技巧2017-11-22 5192

-

Xilinx FPGA的同步复位和异步复位2018-07-13 6160

-

FPGA怎么搭复位电路 fpga复位电路设计方案2018-08-08 10219

-

在Xilinx FPGA上单源SYCL C++实现运行的方法2018-11-20 2962

-

FPGA的原理及电路设计应用的讲解2019-08-06 3131

-

基于Xilinx FPGA的复位信号处理2020-12-25 2346

-

你真的会Xilinx FPGA的复位吗?2023-06-21 680

-

面向Xilinx FPGA和SoC的超快设计方法指南2023-09-14 83

-

Xilinx FPGA芯片内部时钟和复位信号使用方法2023-10-27 1090

全部0条评论

快来发表一下你的评论吧 !