芯片Signoff是通过什么机制去控制偏差带来的不确定性风险的?

电子说

描述

偏差分类

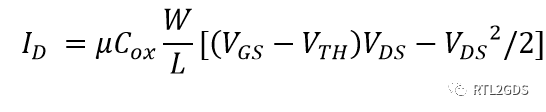

在芯片设计、制造、应用等各个环节都不可避免地会引入偏差,其直接造成的影响是晶体管、电阻电容以及绕线等电特性的不确定性。无源器件尺寸的偏差造成的影响显而易见,那么对于有源器件,从MOS管线性区的I-V特性公式可以看出:

引入偏差的因素,主要分为工艺(Process),电压(Voltage)和温度(Temperature)三类,下面分别讲解:

Process

公式中的迁移率、栅氧化层电容、宽长比、阈值电压等受芯片制造过程中光刻、刻蚀、离子注入等操作精度的影响。有些偏差是系统性的,对所有芯片的影响是一致的,另一些偏差则是局部的,微观上体现在同一颗芯片上完全相同的两个逻辑单元表现出的电性能会有差异。

Voltage

公式中的栅极电压,漏源电压等与电源电压的稳定性以及到达晶体管的电压降(IR Drop)有关。前者是系统性的,芯片外接的电源电压波动影响片上所有的器件,后者是局部的,微观上体现在从电源管脚到达晶体管的IR Drop各不相同,各个区域的电流消耗不一样也会导致IR Drop的差异。

Temperature

公式中的迁移率和阈值电压直接受温度变化的影响,芯片应用时的环境温度是系统性的影响因素,在Signoff是要充分考虑,民用、军用或者太空级别的应用场景对温度变化范围的要求也不同;此外,由于片上功耗分布的不均匀导致局部的温度差异同样需要考虑。

除了上述三个主要因素,这里还想强调两个点:噪声引入的偏差和时钟偏差

Noise

这里所述的noise更多的是芯片应用时,从输入管脚引入的噪声,或者MOS管自身的衬底噪声或者热噪声。特别是对于芯片中的模拟射频电路,比如锁相环,数模转换,放大器等,噪声是其电路设计时重点需要考虑的因素,有些是从结构的角度,有些是从工艺的角度。例如,利用差分信号可以抑制共模噪声,增加Guide Ring可以减少外围器件对其的噪声干扰等等。

Clock

对于数字电路,时钟的质量对其时序的影响非常关键。不管时钟是片外输入,还是片上PLL生成,都不是理想时钟,会引入不确定性。其中,PLL一个很重要的指标就是jitter,而且往往大的SoC中一个源时钟会分频产生很多时钟,分给不同的子系统使用,由于时钟经历的路径不一样,也会对其质量产生影响,所以设计时一般会要求设置clock uncertainty,来模拟考虑时钟频率不确定性的影响。

风控机制

上述的系统性偏差,一般通过不同的PVT Corners来控制,例如ssgnp0p72vm40c、tt0p8v85c 、ffgnp0p88v125c等等,他们分别对应不同的.lib库文件,Foundary提供的Signoff Guide中一般会给出安全的Signoff Corner列表。具体关于工艺角的选择,电压的选择,温度的选择以及RC Corner的选择下回再展开讲解。

上述的局部的偏差,一般通过OCV(On Chip Violation)机制来控制,从最早的Flat OCV,到AOCV(Advanced OCV),在到目前的POCV(Parametric OCV),一直在解放思想,释放过约的Margin。

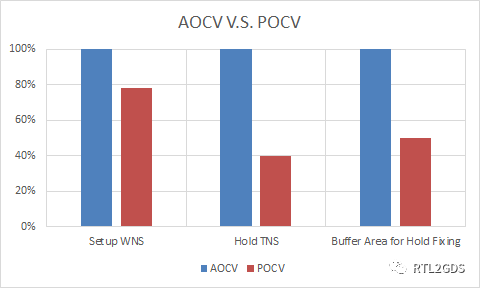

目前比较流行的POCV或SOCV,相比AOCV到底有多大的差别呢?这个需要根据情况具体分析,为了给大家更直观的概念,下面基于某一个Post-Route的Database,分别用AOCV和POCV的方式进行STA分析,可以得出如下图所示的比较结果:

可以看出,相比于AOCV来说,POCV降低了悲观度,特别是对于Hold Timing,能节省很多面积和功耗。有些大公司还执着于用Flat OCV去Signoff,在先进工艺下的代价是很大,尤其是在极低电压下。

对于噪声引入的偏差,一方面,可以在仿真时引入噪声源来模拟其带来影响,另一方面,更多的是通过成功经验得到最佳实践的方式来控制风险。而对于时钟频率偏差,则可以通过设置不同的uncertainty的方式加以控制,例如根据时钟的源头的不同,设置不同时钟之间的uncertainty。

此外,为了充分识别出工艺偏差对芯片的影响,在量产前,Foundary一般会要求把某些测试批次的Wafer故意往变慢或者变快的方向去调整工艺,看看哪一种方案对其芯片的影响是最优的。这也属于流片后管控偏差风险的一部分。

-

去嵌入和不确定性是否使用了正确的设置2018-09-27 0

-

E8364C PNA的不确定性和跟踪是什么?2018-10-18 0

-

是否可以使用全双端口校准中的S11不确定性来覆盖单端口校准的不确定性?2018-12-29 0

-

N5531S TRFL不确定性2019-02-19 0

-

435B-K05输出不确定性2019-08-02 0

-

测试系统不确定性分析2019-09-18 0

-

傅里叶变换与不确定性看了就知道2020-12-30 0

-

基于RFID技术的供应链管理项目存在哪些不确定性?2021-05-28 0

-

运算放大器的开环电压增益有哪些不确定性?2021-07-19 0

-

考虑模型参数不确定性的航天器姿态机动控制2017-01-07 758

-

三相电压型变换器不确定性建模及滑模控制方法_刘雄飞2017-01-08 767

-

连续值信息系统的不确定性度量2017-11-29 592

-

如何用不确定性解决模型问题2018-09-07 4996

-

傅里叶变换的性质 波函数和海森堡不确定性原理2022-07-07 2015

-

海森堡不确定性原理的本质是什么呢?2023-04-03 921

全部0条评论

快来发表一下你的评论吧 !