安路科技EF3L70/EF3LA0器件Freeze IO功能介绍

描述

Freeze IO 功能介绍

在FPGA位流升级过程中,器件IO信号保持不变,在新版本位流加载完成后,重新接管上次位流IO保持的信号,此特性即为Freeze IO。

在服务器、数据中心和基站等需要持续工作的系统中,重启FPGA会影响到整个系统的运行,为确保系统不断运作,在更新配置及其进入用户模式之前,通过Freeze IO特性,可在不中断系统功能的情况下,进行版本升级。

Freeze IO 实现方式

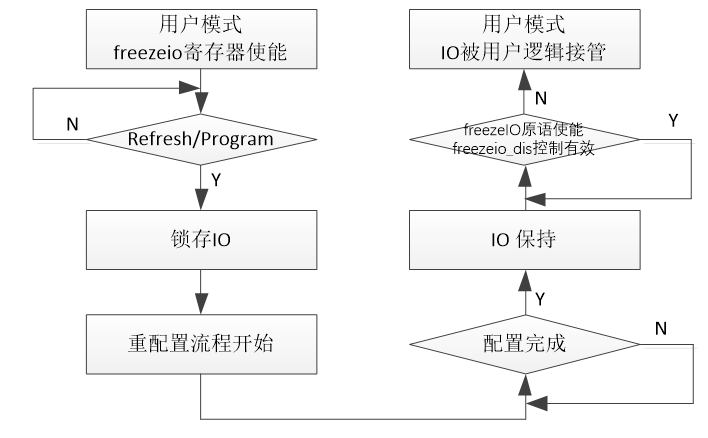

安路科技EF3L70/EF3LA0在用户模式下,若Freeze IO寄存器使能,当用户对其进行Program时,器件会锁存IO状态后,再进行位流重配置,配置过程及其配置完成后,IO状态保持,进入用户模式后,若Freeze IO原语使能,当控制信号有效时,IO状态被用户逻辑接管;否则IO将继续保持。若原语不使能,则IO状态直接被用户逻辑接管。

Freeze IO运行框图

EF3系列FPGA是安路科技“小精灵”系列的第三代产品,采用先进的 55nm 低功耗工艺,最多支持 475 个用户I/O,满足板级 IO 扩展应用需求,定位通信、工业控制和服务器市场,旨在用于大批量、低功耗和成本敏感的应用场景,使系统设计师在降低产品设计成本的同时又能够满足应用市场不断增长的带宽要求。

EF3L70/EF3LA0器件特性包括:

· 等效7952-11776逻辑资源

· 最大用户IO数量为475

· 内置 8Mb Flash,无需外部配置器件

· 每个芯片拥有唯一的 64 位 DNA

· 最小封装尺寸14 mm x 14 mm

· 内置LDO,支持单电源供电

· 部分型号支持I2C、SSPI升级

技术支持:

安路科技提供丰富的设计工具帮助用户有效地利用EF系列FPGA实现复杂系统设计。业界领先的综合和布局布线工具,配合丰富的IP资源,简化用户设计步骤,方便用户直接调用调试,解决了复杂逻辑带来的资源不足的问题,为用户设计高质量产品提供有力保障。

审核编辑:汤梓红

-

DS601_EF3_系列器件介绍2022-10-27 0

-

DS501_ELF3L15器件手册2022-10-27 0

-

EF3系列器件概述2023-08-09 0

-

EF4系列器件概述2023-08-09 0

-

SALELF 3L15&SALELF 3L25&SALELF 3L45 FPGA数据手册2023-08-09 0

-

EF2、EF3、EG4的加载时对于时钟信号的质量要求是什么?2023-08-11 0

-

请问EF2、EF3系列最大功耗多少?2023-08-11 0

-

谁知道EF2/ EF3系列产品加载时间最快多久?2023-08-11 0

-

请问EF2/ EF3/EG4系列产品是否可以支持单电源供电?2023-08-11 0

-

索尼(sony)KV-EF29M80/KV-EF29M90/2010-07-24 1309

-

EF3器件概览2022-09-27 247

-

EF3 IO用户指南2022-09-27 252

-

EF3器件IO输入1.0V电平配置使用说明2022-09-27 256

-

EF3L15 IO用户指南2022-09-27 255

-

安路EF3L15 FPGA器件概览2022-09-27 218

全部0条评论

快来发表一下你的评论吧 !