史密斯圆图与阻抗匹配的调试

电子说

描述

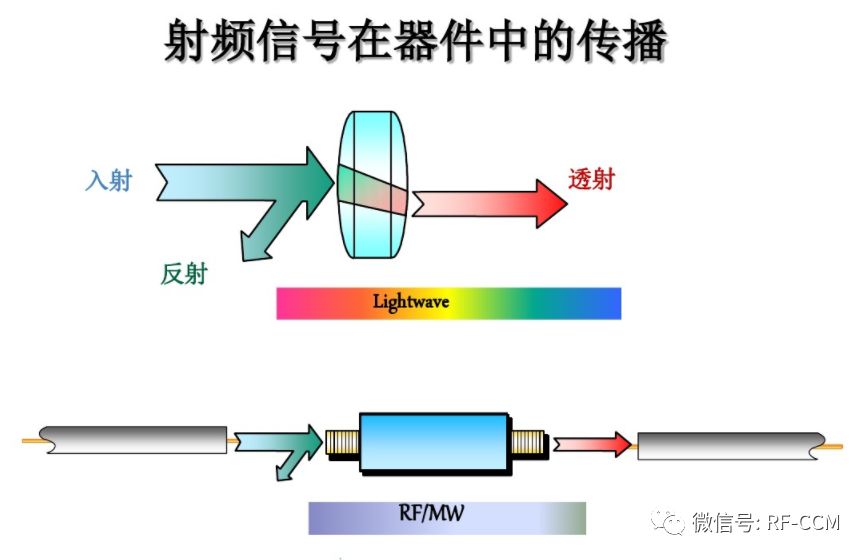

手机射频电路基本是平台厂商已经决定了架构和相关配合的射频器件,根据参考设计进行设计,重点在Layout和射频匹配的调试。射频参数很多,精湛的Layout技术和后期射频调试完成后这些参数都会符合规范要求。

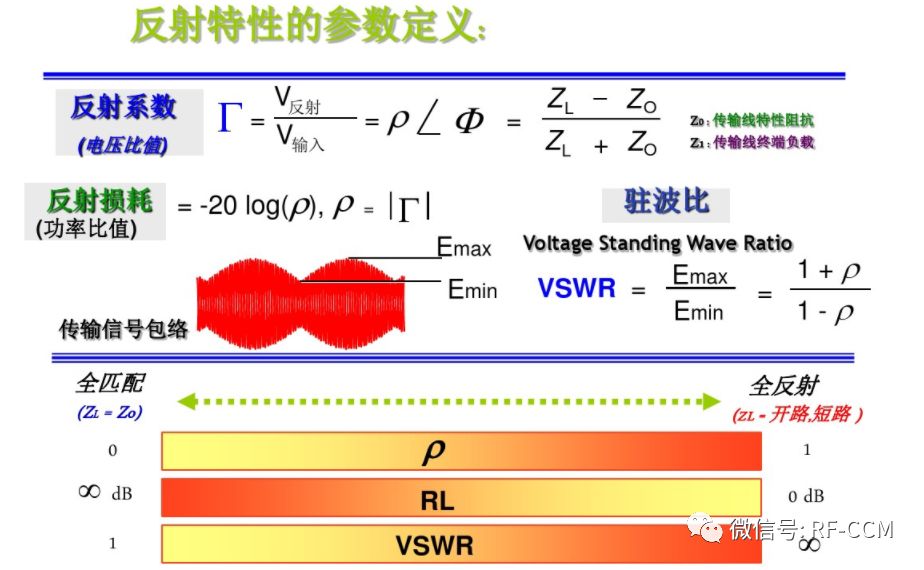

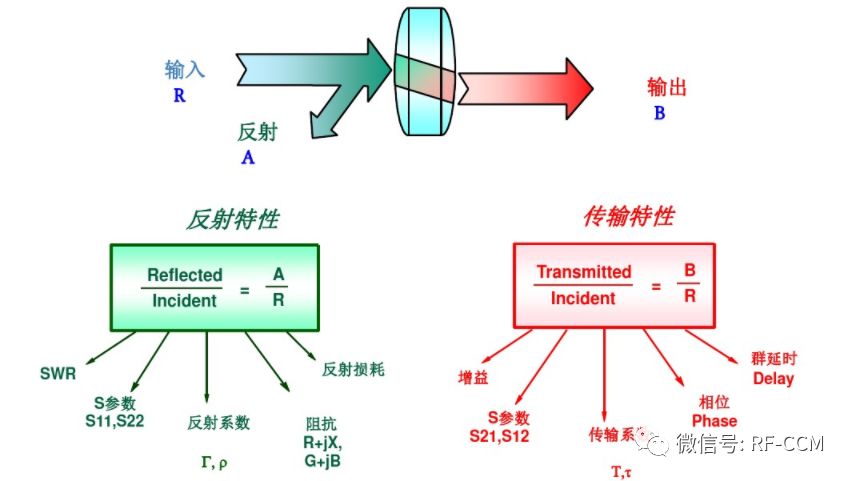

回波损耗(Return Loss): 入射功率/反射功率, 为dB数值

反射系数(Г): 反射电压/入射电压, 为标量

电压驻波比(Voltage Standing Wave Ration): 波腹电压/波节电压 ,从能量传输的角度考虑, 理想的VSWR为 1:1 ,即此时为行波传输状态,在传输线中,称为阻抗匹配 ;最差时 VSWR无穷大,此时反射系数模为1,为纯驻波状态,称为全反射,没有能量传输 。

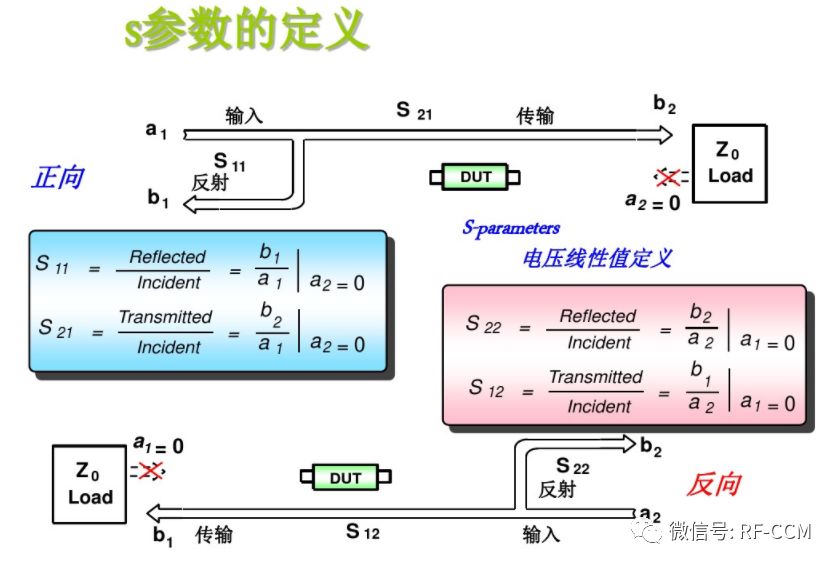

S参数

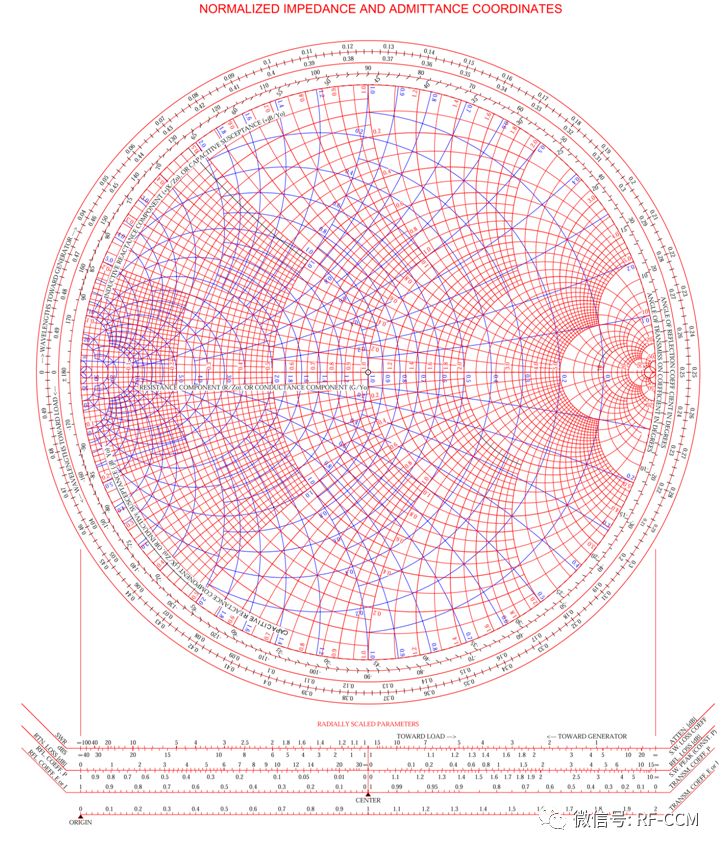

史密斯圆图 ( Smith Chart)

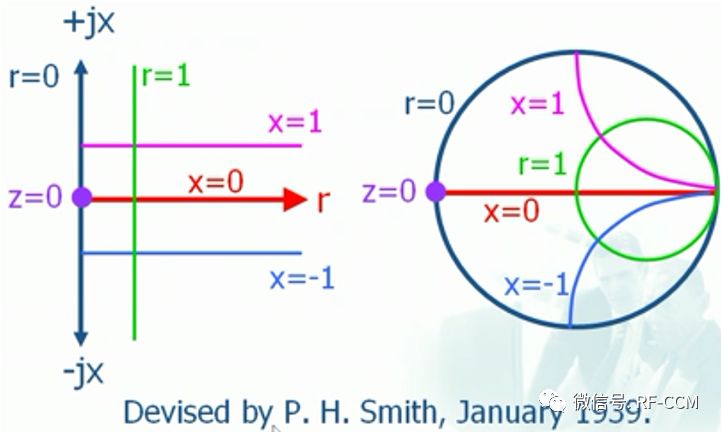

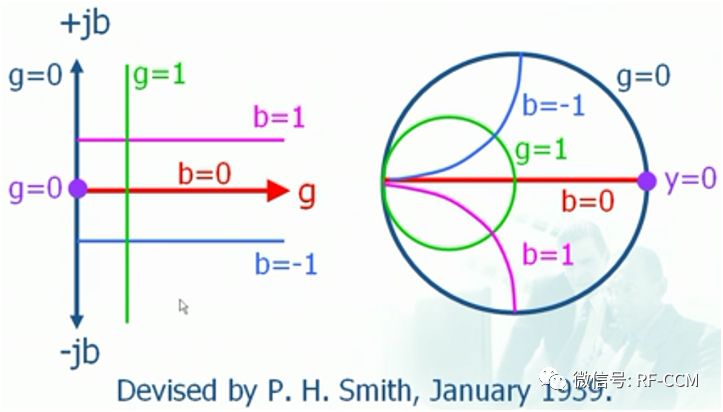

** Phillip Smith于1939年发明**

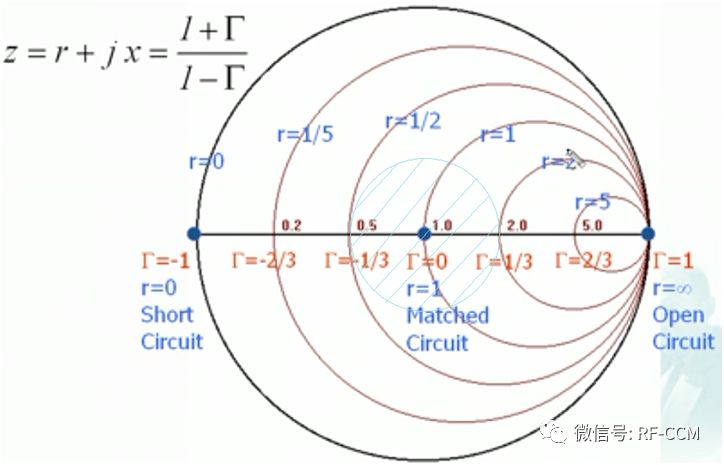

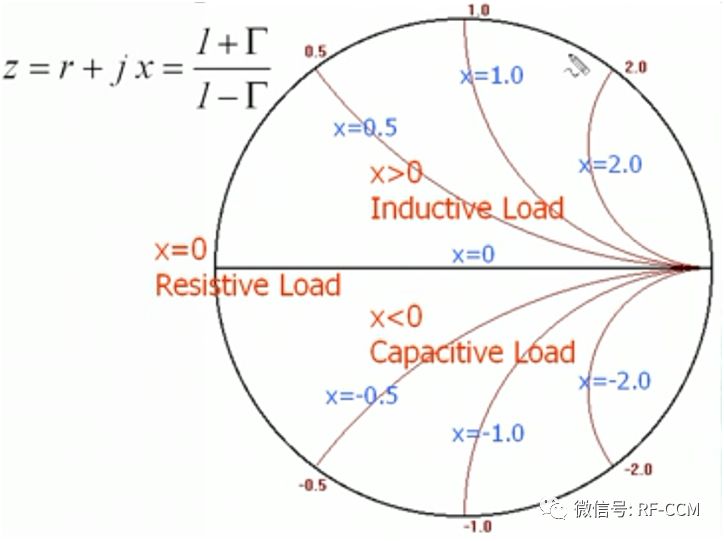

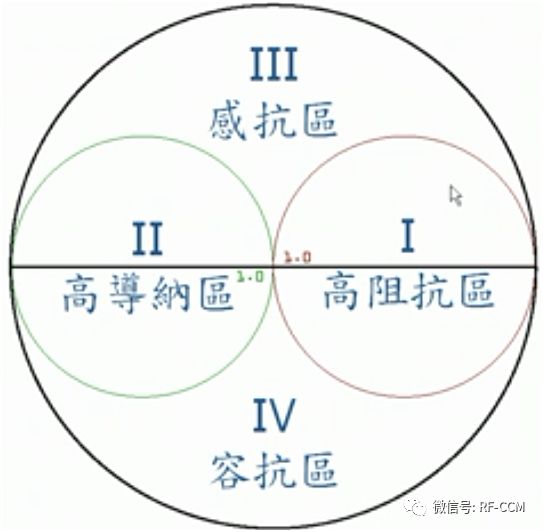

图中分为蓝色和红色两部分,其中:

蓝色部分为导纳图,导纳图用的比较少,在并联元件时候使用。

红色部分为阻抗图,在串联元件时候使用,通常使用中主要以阻抗图为主。

看到Smith Chart的时候的第一件事情是要想到反射系数

Smith Chart表示的就是反射系数。

Z=R+jX,射频电路里面的阻抗是个复阻抗;

R的取值范围为0~∞,j的取值范围为-∞~+∞

那么对于Z来说就会有无限的组合,用图表来表示是表示不完的,但是反射系数Γ****为 0< ** | Γ | < 1 ,即用一个半径为1的圆即可表示完所有的反射系数,且一个阻抗对应唯一的一个反射系数** Γ ,只要在Smith Chart中找到一个 Γ ,就可以通过实部r与虚补j的相交点确认该点的阻抗。所以聪明的前辈Smith,就发明了以反射系数来表示的史密斯圆图。

在SmithChart中使用归一化后的阻抗(归一化即Z/50=R/50+jx/50=z=r+jx),所以看到z=r+jx时候就要明白其表示归一化后的阻抗。

Smith Chart上半圆表示感性阻抗,下半圆表示容性阻抗。

匹配元件在Smith Chart上的移动方向

在设计匹配电路的时候,并联元件在 导纳圆上移动 ,串联元件在 阻抗圆上移动 ,电感元件向上半圆移动,电容元件向下半圆移动。

Constant R Circle

上图表示恒定阻抗的圆(实部)的阻抗为:

0.2=10Ω;0.5=25Ω;1.0=50Ω;2.0=100Ω;5.0=250Ω

利用这些恒定的阻抗圆可以估计附近的阻抗为多少,为不使用PC而评估阻抗提供便利。

最外圆 (黑色) 表示r=0即 Z=0+jx ,表示全反射,代表能量过不去,一定是有开路或短路的情况了,或者就是看过去的不是纯电感就是纯电容。这种情况在用VNA(矢量网络分析仪)调试匹配时候,如果RF Cable没有焊接好的时候经常碰到。

导纳图

在匹配使用到并联元件时候使用导纳图进行匹配设计

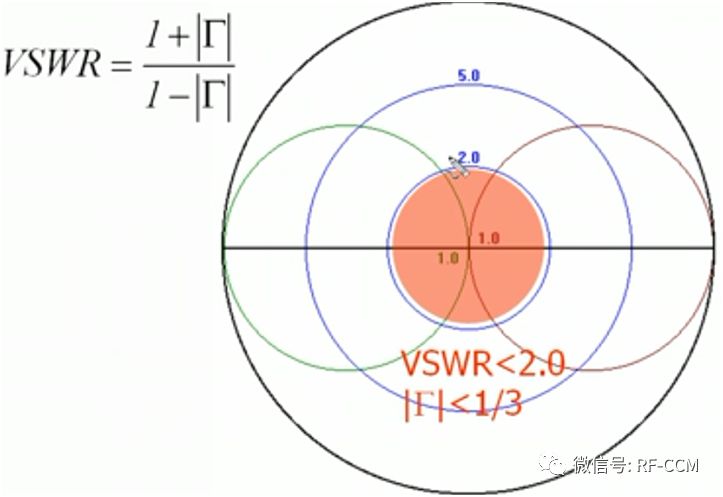

VSWRCircle

如何在实际中使用VSWR圆?

对RF设计的要求 VSWR < 2.0 , S11=1/3, 此即 Γ , 得到 中心圆部分 ,该圆中包含的部分就是符合 VSWR < 2.0 , S11=1/3的部分,这时候如果设计的band的所有点都落在该圆内的话就没太大问题了。

在用VNA测试的时候怎么估计band的点是否落在这个圆内呢?

设定要测试的Start Freq和Stop Freq,通过调节匹配,将整个band的点拉到该圆即可,估计圆的大小时候参考恒定阻抗的圆中0.5,1.0,2.0三个点,以1.0为中心,过0.5和2.0做圆,该圆即为符合 VSWR < 2.0 , S11=1/3的圆,这样就可不用PC而用心算来估计自己设计的RF电路是否符合要求。

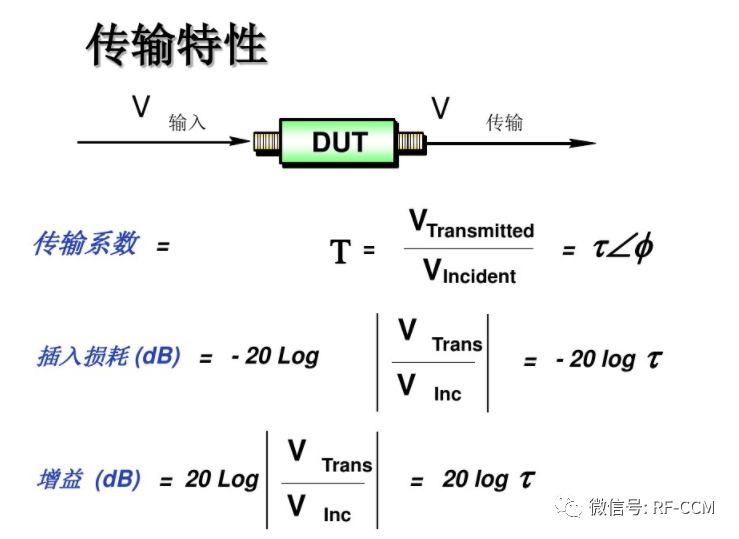

S21可以用来评估插损 (IL: Insertion Loss)的大小,就是“黑盒”的衰减。经验值从PA到RF Jack大概是3.2左右,当然 越小越好 。

射频电路要求

VSWR < 2.0

S11=1/3, 此即****Γ

S11ˊ(dB)=-9.54 ,通常要求为 -10 ,此即 RL, 将****Γ 做对数运算后 -20log(S11)=RL

相关公式:

Γ= (Z L -Z 0 )/(Z L +Z 0 **) **

** = (** | ** VSWR**** |** ** -1) / (** | ** VSWR**** |**** +1)**

VSWR=1+ | Γ | ** /1-** | Γ |

Z L =Z 0 *(1+Γ)/(1-Γ)

**Z0:特性阻抗(特征阻抗),RF的特征阻抗为50Ω **

归一化阻抗:

**z=r+jx=1+Γ/1-Γ=Z/50** **(** **Z=R+jX** **)**

** Γ=Γr+jΓx**

** 注意Γ是个复数,而|Γ|是Γ的模,不要混淆。**

Four Matching Regions of Smith Chart

阻抗落在不同的区域,能选择的匹配的方式就会受到限制。

感抗区和容抗区几乎都是高感抗和高容抗的。

Matching Network

调试的一些规律

高阻抗区即地I区,需要并联元件,即并联电容。

低阻抗区(高导纳区),即第II区需要串联元件,即串联电感。

看到阻抗的时候,可以拿这个阻抗和50Ω去比,大于50Ω或小于50Ω,通常就应该知道一开始的匹配元件应该是串还是并。

并联电容阻抗变小,串联电感阻抗变大。

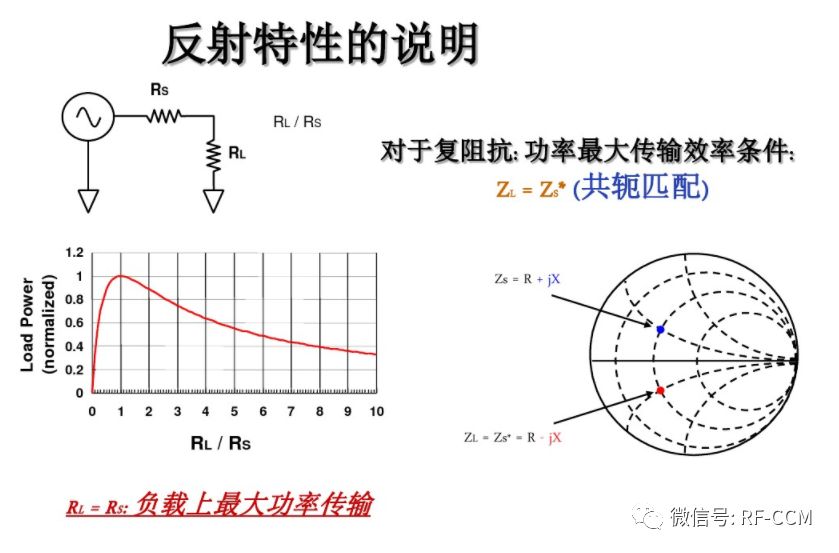

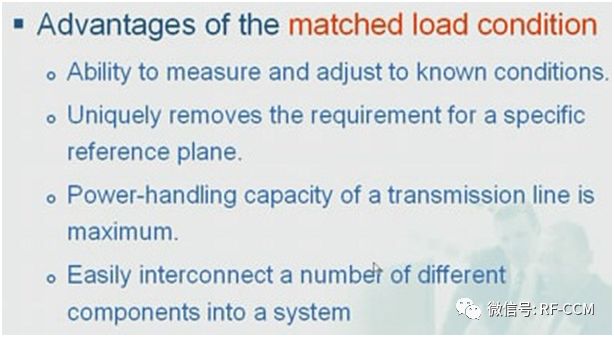

阻抗匹配实质就是使得复阻抗的实部相等,虚部对消。

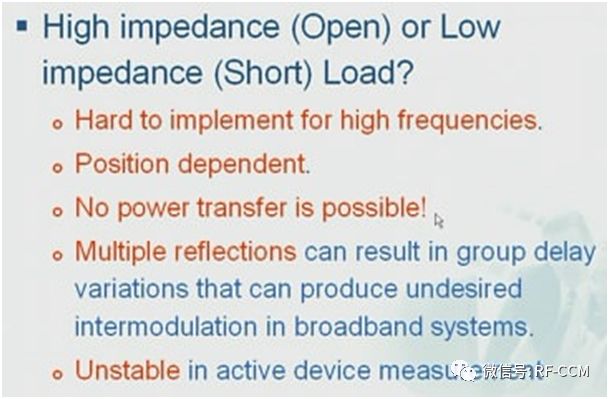

为什么要做阻抗匹配

对于传输线

Z 0 = √ L/C, 特性阻抗

Vp=1/ √ L/C ,相速

在传输线理论中若Δz≈0的话则可用KVL(基尔霍夫电压定律)来计算电路特性,传输线方程就是基于Δz≈0时候的KVL推导出来的,那么什么是Δz≈0,模拟业界认为是<λ/20时候。通常仿真过程在等效电路的时候,每λ/20等效为一个LC。

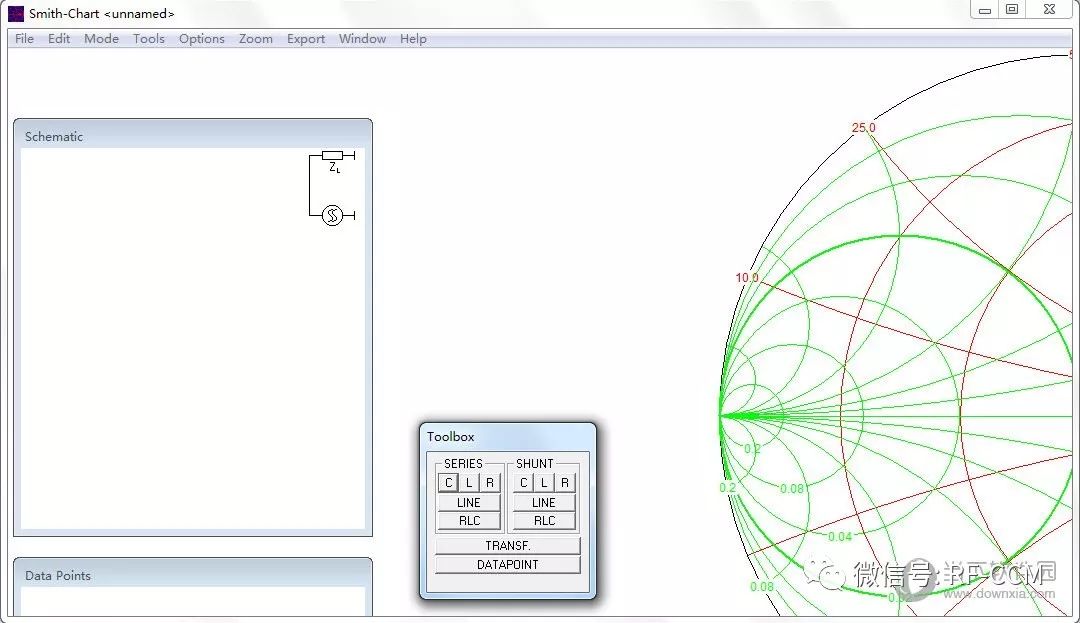

史密斯圆图计算工具

调试匹配非常有用

这个工具使用的时候,加入的元件是并联还是串联,电容、电感大小,在圆图上Z会有方向和步骤的进行移动。

电容或者电感决定了Z的移动方向,其大小决定了Z在圆图上走过的距离。

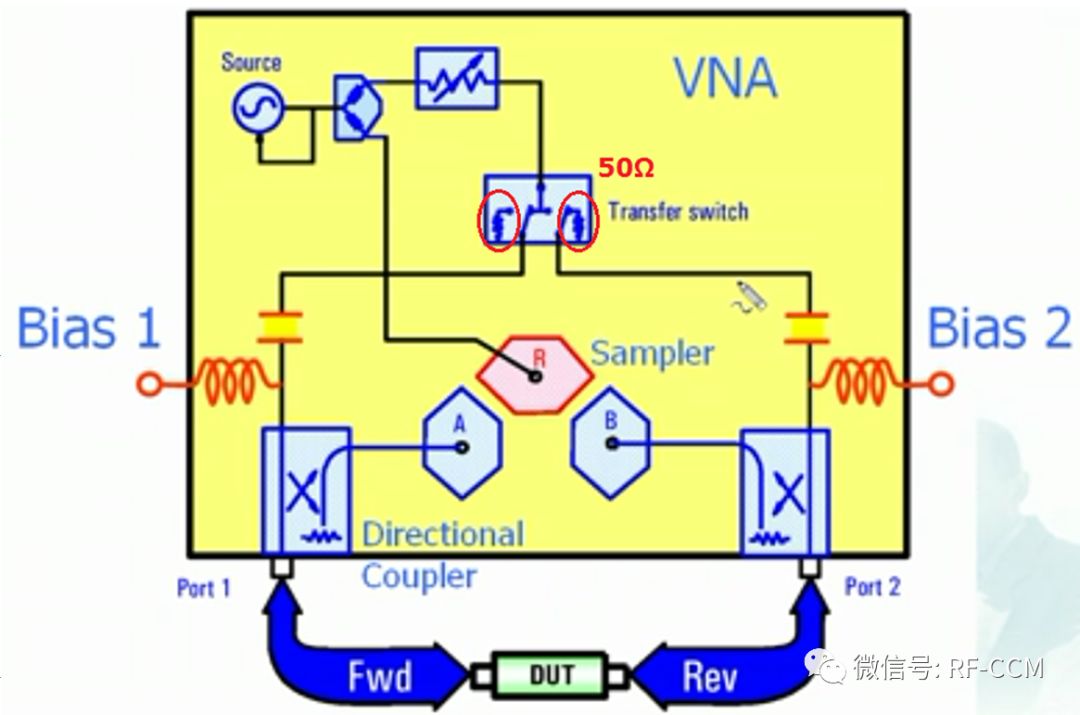

VNA(Vector Network Analyzer)简介

VNA是一个发射和测量接收设备,用来发射信号和测量经过电路后的信号,其输出是CW(Continue Wave连续波)信号,这就是导致为什么在WCDMA和CDMA电路用VNA调试后,有源测试时并不能总是得到与VNA调试结果完全相符的结果的原因,因VNA输出是CW信号,所以电路处理的是CW信号,而实际有源情况是电路处理的是类噪声信号,因此而产生偏差。其内部有50Ω点,在测试时候会让相关端口处于50Ω匹配状态,如下图示为VNA简图。

在用VNA测试芯片阻抗的时候总是会有一个问题困扰,就是测试端口网络S参数的前提是在测试某端口S参数的时候,其它端口需为50Ω匹配,不然不符合S参数的定义,且 芯片端口基本不会是50Ω的,实质是复阻抗形式,更多的时候表现为容性阻抗( 所以匹配中很多时候需要用到电感 ) 。

那么如何保证/确认在测试网络某端口的时候,保证其它网络端口为50Ω呢?对于微波系统来说,其本身就是按50Ω来设计的,系统某处已设计总有一个点是在50Ω的,所以可以将该系统50Ω之前的所有路径及器件均视为“黑盒”,对整个“黑盒”进行S参数的测试,对这个“黑盒”进行匹配。

WCDMA信号由于采用直接序列扩频,具有内在的类噪声特性,信号波动剧烈,峰均比远高于传统模拟系统的稳定信号和一般的 非扩频数字调制信号 (GSM 是非扩频信号,所以峰均比较小,即信号较稳定,所以在用传统网分测试时候效果好 ) ,而且 波动特性 ( 信号幅度概率分布 ) 与 基带编码 ( 码道数量和组合 ) 有直接关系。而传统网络分析仪的激励信号都是 CW 稳定信号, 可以反映器件的传统静态指标 (如用于器件筛选和维修诊断),但**无法反映器件在实际应用过程中通过真实**** WCDMA ** 信号所产生的质量变化 。所以用VNA调试完成后,需要在信令模式进行匹配的微调。

射频环境主要是要在屏蔽房中完成射频相关的工作,以防产生不必要的结果。

举例如WLAN Rx测试时候如果在普通场合,仪器发1000个package给DUT,而DUT计算PER的时候的总数比1000多,这就是内部噪声和外界干扰共同作用产生的结果,射频环境和规范测试很重要。

-

阻抗匹配与史密斯(Smith)圆图:基本原理2009-09-14 0

-

阻抗匹配与史密斯原图:基本原理2014-12-01 0

-

应用史密斯圆图工具进行阻抗匹配的实例[分享史密斯圆图工具]2016-11-21 0

-

利用史密斯圆图进行RF阻抗匹配设计2020-10-09 0

-

利用史密斯圆图作为RF阻抗匹配的设计指南2009-09-14 773

-

阻抗匹配与史密斯(Smith)圆图2009-09-29 950

-

阻抗匹配与史密斯圆图2010-07-10 702

-

阻抗匹配与史密斯(Smith)圆图: 基本原理2006-05-07 4405

-

射频阻抗匹配与史密斯圆图原理2016-05-04 1162

-

阻抗匹配与史密斯圆图的基本原理资料免费下载2019-05-27 1187

-

史密斯圆图和阻抗匹配原理解析2022-11-02 1664

全部0条评论

快来发表一下你的评论吧 !