ESD静电放电问题仿真分析

EMC/EMI设计

描述

“ 静电放电(Electorstatic Discharge,ESD)是指电荷瞬间从一个物体移到另一个物体上,形成一个电荷转移的过程的现象,即具有不同静电电势(电位差)的物体或表面之间的静电电荷转移。ESD会造成电子元件系统受到过度电性破坏,从而影响其电路功能,使电子产品工作不正常或无法工作。”

ESD现象所涉及的物理机制特别复杂,人工计算很难得到放电水平和防护器件性能参数的精确值,仅能通过测试验证的手段获得分析结果,但流片和打板验证耗费大量时间和成本,会使公司在激烈竞争中处于不利的地位。因此,引入合适的仿真模拟手段是十分有必要的。下面通过一个简单的案例描述Sigrity Speed2000 ESD仿真流程,看它可以如何帮助工程师在投产前进行ESD方面的模拟分析工作。

01

案例简述

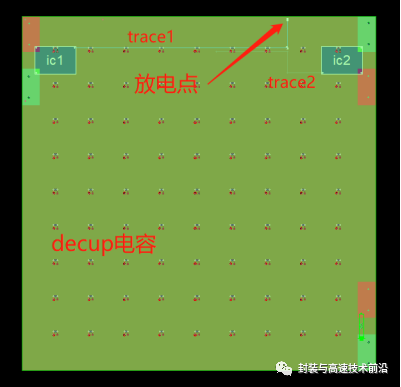

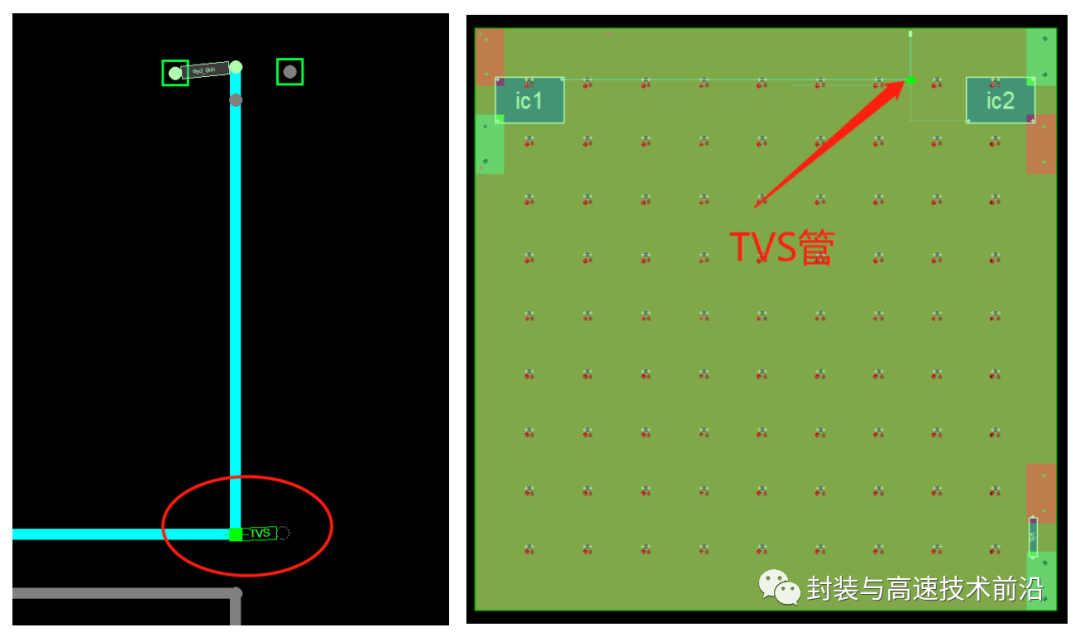

4层PCB板,放电点如下图所示,trace1、trace2分别连到top层的芯片ic1和ic2,信号网络分别为t0与t1,电源网络VDD,地网络GND,bottom层放置多个decup电容。

02

仿真方案

Step 1 :采用ESD枪模型,分析在不做任何ESD处理状态下芯片信号及电源管脚的电压波形。静电过程中不仅会影响放电pin所在trace1的电压,也会通过耦合影响电源和相邻trace2的电压,因此ic2的信号、电源一起仿真;

Step 2 :优化仿真,评估ESD电容添加与否的影响,分析TVS管的作用;

Step 3 :提取芯片管脚上的电压作为噪声,分析静电放电如何影响信号、电源,分析是否会导致信号电平无法识别等问题。

03

静电枪模型

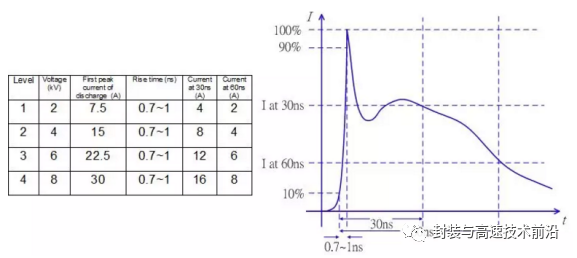

基于IEC-61000-4-2或者EN-61000-4-2 p.19标准定义放电模型,均是以人体放电模式HBM(Human Body Mode)模拟。

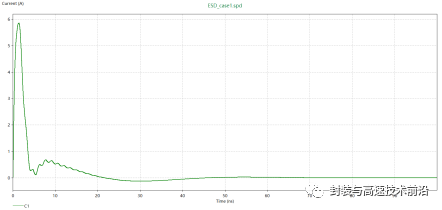

EMC标准是以电流波形来定义静电枪的输出。输出分两段:第一段的上升时间很短(0.71ns),但电流峰值极高(3.75A/KV),此段反映的是HBM放电时,手臂累积的静电荷瞬间放电的结果;第二段(1060ns)则反映身体累积电荷的释放结果。

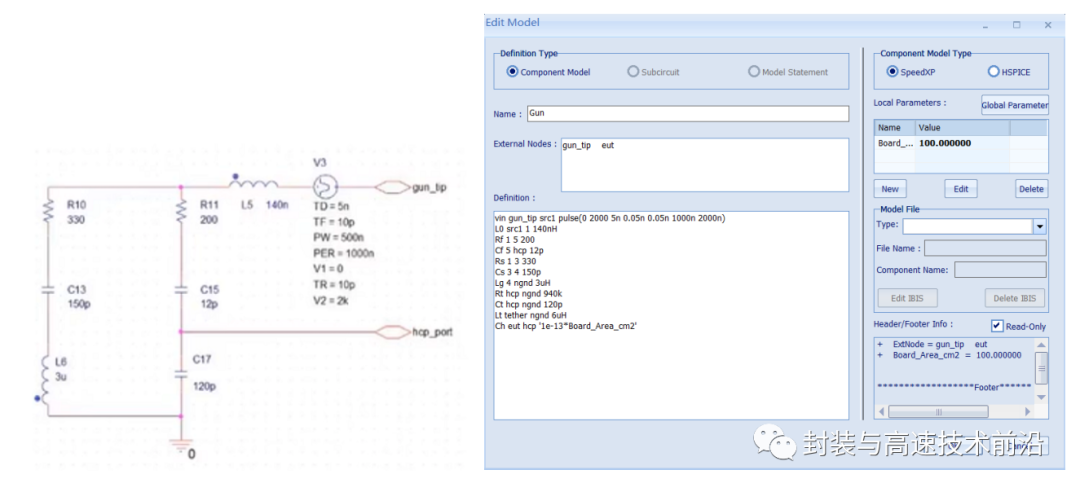

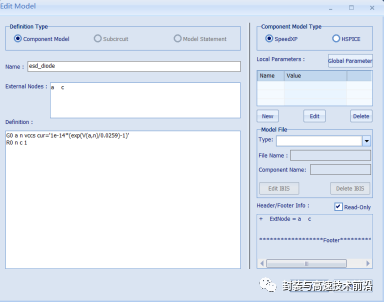

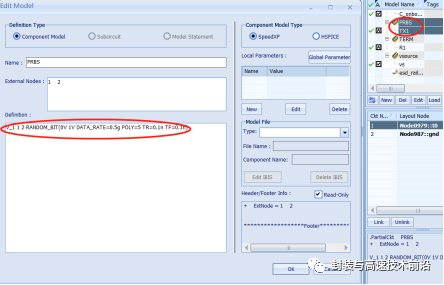

软件定义的枪模型模拟该电流波形,对板子进行激励,枪模型原理图和模型描述如下,为软件给出的缺省模型,无需工程师手动重新定义,当然也是可以在edit model界面修改模型参数或拓扑,定义属于自己的ESD枪模型。

04

仿真过程

- Step1——无ESD防护措施的仿真

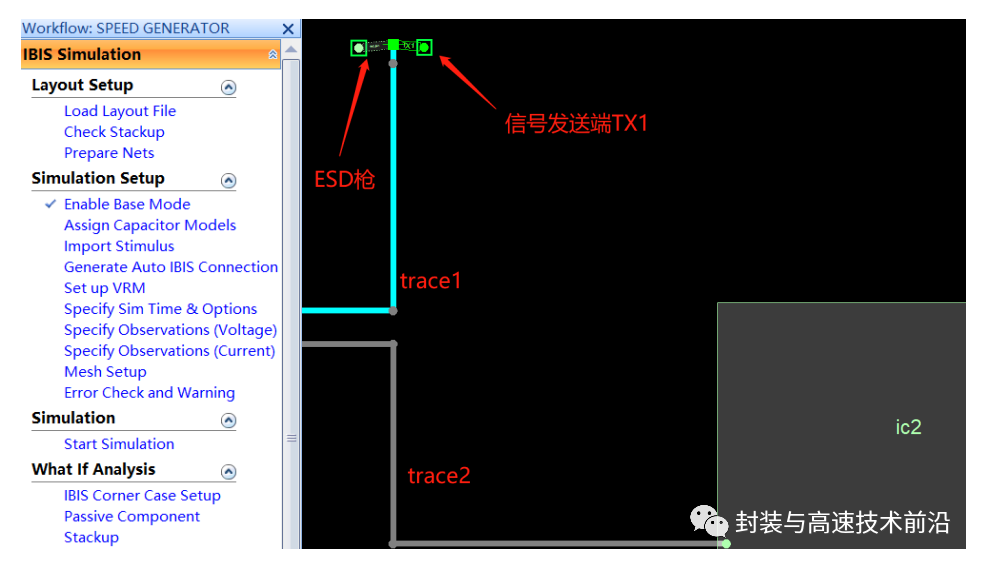

Speed2000的ESD Simulation流程如下:

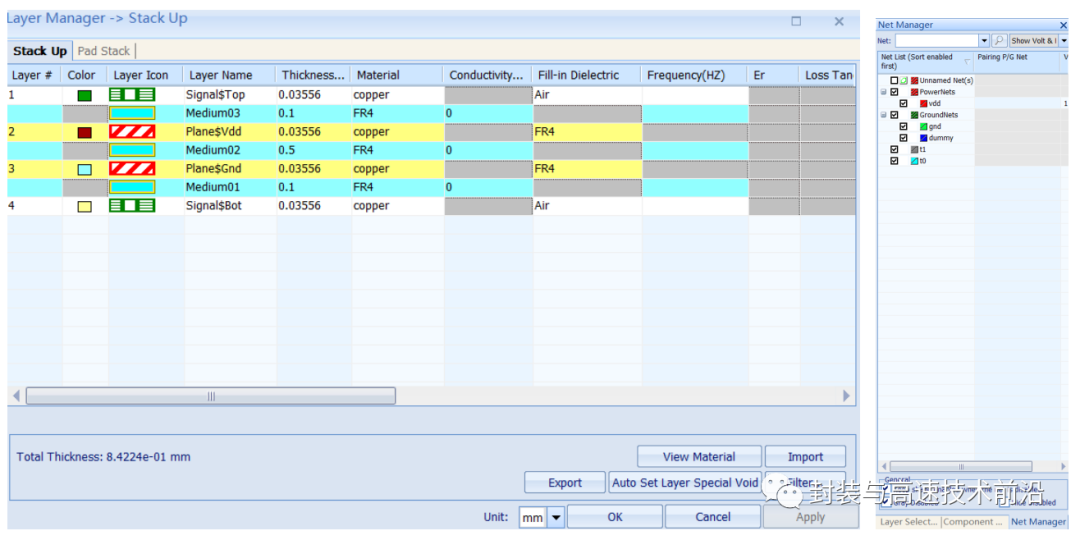

Layout层叠检查和设置、网络选择:

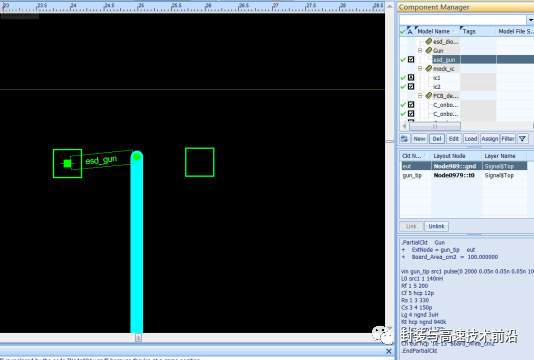

添加ESD枪模型(这里用默认参数),将ESD枪放置到layout中的放电处:

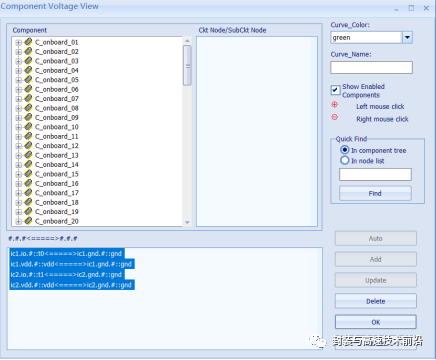

添加ic1和ic2的电源和信号管脚的电压观测点:

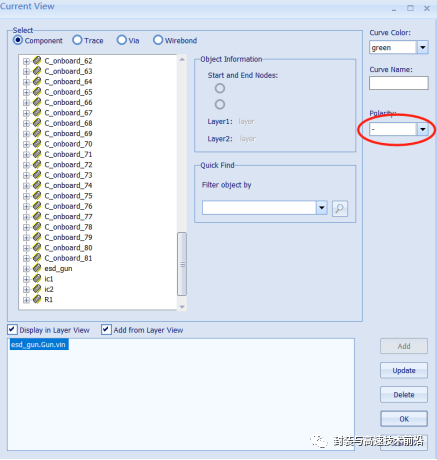

在ESD枪处添加电流观测点,以检查模型的电流波形是否符合要求:

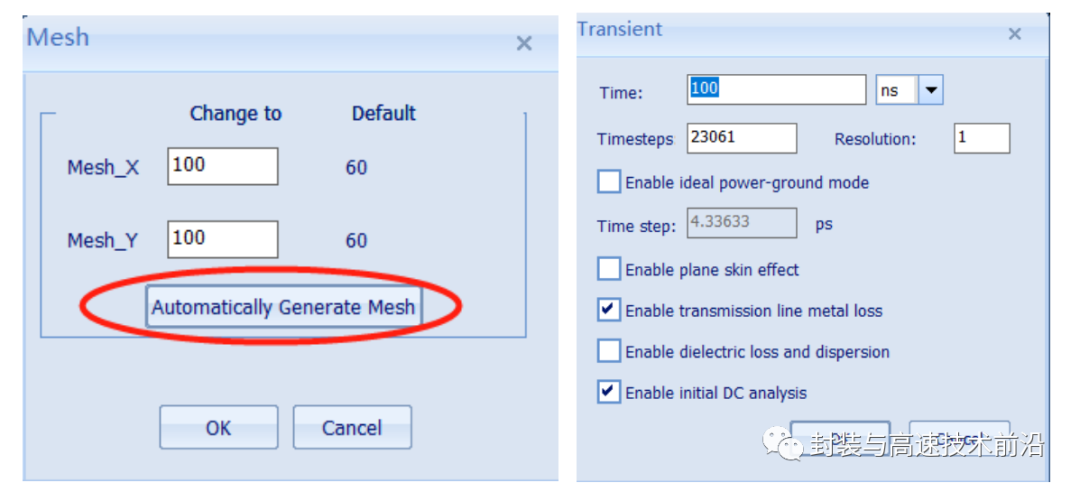

Speed2000的求解引擎为3D时域算法FDTD,因此需要设置Mesh,选择自动生成Mesh,设置仿真时间和其他仿真选项:

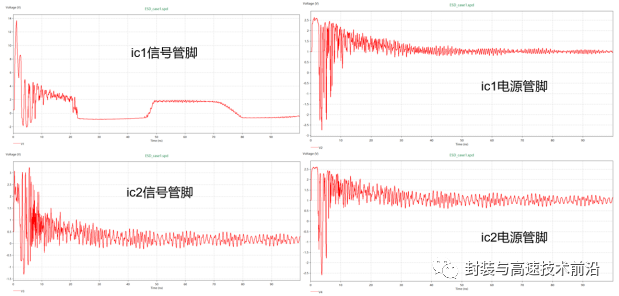

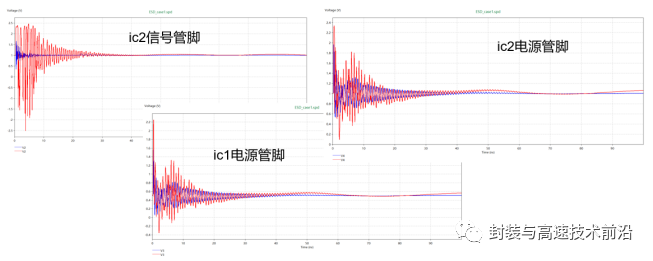

仿真结果如下,ic1信号管脚为直接放电信号,ic2信号管脚为走线耦合信号,ic1和ic2电源管脚评估电源平面耦合结果。可以看到在不加静电处理措施的情况下,ic1芯片信号管脚的电压在ESD冲击下可以达到14V,而且在首次放电结束后会有很多振荡产生,这些噪声信号都将使信号电平被淹没其中而不被识别。而通过耦合到达ic2信号管脚处的噪声为3V左右。另外通过平面耦合到两个芯片电源管脚的噪声大概在2.5V。

ESD枪电流波形如下,验证满足标准的要求。

Step2——ESD防护措施仿真

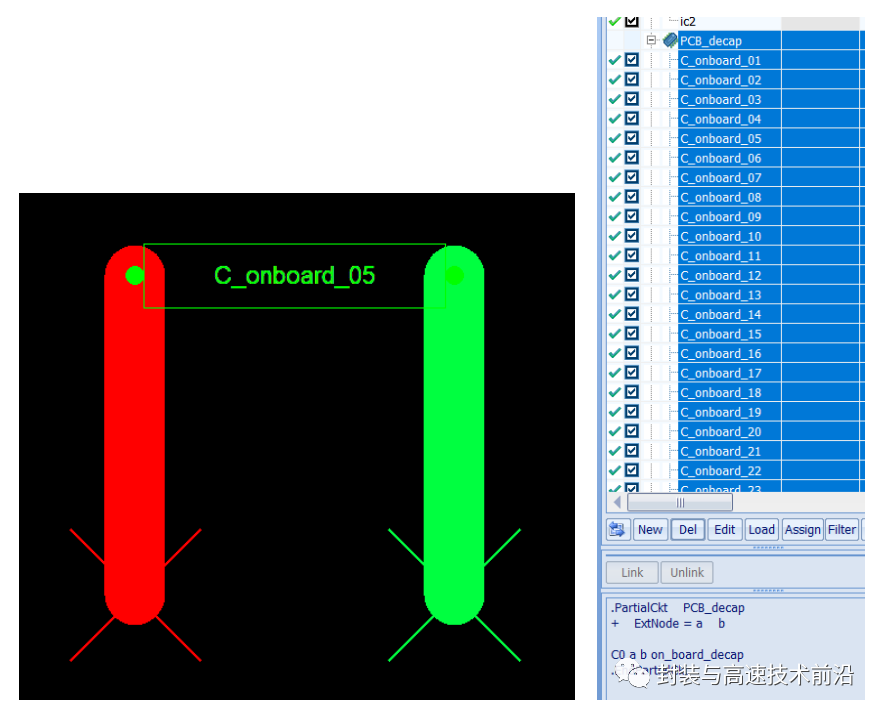

使能所有电容(相当于添加ESD静电电容),观察仿真结果

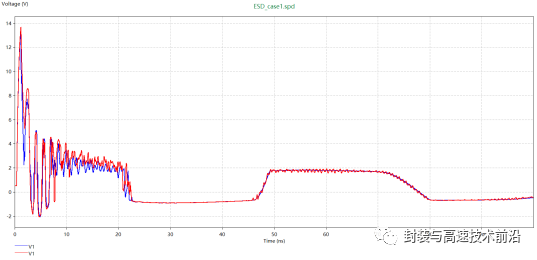

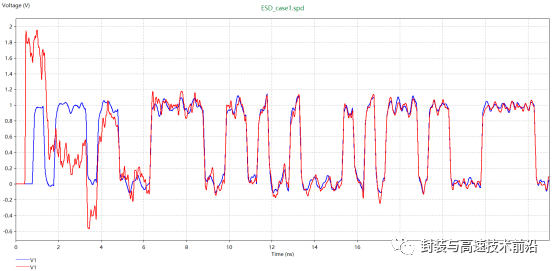

仿真结果如下,蓝色曲线为加ESD电容、红色曲线为没加ESD电容情况下,信号t0的芯片ic1管脚处电压,可见ESD电容的添加可以降低放电噪声幅度,该案例降低1V左右,并且去耦电容可以减轻噪声的振荡现象。

然后我们在放电处附近添加TVS器件,使用软件自带缺省模型,评估优化效果。放置位置如下:

TVS模型描述如下:

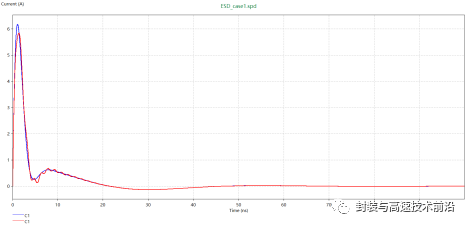

ESD枪电流波形的仿真结果如下,蓝色为加tvs管、红色为没加tvs管的放电处电流曲线,可见是否添加TVS管对放电处的电流波形影响不大。

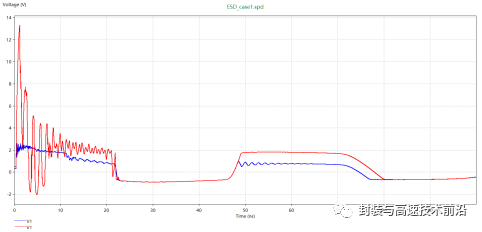

下图是噪声结果,蓝色曲线为加tvs管、红色曲线为没加tvs管情况下,信号t0的芯片ic1管脚处电压,可见添加TVS管可以大幅降低芯片端的放电噪声,该案例从14V降低到2V左右,使得噪声达到可控的程度。

下面为ic2通过走线耦合的信号管脚处噪声对比和ic1/2电源管脚噪声对比,蓝色均为加tvs管的结果,红色为没加tvs管的结果,ic2信号管脚处耦合的噪声明显减少,两个芯片电源管脚处耦合的噪声也有所降低。

Step3——ESD噪声影响SI的仿真

利用Speed2000的IBIS Simulation可以仿真放电噪声如何影响信号质量。其他设置同ESD仿真流程,在下图所示位置添加信号激励源TX1:

信号激励源模型如下图所示,本案例添加的是500Mbps的PRBS随机码

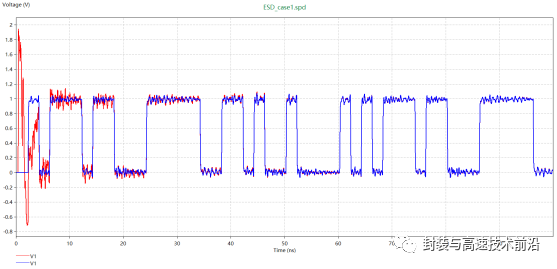

仿真结果如下,蓝色为加tvs管、红色为没加tvs管情况下,信号接收端芯片ic1管脚处电压,可见放电噪声可以造成前期波形的严重变形,影响电平判断,而加了TVS管后就修复了这一问题。

将信号源的速率提升到2Gbps,仿真结果如下,蓝色为加tvs管、红色为没加tvs管的结果,可见随着速率的提升,放电噪声的影响会越大,而且TVS管的作用再次得到验证。

05

仿真结论

本文通过一个案例的形式,描述了Sigrity Speed2000是如何针对ESD问题进行仿真分析,ESD仿真流程可以帮助我们模拟出放电电压能够达到什么程度,提供ESD激励枪模型,可以很方便地进行放电模拟;支持添加电容、TSV等防护器件,评估防护电路设计的效果;另外,还能配合IC器件的IO模型或定义信号激励源,评估ESD产生的噪声对信号完整性影响的程度,帮助原理、PCB、仿真工程师在投产前对ESD影响和ESD防护设计做出合理判断。

-

ESD静电放电影响及分类2024-01-03 311

-

ESD静电放电2018-09-21 0

-

电缆对静电放电的影响分析2020-10-23 0

-

ESD静电放电产生的原理和危害2021-01-06 0

-

什么时静电放电(ESD)2021-03-26 0

-

静电放电(ESD)原理2011-03-23 4812

-

手机ESD静电放电问题盘点2015-11-10 4036

-

ESD静电放电设计 20页 1.0M2016-05-24 758

-

静电放电ESD的介绍和原理及解决方法概述2019-01-07 4115

-

静电放电ESD的原理和详细资料概述2019-04-04 2117

-

模拟分析静电放电(ESD)事件2019-08-11 8997

-

MT-092:静电放电(ESD)2021-03-21 764

-

【电磁兼容技术案例分享】静电放电(ESD)整改案例分析2023-11-03 850

-

ESD静电放电有几种主要的破坏机制 ESD失效的原因2024-01-03 2073

-

ESD静电放电的原理和危害2024-01-03 518

全部0条评论

快来发表一下你的评论吧 !