GPIO输入主要电路结构

描述

1. 数字输入输出的定义

数字输入或输出(英语:Digital Input or Digital Input),又叫开关量输入或输出,只有通和断二种状态,离散状态。

常见的数字输入有GPIO,GTA等

本文主要说明GPIO

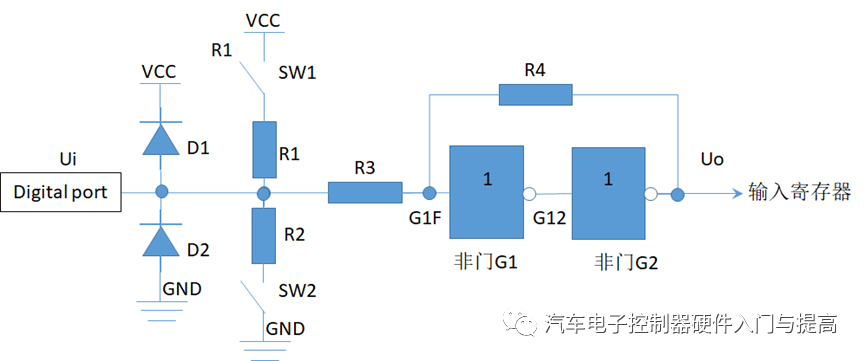

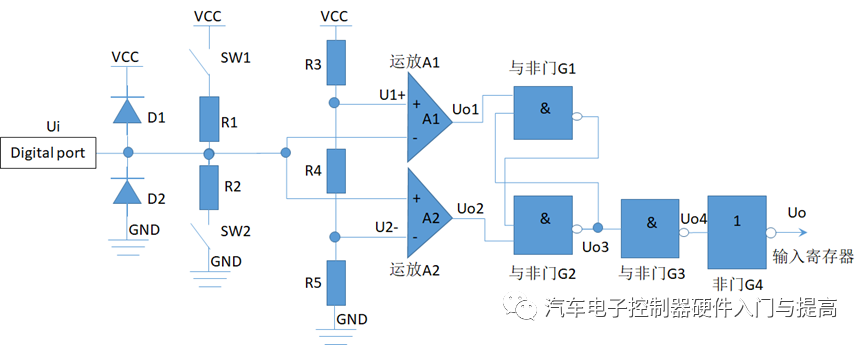

2. GPIO输入主要电路结构

施密特触发器分TTL门电路、CMOS门电路和运放比较器三种种分别说明

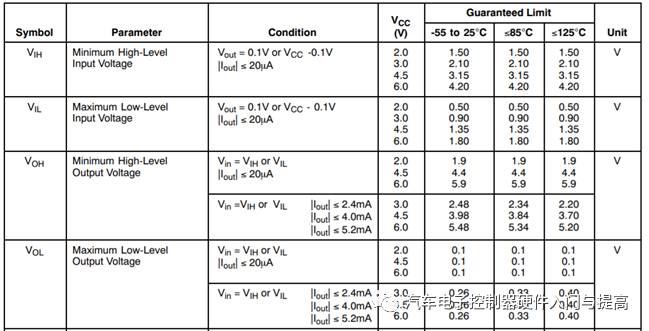

2.1.TTL施密特触发器下的GPIO主要电路结构

其中

1)R1,R2为内部弱上拉或弱下拉,阻值很大,一般为100k以上;

2)D1,D2为嵌位二极管,可以嵌位到-V(D2)到VCC+V(D1)之间,如果选择硅管二极管,可以嵌位到-0.7V~5.7V;

3)R3=100Kohm,R4=1000kohm

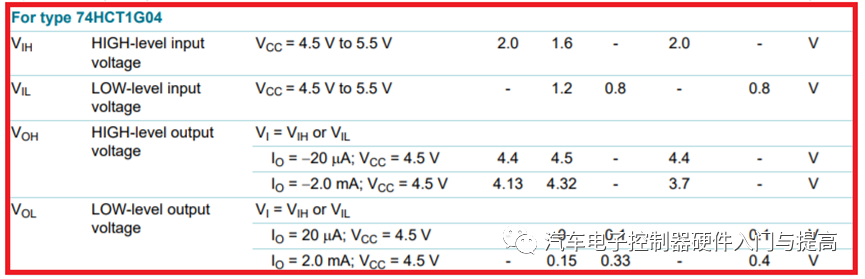

2.2.TTL施密特触发器下的GPIO阈值计算

非门以74HCT1G04举例,此处不讨论R1,R2接入情况

1)当外部信号Ui未接入时,真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 悬空 | 0 | 1 | 0 |

| 电压值 | 悬空 | 悬空 | 4.4V | 0.4V |

UG1F=Ui*R4/(R3+R4)

2)当外部信号Ui输入上升,UG1F>=UIH=2.0V时,

Ui>=UG1F*(R3+R4)/R4=UIH*(R3+R4)/R4=2*(100+1000)/1000=2.2V

即VDIH=2.2V

假设Ui从0V升到4.2V

真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 1 | 1 | 0 | 1 |

| 电压值 | 4.2V | 2.8V | 0.4V | 4.4V |

3)当外部信号Ui输入从5V下降时,

(Uo-Ui)/(R3+R4)=(Uo-UG1F)/R4,即UG1F=(Ui*R4+Uo*R3)/(R3+R4)<=0.8V

Ui=

其中R3=100K,R4=1000K,Uo=4.4V,解得:Ui<=0.44V,即VDIL=0.44V

假设Ui从4.4V降到0.3V

真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 0 | 0 | 1 | 0 |

| 电压值 | 0.3V | 0.67V | 4.4V | 0.4V |

经过一段时间后,稳定后的

UG1F=(UiR4+UoR3)/(R3+R4)=(0.310+0.41)/11=0.1V

真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 0 | 0 | 1 | 0 |

| 电压值 | 0.3V | 0.1V | 4.4V | 0.4V |

综上所述,VDIH=2.2V ,VDIL=0.44V

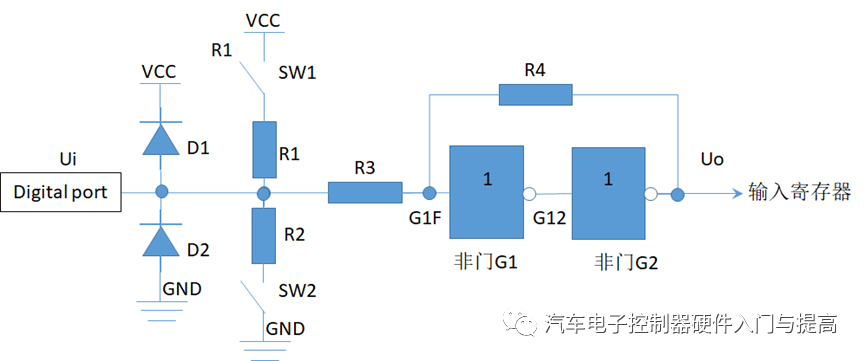

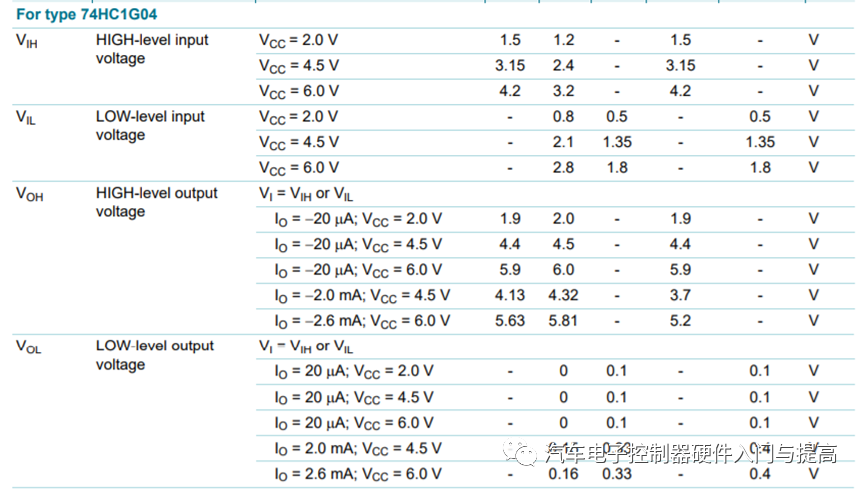

2.3.CMOS施密特触发器下的GPIO主要电路结构

其中

1)R1,R2为内部弱上拉或弱下拉,阻值很大,一般为100k以上;

2)D1,D2为嵌位二极管,可以嵌位到-V(D2)到VCC+V(D1)之间,如果选择硅管二极管,可以嵌位到-0.7V~5.7V;

3)R3=100Kohm,R4=3000kohm

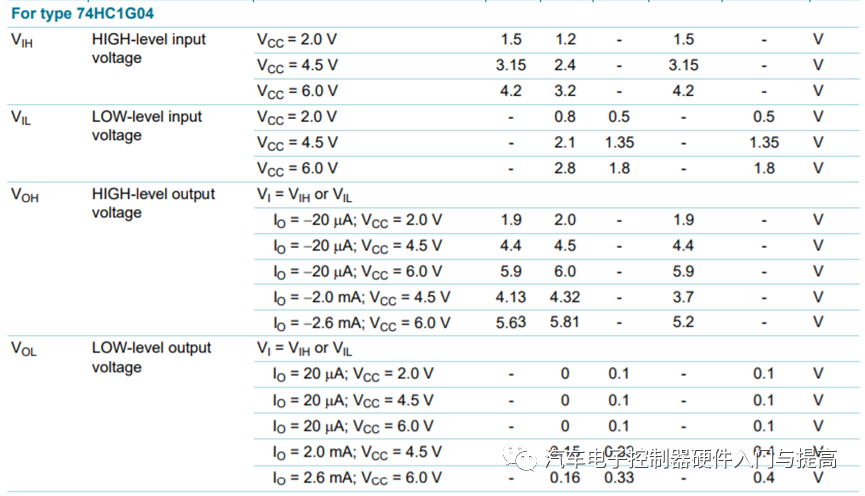

2.4.CMOS施密特触发器下的GPIO阈值计算

非门以74HC1G04举例,此处不讨论R1,R2接入情况

假设供电VCC=5V,那么UIH=3.5V,UIL=1.5V,VOH=4.5V,VOL=0.5V.

1)当外部信号Ui未接入时,真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 悬空 | 0 | 1 | 0 |

| 电压值 | 悬空 | 悬空 | 4.5V | 0.5V |

UG1F=Ui*R4/(R3+R4)

2)当外部信号Ui输入上升,UG1F>=UIH=3.5V时,

Ui>=UG1F*(R3+R4)/R4=UIH*(R3+R4)/R4=3.5*(100+3000)/3000=3.62V

即VDIH=3.62V

假设Ui从0V升到4.2V

真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 1 | 1 | 0 | 1 |

| 电压值 | 4.2V | 3.62V | 0.5V | 4.5V |

3)当外部信号Ui输入从5V下降时,

(Uo-Ui)/(R3+R4)=(Uo-UG1F)/R4,即UG1F=(Ui*R4+Uo*R3)/(R3+R4)<=0.5V

Ui=

其中R3=100K,R4=3000K,Uo=4.5V,解得:Ui<=0.37V,即VDIL=0.37V

假设Ui从4.2V降到0.2V

真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 0 | 0 | 1 | 0 |

| 电压值 | 0.3V | 0.67V | 4.5V | 0.5V |

经过一段时间后,稳定后的

UG1F=(UiR4+UoR3)/(R3+R4)=(0.33000+0.5100)/3100=0.31V

真值表为以下

| 信号 | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 逻辑值 | 0 | 0 | 1 | 0 |

| 电压值 | 0.3V | 0.31V | 4.5V | 0.5V |

综上所述,VDIH=3.62V ,VDIL=0.37V

2.5.运放比较器施密特触发器下的GPIO主要电路结构

其中

1)R1,R2为内部弱上拉或弱下拉,阻值很大,一般为100k以上;

2)D1,D2为嵌位二极管,可以嵌位到-V(D2)到VCC+V(D1)之间,如果选择硅管二极管,可以嵌位到-0.7V~5.7V;

3)R3=R4=R5=10Kohm

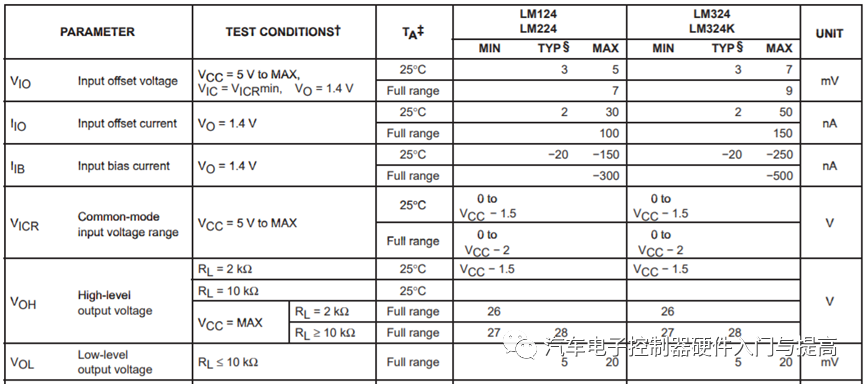

2.6.运放比较器施密特触发器下的GPIO阈值计算

利用运放A1和A2的虚短特性,

U1+=VCC*(R4+R5)/(R3+R4+R5)=5*2/3=3.33V

U2+=VCCR5/(R3+R4+R5)=51/3=1.67V

与非门以74HC00DR2G举例,此处不讨论R1,R2接入情况

假设供电VCC=5V,那么UIH=3.5V,UIL=1.5V,VOH=4.5V,VOL=0.5V.

非门以74HC1G04举例

假设供电VCC=5V,那么UIH=3.5V,UIL=1.5V,VOH=4.5V,VOL=0.5V.

运放比较器以LM324为例,工作量程V+-V-最大7mV,也就是说V+-V-超过7mV,运放进入放大饱和区间,此时输出VOH=3.5V,即为比较器功能。

1)当外部信号Ui未接入时

U1+=3.33V>Ui,那么U01=3.5V

Ui

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | 悬空 | 1 | 0 | 1 | 0 | 1 |

| 电压值 | 悬空 | 3.5V | 0.005V | 4.5V | 0.5V | 4.5V |

2)当外部信号Ui输入上升,Ui<1.67V时,

U1+=3.33V>Ui,那么U01=3.5V

Ui

假设Ui=1.0V

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | - | 1 | 0 | 1 | 0 | 1 |

| 电压值 | 1.0V | 3.5V | 0.005V | 4.5V | 0.5V | 4.5V |

3)当外部信号Ui输入继续上升,3.33V=>Ui>=1.67V时,

U1+=3.33V>Ui,那么U01=3.5V

Ui>=U2-=1.67V,那么U02=3.5V

假设Ui=3V

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | - | 1 | 1 | 1 | 0 | 1 |

| 电压值 | 3V | 3.5V | 3.5V | 4.5V | 0.5V | 4.5V |

4)当外部信号Ui输入继续上升,Ui>=3.33V时,

U1+

Ui>=U2-=1.67V,那么U02=3.5V

假设Ui=4.2V

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | - | 0 | 1 | 0 | 1 | 0 |

| 电压值 | 4.2V | 0.005V | 3.5V | 0.5V | 4.5V | 0.5V |

综合1)~4)可以得出VDIH=3.33V(Uo由4.5V变为0.5V)

5)当外部信号Ui输入从5V下降到, Ui>3.33V

U1+=3.33V>Ui,那么U01=0.005V

Ui>=U2-=1.67V,那么U02=3.5V

假设Ui=4.2V

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | - | 0 | 1 | 0 | 1 | 0 |

| 电压值 | 4.2V | 0.005V | 3.5V | 0.5V | 4.5V | 0.5V |

6)当外部信号Ui输入继续下降,3.33V=>Ui>=1.67V

U1+=3.33V>Ui,那么U01=3.5V

Ui>=U2-=1.67V,那么U02=3.5V

假设Ui=3V

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | - | 1 | 1 | 0 | 1 | 0 |

| 电压值 | 3V | 3.5V | 3.5V | 0.5V | 4.5V | 0.5V |

7)当外部信号Ui输入继续下降,Ui<=1.67V

U1+=3.33V

Ui<=U2-=1.67V,那么U02=0.005V

假设Ui=1.2V

真值表为以下

| 信号 | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 逻辑值 | - | 0 | 0 | 1 | 0 | 1 |

| 电压值 | 1.2V | 0.005V | 0.005V | 4.5V | 0.5V | 4.5V |

综合1)~4)可以得出VDIL=1.67V(Uo由0.5V变为4.5V)

-

二.GPIO输入输出及延迟函数2021-11-24 432

-

STM32的GPIO输入模式和输出模式结构2019-05-21 0

-

高阻态是什么?GPIO管脚在高阻态输入模式下的等效结构模式2022-01-25 0

-

04、STM8通用输入输出口(GPIO)2021-11-26 465

-

STM32的8种GPIO输入输出模式2021-11-26 1723

-

STM8S自学笔记-006 GPIO输入:按键输入 与 按键滤波2021-12-05 472

-

GPIO通用输入输出2021-12-20 573

-

STM32-(基于STM32F4)-GPIO基本结构-输入/输出模式2022-01-13 325

-

GPIO内部结构及输入输出模式2022-10-08 3941

-

通用输入输出GPIO是什么2023-03-23 1009

-

i.MX6ULL学习笔记:GPIO按键输入捕获2023-04-06 704

-

一文详解GPIO的输入配置2023-06-14 3085

-

瑞萨e2studio----GPIO输入检测2021-11-03 839

-

GPIO输出主要电路结构2023-07-02 1113

-

五种宽带接入主要技术浅析2023-11-10 104

全部0条评论

快来发表一下你的评论吧 !