“去耦”电容其作用究竟是什么?

电子说

描述

“去耦”电容并没有去除来自电源网络或某个“神秘来源”耦合过来的噪声,从这个角度讲,“去耦”电容的命名存在一定的误导性。如果电源上存在噪声,一般情况下是由于负载电路需要从电源网络汲取较大的电流,而电源传输网络(PDS)的输出阻抗较高造成的。结果是当负载电流较大时,终端产生了电压降,从而导致了纹波。而“去耦”电容在电源传输网络中的真正作用是:在保证自身阻抗较小的同时,当负载电路切换状态需要电流时,为其提供支持。懂了这一点,就会比较容易理解为何每个电源传输网络都需要使用不同容值的多个电容。

电容的类型

通常来说,电容的容值越大,尺寸也越大。在大多数情况下,电容的物理尺寸、封装类型、材质及安装方式比容值更重要。所有的电容都有寄生参数,而寄生参数决定了电容在不同频率下是否有效。

最常见的“去耦”电容包括以下几种类型:

铝电解电容

如下图所示,无论是贴片的还是直插的,只要在PCB上看到的“直直挺立”的电容,基本上都是铝电解电容。

铝电解电容的特点是:

- 容值大、体积大、耐高压、ESR低

- 由于电解液的挥发,使用时间久会导致容值下降

铝电解电容在高压应用中(比如48V的DC-DC输入端)非常常见。但由于尺寸较大的原因,在低压场景中较少使用。

钽电容

钽电容是高性能的代名词,也属于电解电容的一种,使用金属钽做介质,而非电解液,因此很适合在高温下工作。美系厂家(Kemet, AVX)的钽电容喜欢用黄色,而日系厂家(SANYO)喜欢用黑色。

钽电容的特点是:

- 1 uF到1000 uF、中等尺寸(体积小且能达到较高容量)、耐压低、ESR低

- 价格贵,选择少,但失效率低

随着铝电容的推广,在很多低端场合,钽电容有被替代的趋势。但在高端领域,比如军工,钽电容仍是当之无愧的王者。在某些高端的消费电子领域,也可以看到钽电容的身影。比如下图中的高端显卡:

陶瓷电容

陶瓷电容是最小也最便宜的。最近受疫情影响,缺货严重的MLCC(Multi-layer Ceramic Capacitor)就是片式多层陶瓷电容器英文缩写。

陶瓷电容有各种不同的尺寸、容值和耐压值。根据电解质材质的不同,陶瓷电容也分很多品类。比如使用X7R做为电解质的陶瓷电容质量较好,它有极高的电压稳定性及很低的ESR,且温度范围比较宽,非常适合滤波、去耦的场合;又如以Y5V做为电解质的陶瓷电容,它的特点是介电常数较高,因此单位容量的电容值较高,从这个角度讲应该比较适合“去耦”的应用场合,但其稳定性较差,随温度及电压变化大,因此不是很好的“去耦”选择。

陶瓷电容的特点是:

- 容值小、尺寸小、ESR低

- 价格最低、可靠性高

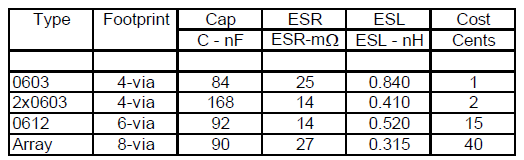

排容

排容是由若干个电容排列而成的电容阵列,应用于对元器件空间要求严格的PCB,如手提电脑,PDA,手提电话等,特别适用于输入,输出接口电路。从性能上讲,排容可以降低电容的ESL。但排容的价格至少10倍于同等容值的陶瓷电容(以0603为例)。如果为了省钱,并联两个0603的陶瓷电容同样可以达到一个排容的ESL。

排容的特点是:

- 节省PCB空间,阵列式的触点可以使ESL非常低

- 价格贵

电容等效电路

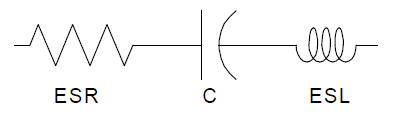

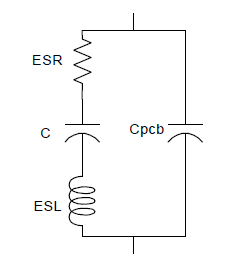

下图是一个去耦电容的等效电路:

可以看到,任何一个电容都会存在两个寄生参数,可以等效为一个串联电阻ESR(Equivalent Series Resistance)以及一个串联电感ESL(Equivalent Series Inductor)。

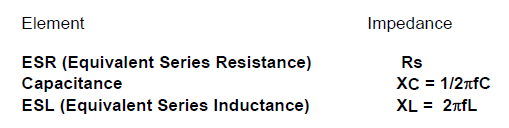

ESR、电容、ESL的阻抗如下:

因此,去耦电容的有效阻抗计算公式为:

串联谐振

由上述公式可得,当达到串联谐振频率f,使得XL=Xc时,电容的阻抗最小,即ESR的阻值。当频率高于谐振频率时,电容呈现出电感的特性。

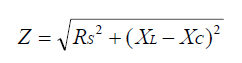

下图是一个1 uF的0603陶瓷电容的频率-阻抗曲线:

串联谐振频率在3.5 MHz。超过3.5 MHz后,电容的阻抗取决于ESL。

并联谐振

如果PCB使用了电源平面对,则还需要考虑平面电容与PCB表面所有其他电容互相作用而在某个频率产生的阻抗尖峰(Impedance Hole),该频率会大于串联谐振频率(因为平面电容通常大于PCB上的电容),我们称其为并联谐振频率。

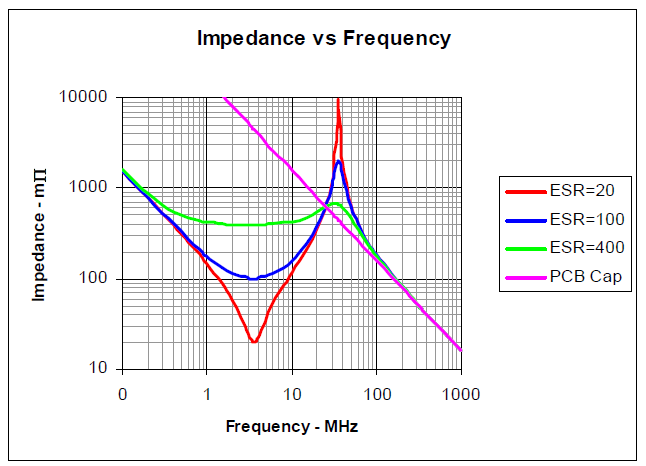

下图是PCB板上的电容等效模型:

在高频的时候,电容“C”相当于短路。并联谐振频率发生在XL(陶瓷电容的ESL)及XC-PCB(平面电容阻抗)相等的时候。

在并联谐振频率处,电路的阻抗幅度与陶瓷电容的ESR成反比:

如果ESR非常小,则阻抗会变得非常大。典型的问题出现在几百MHz的时候,如果并联谐振频率正好等于时钟或者某个信号的谐波频率,则阻抗会变得很大。

因此,在选择电容时,必须要考虑ESR在一个合理的区间内:ESR要足够小以保证低频时的频率特性,但同时需要足够大以抑制并联谐振频率时的阻抗尖峰。

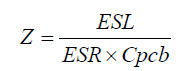

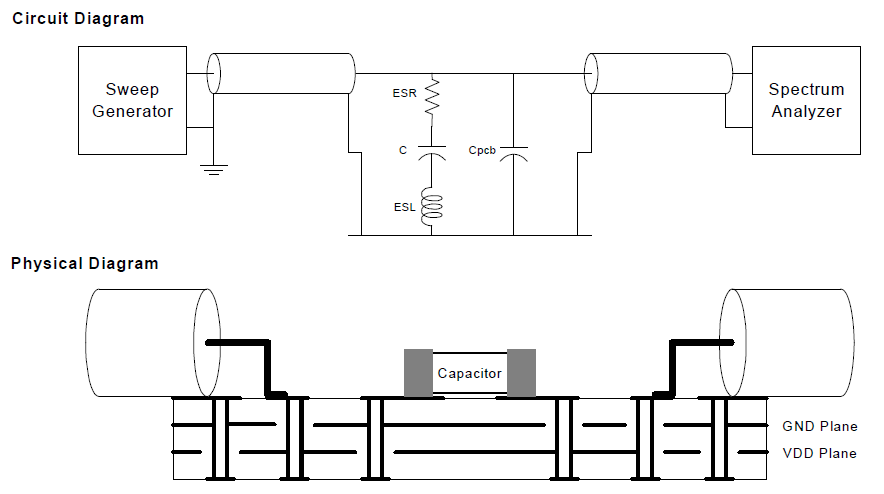

下图为1 uF的0603陶瓷电容及PCB平面电容为10 nF时的频率-阻抗曲线:

图中展示了不同ESR陶瓷电容在串联谐振频率及并联谐振下的阻抗。粉红色的曲线为PCB平面电容。可以看到并联谐振时的阻抗总是高于PCB平面电容阻抗本身。当ESR为20毫欧时,在并联谐振频率35.6 MHz处,阻抗尖峰达到了9.5欧姆。

去耦电容特性测量

下图为测量“去耦”电容特性的参考电路及实际测试的情况:

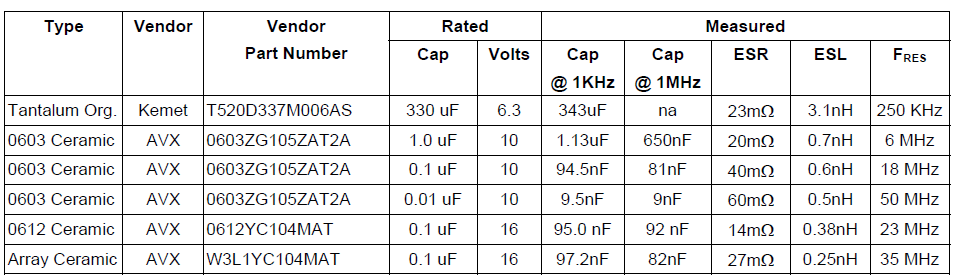

下图为常用去耦电容的特性:

最后一列Fres为电容的串联谐振频率,超过这一频率,电容就会表现为感性,其阻抗就会迅速变大。以上数据来源于电源平面与装配去耦电容层非常接近的情况,电容的焊盘到电源平面的过孔长度只有11 mils。

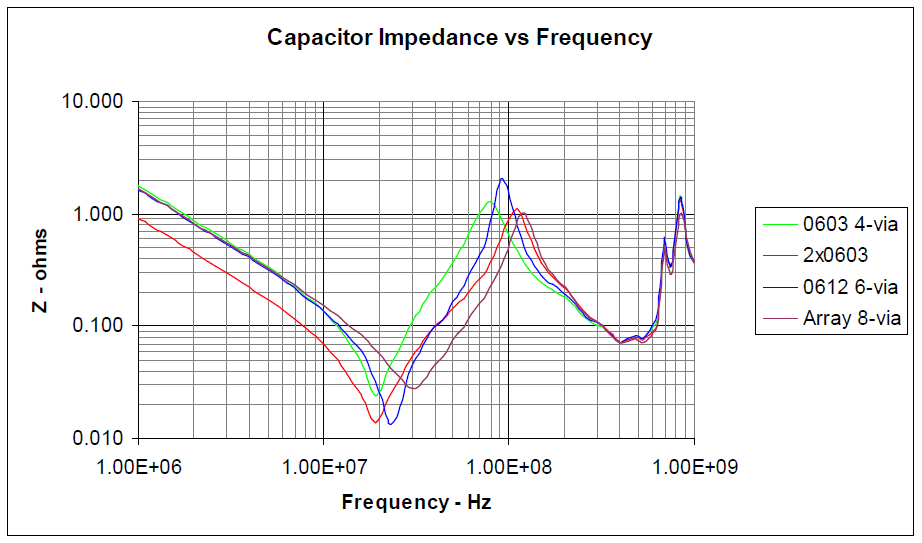

下图是不同3种不同类型电容的频率响应曲线:

所有电容的容值都为0.1 uF,由于测试板的电容焊盘到电源平面的过孔长度略大(30 mils),因此测出的ESL与上表相比略大:

平面电容

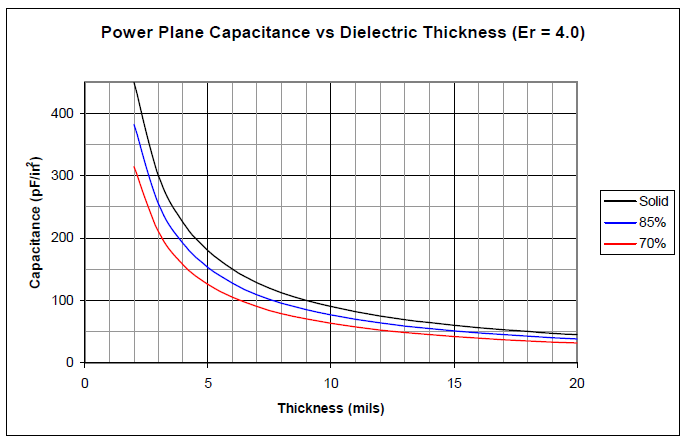

从上面的表格中可以看到,即使使用了容值仅为0.01 uF的电容,其串联谐振频率也仅能达到50 MHz。如果频率更高,就无法为负载提供低阻抗的路径了。这时,就必须使用电源平面对。关于电源平面对,在上一章节已经介绍过,这里不再赘述。再强调一下结论:

当VDD与GND的电解质厚度为3 mils时,电源平面电容为每平方英寸300 pF。如果考虑到AntiPad或者过孔到平面的间距,有效容值约为85%左右;对于BGA器件,由于存在较多的过孔,其有效容值只能达到70%左右。

去耦电容的摆放

开始这个话题前,先明确一个概念:电源平面对的ESL远小于普通电容(篇幅原因,不再详细分析原因)。

所有人都告诉我们,去耦电容应尽可能接近芯片的电源和地。这个结论是不是绝对的呢?

其实更正确的说法应当是:如果不存在电源平面(对),去耦电容应尽可能接近芯片的电源和地。如果存在合理设计的电源平面(即存在平面电容),去耦电容摆放的位置并不会造成太大的影响,考虑如何更方便地进行走线或者装配,比电容的位置更重要。

下图是一个电容测试板,有8个平面、6个信号层及2个外层。使用配合测量的电源/地平面容值为15.77 nF。测试板的左侧是两根焊在PCB上的同轴电缆引线,用于测量。

由于电源平面对的感抗很低,电容的摆放位置并没有那么重要,此时更应该考虑的是过孔的长度(表面到地平面)以及电源平面到IC的距离。

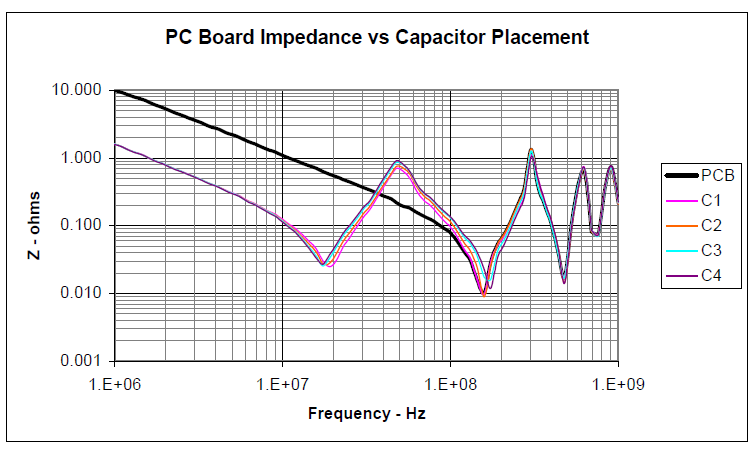

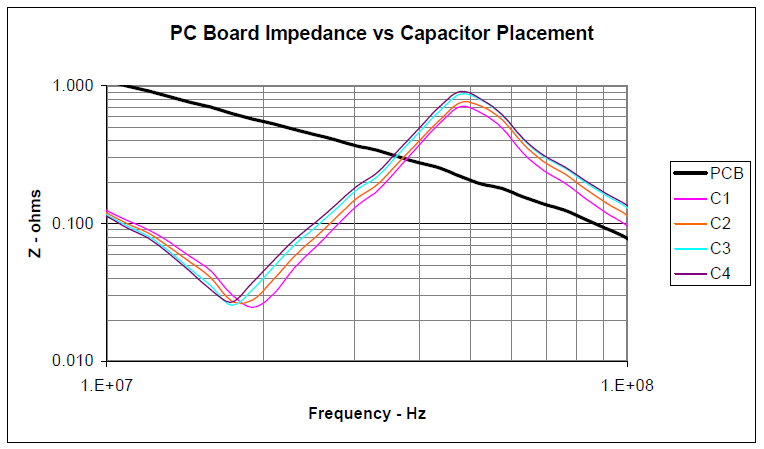

为了验证电容在不同位置的效果,我们沿着板长的方向,每隔2.5''摆放一个0.1 uF的0603电容,下图是实际测出的在不同位置摆放电容时阻抗-频率曲线:

放大细节:

可以看到,电容不同的位置只是使串联谐振频率偏移了8%左右;而并联谐振频率几乎没有差异。可见,在电源平面/地平面设计良好的情况下,去耦电容摆放的位置并没有太大的影响。

-

图解:IGBT究竟是什么?2020-08-10 0

-

S参数究竟是什么?2021-03-01 0

-

我们仿真DDR究竟是仿真什么2021-03-04 0

-

电感饱和究竟是什么2021-03-11 0

-

真正软件定义无线电究竟是怎样的?2021-05-14 0

-

IIoT究竟是什么?传感器在IIoT中的关键作用是什么?2021-05-21 0

-

分贝究竟是什么?如何去理解它?2021-05-31 0

-

一文读懂eMMC究竟是啥?2021-06-18 0

-

SLC、MLC、Parallel NOR Flash等究竟是什么意思?2021-06-18 0

-

spec究竟是什么?有谁可以分享一下吗2021-06-21 0

-

无片外电容LDO究竟是什么?2021-06-22 0

-

retain,copy与assign究竟是有什么区别呢2021-09-30 0

-

linux内核的“头”究竟是什么?2022-11-15 699

-

串口究竟是什么呢?2023-04-12 16153

全部0条评论

快来发表一下你的评论吧 !