CMOS图像传感器类型及3D堆叠

MEMS/传感技术

描述

CMOS图像传感器根据像素排列方式可以划分为面阵CMOS图像传感器和线阵 CMOS 图像传感器:

1)面阵CMOS图像传感器

面阵CMOS图像传感器的像素按照二维矩阵的形式进行排列,在成像过程中可以直接获取一幅完整的二维图像。

光学尺寸是面阵 CMOS 图像传感器感光区域对角线的长度,由分辨率和像素尺寸共同决定。由于镜头光学利用率等历史原因,业内所称的 1"(即 1 英寸)CMOS 图像传感器的对角线长度为16mm,而非 25.4mm 。

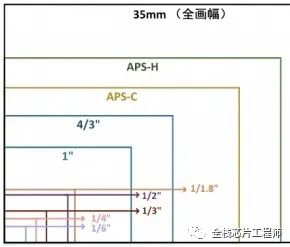

常 见 的 光 学 尺 寸 为 :1/6"、1/4"、1/3"、1/2"、1/1.8"、1"、4/3"、APS-C、APS-H、35mm(像素面积 36mm x 24mm)全画幅等,示意图如下:

根据光学尺寸的大小,面阵CMOS图像传感器可以分为光学尺寸>APS-C、光学尺寸介于 1"与APS-C之间、光学尺寸≤1"等三类。

2)线阵 CMOS 图像传感器

线阵CMOS图像传感器的像素按照一维排列,通过在垂直于像素线方向上对匀速运动的物体进行扫描,从而获得二维的图像。

线阵CMOS图像传感器一般有单线或多线,每线的分辨率,如 2K、4K、8K、16K 是其最主要的指标,一般分辨率越高,成像性能越好,单价越高。线阵 CMOS 图像传感器已广泛应用于工业检测、印刷品检测、物流扫码、铁路检测等场景。

采用了时间延迟积分(TDI)技术的线阵CMOS图像传感器,因其灵敏度极高、成像速度极快,在高端半导体检测与量测、DNA 基因测序、工业检测、高分辨率高速成像等场景中具有不可替代的重要地位。

3)堆栈式芯片架构

堆栈式芯片架构是在传统正照式、背照式架构基础上的进一步升级,将原本在一片晶圆上的像素矩阵和电路区域,分别置于两片晶圆上,并将两片晶圆绑定在一起。堆栈式架构的出现使得 CMOS 图像传感器的像素和电路可以进行独立设计和优化,例如电路设计可使用更先进的工艺制程,从而提升电路性能;像素设计可以使用普通工艺制程,有效控制成本。

另外堆栈式架构的像素填充系数可以达到 100%,从而提升量子效率和灵敏度。目前堆栈式芯片架构已广泛应用于高端消费类产品,在可预见的未来,采用堆栈式架构的 CMOS 图像传感器将逐步在其它领域得到更广泛应用。

图像拖影是Rolling shutter卷帘快门图像传感器的大问题,除了Global shutter全局曝光图像传感器外,三层堆叠的图像传感器开始出现:

像素层:90nm

DRAM:LPDDR4,30nm

逻辑层:40nm

三层堆叠的图像传感器能以超过960FPS的速度捕捉慢动作画面。

堆叠方案让芯片的大小减少了30%以上,增大了靶面,提高了像素分辨率。像素仍然用各家打磨多年的成熟工艺,逻辑层用先进工艺完成自动对焦等ISP功能、AI加速功能,提高PPA竞争力。

特别的是,传统的堆叠式CMOS图像传感器光电二极管、像素晶体管在同一背照像素层。

堆叠通过TSV技术,在芯片上钻孔,再加入导电介质形成通道,从而完成芯片之间电信号传递通道。

审核编辑:汤梓红

-

CMOS图像传感器简议2018-10-29 0

-

CMOS图像传感器的结构及工作原理2018-10-31 0

-

基于CMOS图像传感器的视频采集系统设计2018-11-01 0

-

新型CMOS图像传感器设计2018-11-14 0

-

IBM进军CMOS图像传感器2018-11-19 0

-

IBM将提供CMOS图像传感器代工服务2018-11-20 0

-

CMOS图像传感器数据采集系统2019-04-26 0

-

cmos图像传感器的应用2020-06-20 0

-

3D传感器如何为车内安全保驾护航?2020-07-29 0

-

3D传感器有哪些类型2020-12-09 0

-

AR0237IR图像传感器推动3D成像技术的发展2020-12-16 0

-

CMOS传感器在3D视觉/感测和度量中的应用2021-02-22 0

-

如何去提高CMOS图像传感器的图像质量?2021-04-20 0

-

CMOS图像传感器,CMOS图像传感器是什么意思2010-03-02 2852

-

堆叠图像传感器在图像传感器架构演进方面的最新成果2022-07-10 1218

全部0条评论

快来发表一下你的评论吧 !