MIPI CSI-2 RX Subsystem IP介绍和PHY实现浅谈

电子说

描述

MIPI CSI-2 RX Subsystem IP实现MIPI CSI-2 v2.0协议以及底层的MIPI D-PHY v2.0协议, 这个IP是用来抓取来自MIPI CSI-2 摄像头的视频流, 把该视频流输出到AXI4-stream的接口, 进行下一步处理.

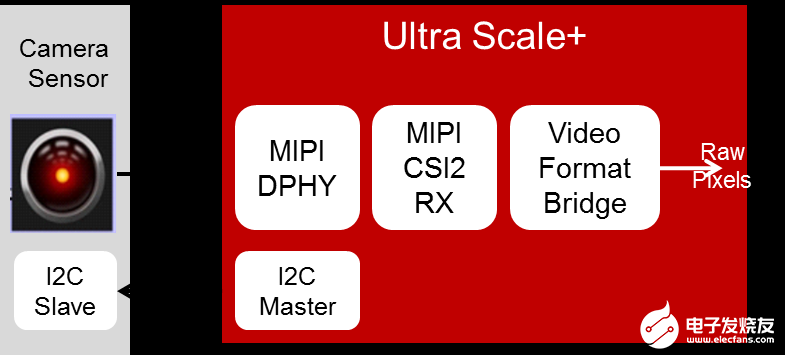

下面是MIPI CSI-2 RX Subsystem IP典型的应用示例:

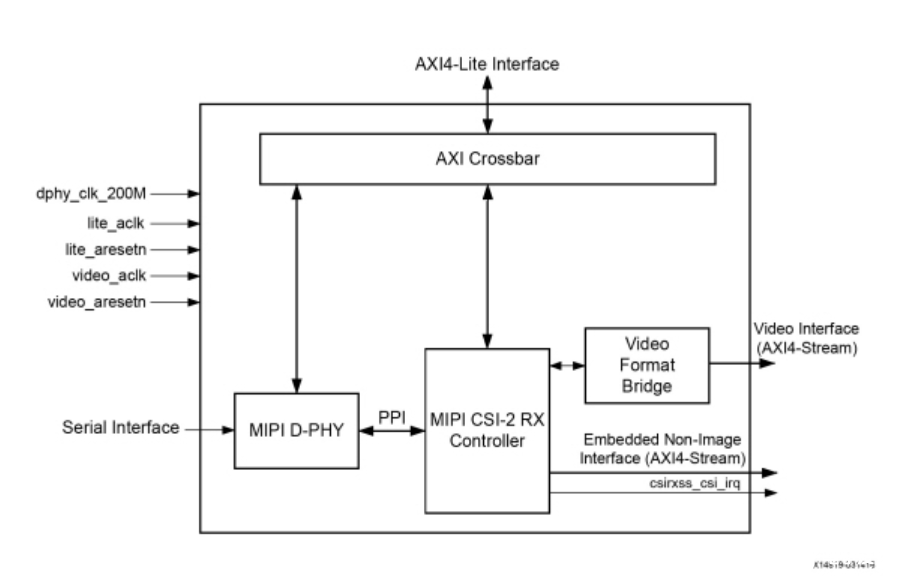

该IP是由MIPI D-PHY和MIPI CSI-2 controller, 以及VFB(Video format bridge)组成, 其中VFB可选. 下面是该IP的简略系统框图:

该IP支持7-series, UltraScale+, Zynq-7000, MPSoC, RFSoC, Versal. 对于UltraScale+, MPSoC, RFSoC, 在HP IO bank, 有可以支持MIPI_DPHY_DCI的I/O, 该I/O standard可以在同一个I/O上在low-power mode(0-1.2V single ended)和high speed mode(0.1-0.3v)之前切换。

对于Versal, 在其XPIO bank, 也有支持MIPI_DPHY_DCI I/O standard的I/O, 因此符合MIPI协议的sensor可以直接与FPGA的这些IO连接。

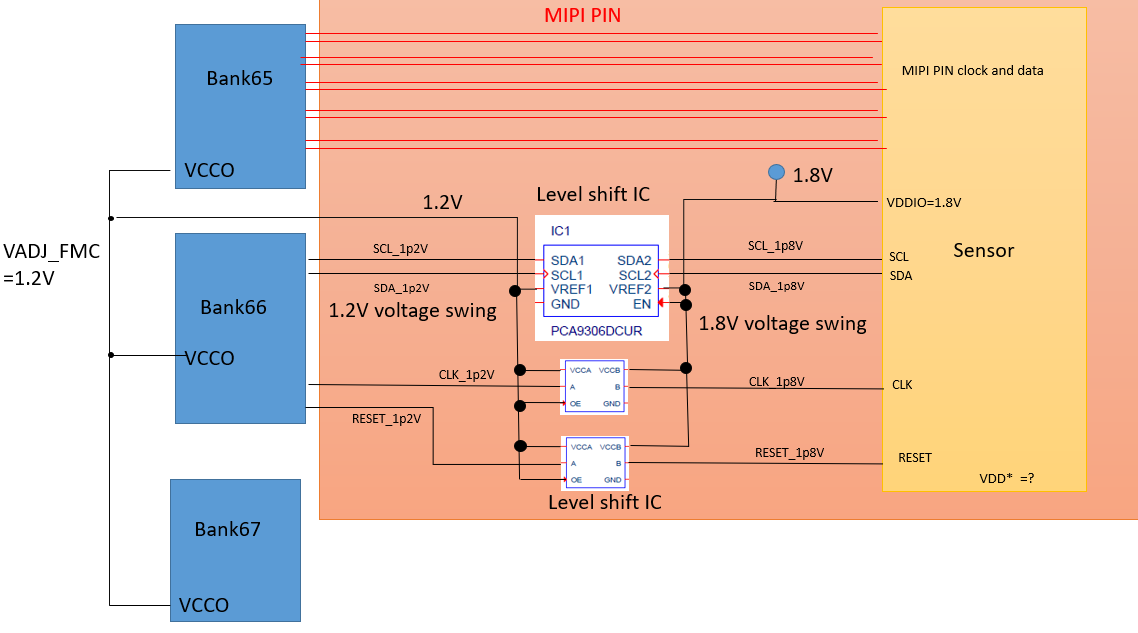

需要注意的是, 因为, MIPI_DPHY_DCI 无论对于input还是output, Vcco的要求都是1.2v, 见FPGA的手册, 如果sensor需要的电压是1.8v, 那么这时候, 对于那些控制信号, 因为有电压差异, 所以需要level shift。

下面是一个例子, sensor需要的VDDIO是1.8v(见sensor的手册), FPGA与sensor连接的简略框图, 左边是FPGA I/O bank, 右边是Sensor.x

对于7 series和zynq-7000的支持, 因为FPGA没有支持MIPI协议的I/O, 因此, 需要用到XAPP894实现PHY, 当然, 如果用户直接用MIPI CSI-2 RX Subsystem该IP, 因为该IP支持 7 series, 不需要考虑PHY实现。

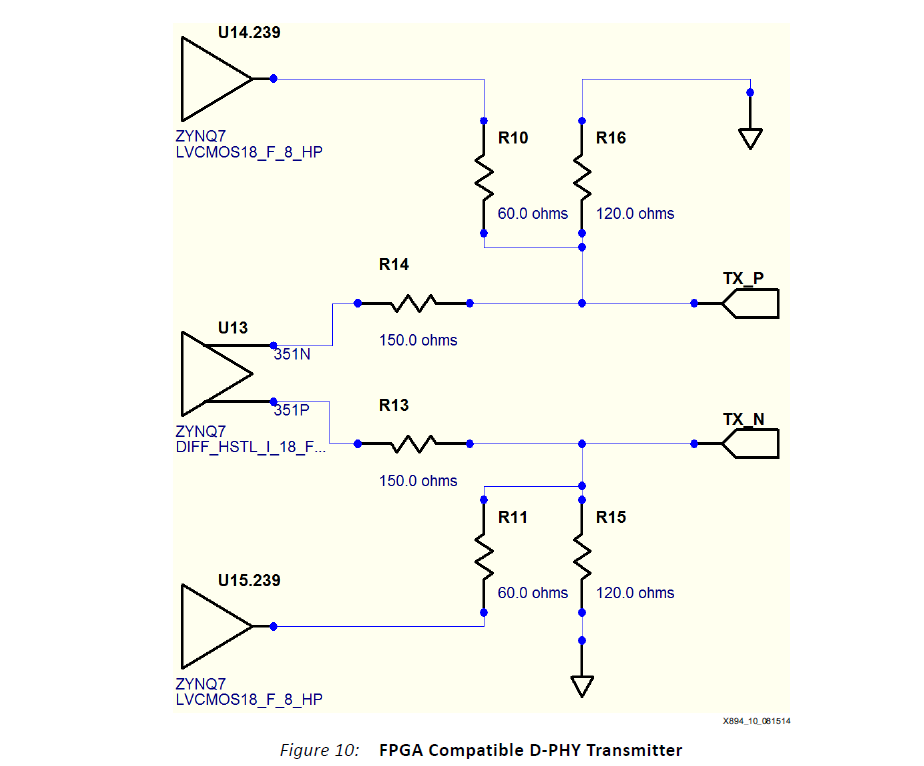

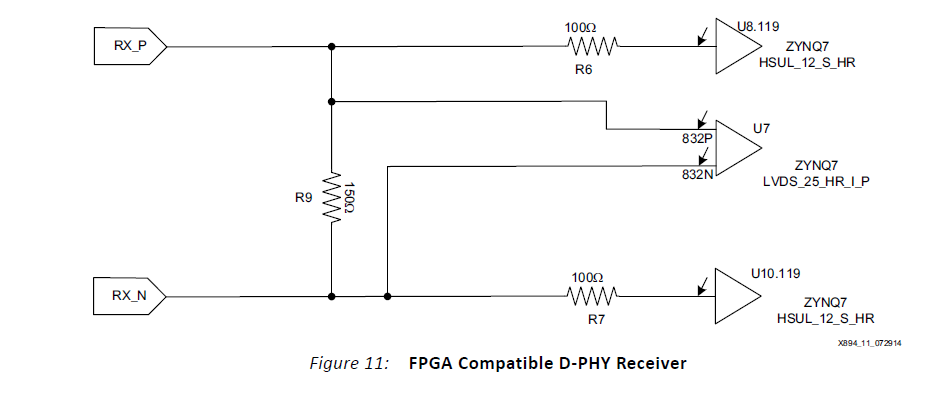

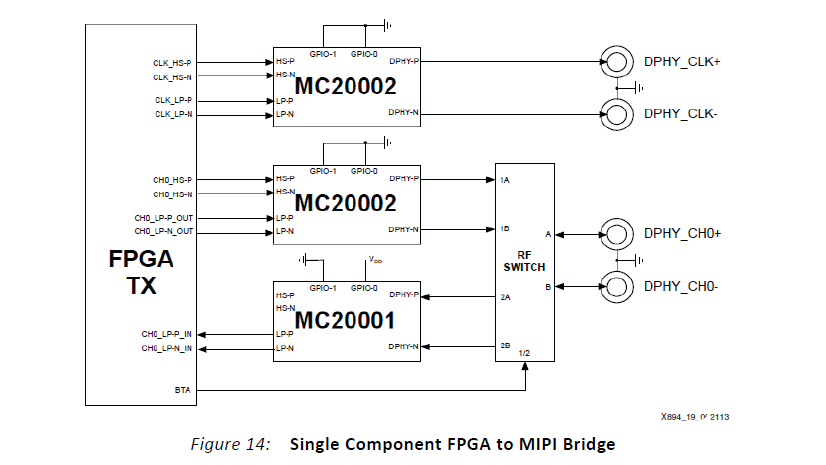

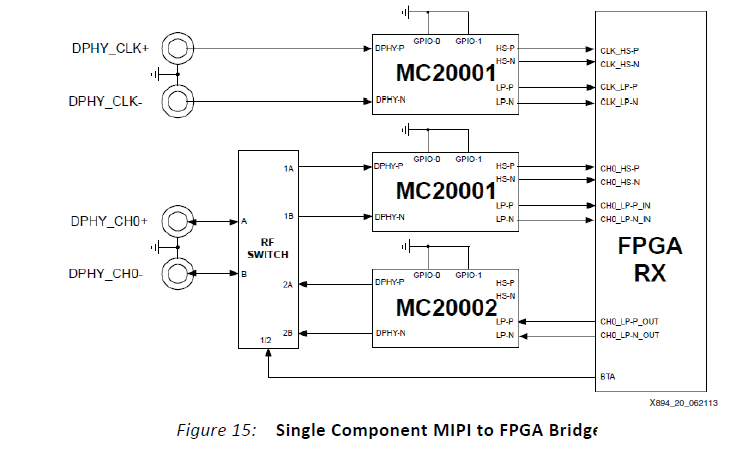

如果目标器件是Spartan, 该IP不支持. 那么用户需要用到XAPP894实现PHY, XAPP894提供的两种方式实现DPHY IO, Compatible Solution和Compliant Solution.

Compatible Solution:

Compliant Solution:

Compatible solution适用于不超过800Mbps的应用, 不管是哪种实现方式, 需要做board level SI simulation。

对于7series以及其他MIPI CSI-2 RX Subsystem支持的这些器件. 需要注意I/O pin以及bank的要求。

审核编辑:汤梓红

-

camera module CSI-2 MIPI解压这块没有2014-06-17 0

-

CX3 3065: HOW TO CFG MIPI CSI-22018-08-30 0

-

mipi-csi2-rx示例设计许可证错误2018-12-28 0

-

请问是否有MIPI CSI-2解决方案可了解FPGA?2019-07-18 0

-

移动行业处理器接口MIPI CSI-2接收桥参考设计2020-04-29 0

-

基于MIPI的移动行业处理器接口CSI-2发送桥2020-05-01 0

-

mipi csi与mipi csi phy部件之间如何连接?2022-03-10 0

-

具有MIPI CSI-2输出的汽车ADAS参考设计2022-09-14 0

-

如何连接STM32MP1系列产品与MIPI CSI-2摄像头的信息2023-09-07 0

-

MIPI CSI-2 D-HPY协议详细资料介绍免费下载2018-08-01 1580

-

基于MIPI CSI-2 Receive Bridge图像传感器的参考设计2021-01-14 866

-

HDMI_1.4_2.0_RX_Subsystem_IP介绍和基础debug建议2022-03-25 3270

-

MIPI CSI-2 相机规格增加了先进的始终在线成像解决方案2022-08-19 1018

-

Gowin MIPI D PHY RX TXAdvance IP用户指南2022-09-15 335

-

MIPI CSI-2 RX Subsystem IP和D-PHY基本调试2023-03-17 1087

全部0条评论

快来发表一下你的评论吧 !