单片微波集成电路中砷化镓的干蚀刻

电子说

描述

引言

目前高功率砷化镓基单片微波集成电路(MMICs)已广泛应用于军事、无线和空间通信系统。使用连接晶片正面和背面的衬底通孔,这些MMICs的性能显著提高。

在蚀刻通孔之前,在晶片的正面制造器件,然后根据需要将晶片从背面减薄到100-200μm的厚度。从晶片的背面执行通孔蚀刻,以接触正面上的接地金属焊盘。干法蚀刻优于湿法蚀刻,因为它具有优异的均匀性和尺寸控制。

由于通孔蚀刻在所有其他器件制造工艺之后进行,因此工艺的可靠性和再现性非常重要。为了蚀刻非常高纵横比的孔,干法蚀刻工艺必须提供高蚀刻速率、良好的蚀刻各向异性、平滑的侧壁以及对掩模材料和正面金属焊盘的高选择性。目前满足上述要求的最常见技术是反应离子蚀刻(RIE)。

实验与讨论

我们将晶片放置在施加了13.56 MHz射频功率的下电极上。使用冷却器将该电极的温度保持在30℃。在将工艺气体(CCl2F2和CCl4)引入腔室之前,通过由机械泵支持的涡轮分子泵将腔室抽空至约8E-6托的基础压力。由于四氯化碳在室温下是液体,所以使用鼓泡器中的N2气体将其蒸汽输送到室内。我们在砷化镓中蚀刻孔之后,分别通过在丙酮中清洗和在FeCl3 /H2O溶液中湿法蚀刻来去除光致抗蚀剂和Ni掩模。

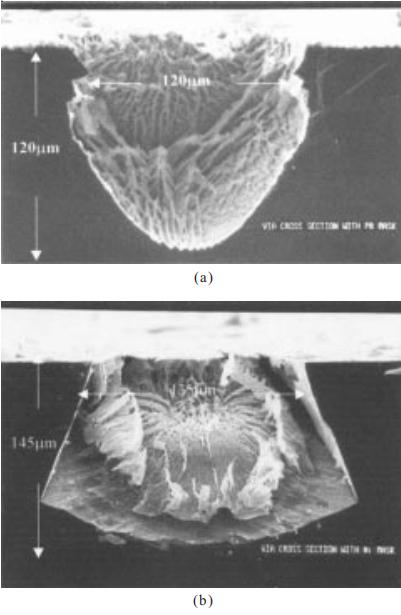

图1显示了在功率=150W、压力=100mTorr、CCl4 =7sccm、CCl2F2=35sccm的相同条件下,对于60μm直径的开口,分别使用光致抗蚀剂和Ni掩模获得蚀刻轮廓。这些蚀刻曲线表明,在更高的压力下(100毫托),使用光刻胶掩模时蚀刻本质上是各向异性的,而使用Ni掩模时是结晶的。

图1:横截面扫描电镜图

为了获得大于116μm的蚀刻深度和期望的轮廓,因此英思特在大约40-50毫托的较低压力下研究了Ni掩模。在较低压力下,平均自由程增加,这增强了物理蚀刻分量,因此增强了各向异性。实验表明,在没有任何掩模的情况下,砷化镓平均蚀刻速率约为3-4 m/min。

然而,在Ni掩模的情况下,蚀刻速率有非常小的降低,从60分钟的2.1米/分钟降低到120分钟的1.9毫米/分钟。在这两种情况下,蚀刻速率随着深度的增加而降低,这是因为提供活性物质和去除蚀刻副产物的效率降低。与Ni掩模相比,用光致抗蚀剂掩模观察到较少的底切。

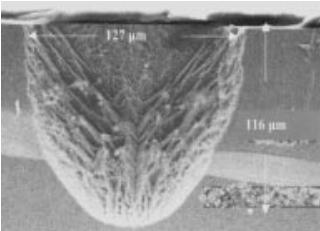

如图2所示,在100毫托工艺压力下蚀刻时间为120分钟。该蚀刻轮廓清楚地表明,使用光致抗蚀剂掩模的RIE工艺仅适用于蚀刻100μm深的通孔。

图2:经过120 min的蚀刻后,用光刻胶掩模获得的扫描电镜轮廓

从上面的讨论可以清楚地看出,Ni掩模适用于使用RIE工艺的200μm深的通孔蚀刻,这导致非常好的选择性、再现性和可重复性。

结论

英思特研究了各种工艺参数对采用四氯化碳气体的RIE深度各向异性刻蚀砷化镓的影响。发现镍金属掩模适合于实现200μm的蚀刻深度,平均蚀刻速率约为1.3 m/min,并且具有期望的各向异性轮廓。

英思特研究表明在40毫托压力、950瓦线圈功率、90瓦压板功率、约4毫米/分钟的蚀刻速率和通孔蚀刻产率下整个晶圆的90%以上,具有非常好的均匀性和再现性。与RIE工艺相比,ICP工艺产生了具有可接受的蚀刻侧壁形态的高蚀刻速率。这种高密度等离子体蚀刻工艺已经集成到生产线中,用于以高产量制造MMIC,而不影响使用现有设计和掩模组的生产。

审核编辑:汤梓红

-

MESFET集成电路应用-概述2009-08-20 0

-

微波集成电路设计2009-08-24 0

-

单片微波集成电路设计分析介绍2019-07-04 0

-

黑科技!看大神如何使用AI设计微波集成电路2019-08-16 0

-

什么是微波集成电路技术?2019-09-11 0

-

怎么设计制作一种基于GaAs工艺的可变增益功率放大器单片微波集成电路?2021-04-06 0

-

微波集成电路(MMIC)是什么意思2010-03-05 10976

-

MESFET集成电路应用2011-10-28 641

-

用于毫米波范围的单片微波集成电路2011-12-29 1076

-

微波集成电路设计作者: 顾其诤 项家桢 彭孝康2013-09-12 2502

-

中国集成电路大全-微波集成电路2017-03-01 1474

-

微波元器件和微波集成电路的学习课件免费下载2018-10-31 969

-

单片微波集成电路(MMIC)混频器——HMC8192LG2023-05-23 557

全部0条评论

快来发表一下你的评论吧 !