详解编码器和解码器电路

电子说

描述

编码器和解码器是组合逻辑电路,在其中,主要借助布尔代数实现组合逻辑。今天就大家了解一下编码器和解码器电路,分别从定义,工作原理,应用,真值表几个方面讲述一下。

编码器定义

编码器是一种转换二进制的数字组合电路,最多 2n 个输入行的信息到 n 个输出行。对应的输入二进制值生成输出线。

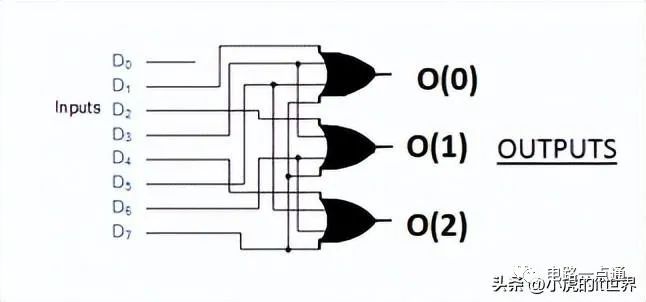

编码器电路

编码电路图

八进制到二进制编码器

它具有每个八进制数字的输入,总数为2。它具有三条输出线(根据XNUMXn输入线编码器将具有n条输出线的规则)。输出以二进制表示数字。

编码器可以使用“或”门实现。如果八进制数字的值为1、1、3、5,则输出C等于7。如果八进制数字的值为2、3、6、7,则输出B将为4。如果八进制数字的值为5,则输出AS将为6。输入八进制数字的值为7、XNUMX、XNUMX、XNUMX。以下布尔表达式表示输出。

A = O4 + O.5 + O.6 + O.7

B = O2 + O.3 + O.4 + O.7

C = O1 + O.3 + O.6 + O.7

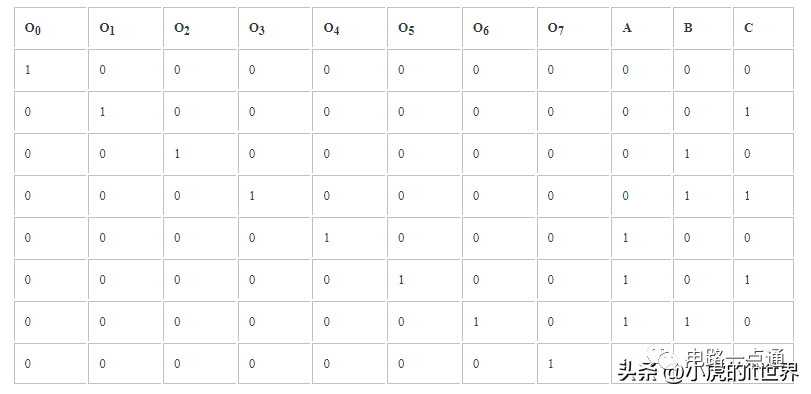

八进制到二进制编码器真值表

在桌子上实现的编码器有唯一的限制。也就是说,在任何给定时间,只有一个输入可以处于活动模式。这就是为什么如果两个输入被激活,那么输出线会产生未定义的输出。

让我们举个例子,如果输入 O3 处于活动状态并且输入 O6 也处于活动状态,则编码器产生输出为 111。结果既不代表 O6 也不代表 O3。所以,有一个混乱。

为了解决这个问题,新的编码器被设计为具有输入优先级,以确保一次仅启用一个输入。如果在此新系统中将较高的数字的优先级设置为高,则对于启用的O3和O6,输出将为110,表示二进制数6。这是因为O6的优先级高于O3。

解码器定义

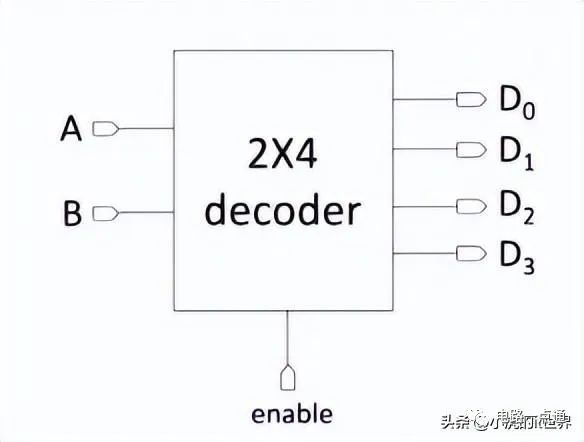

解码器是执行编码器电路相反操作的组合电路。它将来自n条输入线的编码信息解码或简化为最多2n条输出线。

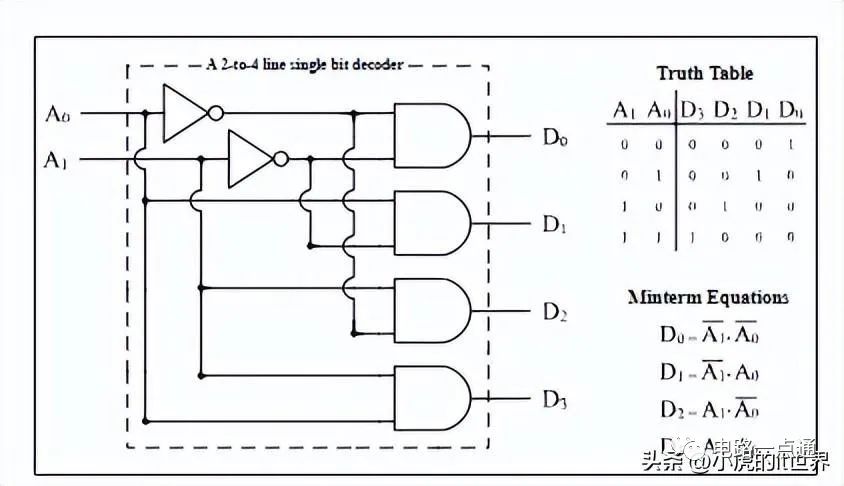

解码器电路

解码器电路图

二进制代码代表不同数量的信息。n位二进制代码最多可以表示2n个编码数据的不同元素。解码器对该信息进行解码并提供输出。唯样商城自建高效智能仓储,拥有自营库存超100,000种,提供一站式正品现货采购、个性化解决方案、选型替代等多元 化服务。

解码器被指定为输入到输出线解码器的数量。如果输入线数为n,则最大输出为2n。每个输入组合都会产生不同的输出值。

为了说明解码器的工作原理,让我们以3:8解码器为例。该规范建议该电路将三个输入线解码为八个输出,每个输出代表最小项。必要时,连接的“非”门会使输入数据线反相。AND门(总数为XNUMX)产生最小项(每个为一个输出)。

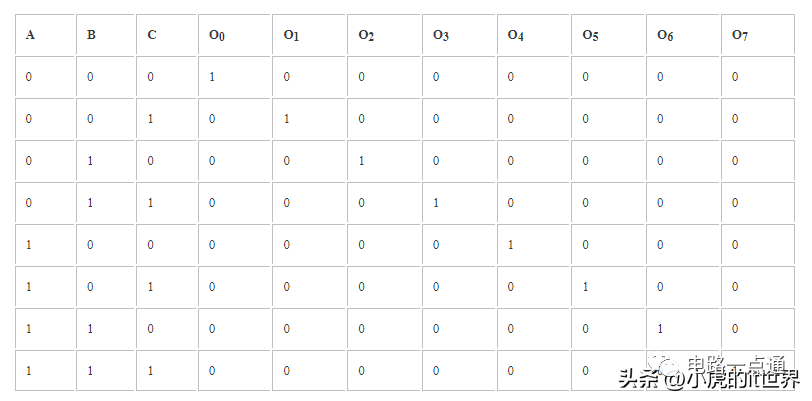

解码器真值表

从真值表中,我们可以看到七个输出值为0,一个输出值为1。结果值为1,表示实际输入值或最小项。

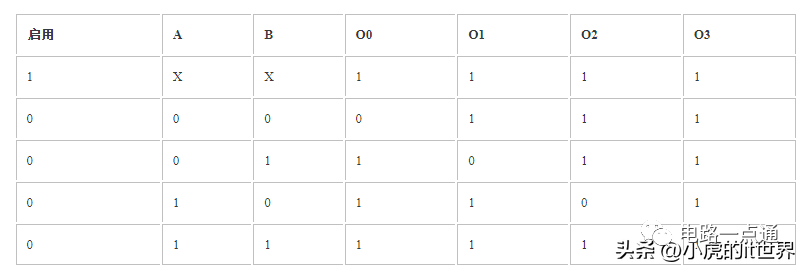

有一些由通用基本门(例如NAND和NOR)构成的解码器。使用“与非”门既经济又有效。解码器还需要启用编码器之类的输入。当使能输入引脚的值为0时,解码器将被使能。一次只能有一个输出的值为0,其余的输出将等于1。下面的真值表简化了操作。

解码器真值表

如果E值设置为1,则电路将被禁用。与编码器电路一样,如果E值设置为1,将不会检查其他输入。在解码器的禁用状态下,没有输出值为0,并且没有选择最小项。许多解码器具有多个使能引脚。他们需要遵守逻辑操作才能充当解码器。

如果在解码器上添加了使能输入,则可以使用解码器进行多路分解。并行对应的解码器可以构成大型解码器。

使用解码器实现逻辑

解码器具有2n条输入数据线和n条输出线。2n代表最小项,n代表形成最小项的变量数。如前所述,对于每种输入组合,都有不同的输出。

解码器可用于实现逻辑门,因为布尔函数不过是最小项之和。与解码器连接的“或”门可以实现布尔函数的逻辑。

启用解码器

编码器和解码器的应用

编码器电路和解码器电路已在智能数字设备中得到应用,因为它们对于当今的数字时代至关重要。其中一些重要的应用是

1、现代电动机的速度控制。

2、夜视摄像机

3、金属探测器

4、编码器电路在机器人车辆中的应用

5、自动化系统–尤其是家庭自动化系统。

6、自动监视系统具有不同类型的编码器电路。

7、编码器电路已用于加密通信系统中。

-

如何使用PSoC Creator中的块构建NRZI解码器和编码器2019-09-10 0

-

语音编码和解码免费Speex音频编解码器的微控制器2020-05-29 0

-

怎么理解真正的编码器和解码器?2020-09-01 0

-

编码器和解码器的区别是什么,编码器用软件还是硬件好2018-08-02 33723

-

Xilinx Logicore IP极轴编码器解码器产品指南资料免费下载2019-05-05 827

-

详解编码器和解码器电路:定义/工作原理/应用/真值表2022-11-03 5323

-

PyTorch教程10.6之编码器-解码器架构2023-06-05 266

-

PyTorch教程-10.6. 编码器-解码器架构2023-06-05 580

-

基于transformer的编码器-解码器模型的工作原理2023-06-11 1324

-

基于 Transformers 的编码器-解码器模型2023-06-16 513

-

神经编码器-解码器模型的历史2023-06-20 480

-

视频编码器与解码器的应用方案2023-08-14 903

-

YXC丨视频编码器与解码器的应用方案2023-08-23 413

-

LDPC编码器解码器产品简介(v2.0)2023-09-13 166

全部0条评论

快来发表一下你的评论吧 !