如何解决高速PCB设计中遇到的问题?pcb设计常见问题和改善措施

PCB设计

描述

PCB设计

如果像我一样,您有硬件背景,您可能更喜欢将数字电子产品视为开和关或高低;那些打开和关闭的信号在电路中瞬时可靠地传播。通过二进制形式,即时并且可靠。当然,从程序员的角度来看,这种抽象级别是在软件级别假设的!然而,随着时钟速度从MHz移动到GHz,使用越来越快的电子设备,事情并没有想象中那么简单。在本文中,我们将研究使高速设计更加复杂的一些因素,以及用于解决这些问题的一些技术。

电压转换速率

让我们从电压转换速率开始。我们需要明白,从“关闭”到“打开”的瞬时转换 - 电压必须从低电平(例如0V)过渡到高电平(例如3.3V),通过两者之间的所有电压,即使它这样做得非常快;在转换过程中的某个时间点它是1.8V,在另一个时间点是2.5V,依此类推。电压从低电平状态转换到高电平的速度称为电压转换速率。

速度

电信号也有速度限制——光速。光速为299 792 458 m/s,非常快。然而,考虑到 1GHz 信号的周期为 1ns(1 纳秒),光的传播速度仅为大约 0.3 m/ns,即 30 cm/ns ; 这意味着在30厘米长的导体上,1GHz信号的第一个时钟脉冲在导体开始时产生下一个时钟脉冲时刚刚到达导体的另一端。如果是3GHz,当第一个脉冲到达导体的另一端时,时钟信号源已经产生了第三个脉冲!思考一下(3GHz,30cm导体),这意味着我们的单个30cm导体在其长度内“包含”3个脉冲,3个高低状态。这当然不是从导体的一端到另一端的瞬时开/关!

信号传输不能再被认为是瞬时的了!

可靠性

每当电流通过导体时,它都会在该导体周围产生磁场 - 无论磁场多么小。相反,当磁场通过导体时,它会在该导体内产生电压(通过电动势)。因此,电路中的所有导体(通常是PCB上的轨道)都能够产生和接收电磁干扰,这可能会使轨道承载的信号失真。PCB上的每个轨道也可以被视为一个小型无线电天线,能够产生和接收无线电信号,这可能会使轨道承载的信号失真。

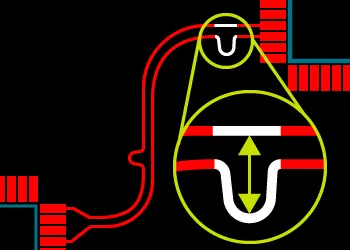

阻抗

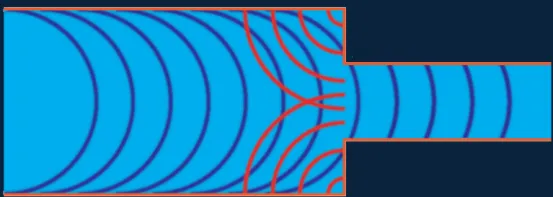

如“速度”部分所述,我们的电信号不是瞬时的,实际上是在我们的导体中以波的形式传播的。在我们的3GHz / 30cm迹线示例中,在任何给定时间,导体内都有3个波 - 波峰和波谷。波受到各种现象的影响,其中对我们来说最重要的是“反射”。让我们想象一下,我们的导体就像充满水的运河/渠道。波在通道的一端产生,并沿着通道(接近光速)到达另一端。想象一下,我们的通道有100厘米宽,但在某个时候它突然变窄到只有1厘米宽——当我们的波到达突然变窄的部分(基本上是一堵有小缝隙的墙)时,大部分波会从狭窄的部分(墙)反弹回来发射器。

由于宽度变化引起的波反射

如果运河/通道内有多个狭窄的部分,那么就会有多个反射反弹,干扰信号。信号的大部分能量也不会到达接收器(至少不会在正确的时间到达)。因此,通道的宽度/高度必须沿其长度尽可能保持恒定,以避免反射。

宽度的多次变化使信号变差

在电气术语中,这被称为 "阻抗",它是导体的电阻、电容和电感的一个函数。因此,对于高速设计来说,我们希望尽量保持轨道的阻抗在其长度上的一致性。另一件需要考虑的事情,特别是在总线拓扑结构中,我们希望在接收器处 "停止 "波,而不是让它再次反弹--这通常是通过一个终端电阻来实现的,它在总线的末端吸收波的能量(如RS485)。

信号完整性

所以现在我们知道所有这些物理效应是什么,当频率很高时,它们可以扰乱我们的信号。那么这样的数字通信是不可靠的,需要在设计电路时开始考虑摆动、速度、磁干扰和阻抗。在PCB设计过程中考虑信号完整性只是意味着考虑所有这些因素,并在电路板上布置对策,以确保我们的接收器获得正确的信息。以下是高速PCB设计中使用的几种更常用技术的简短介绍。

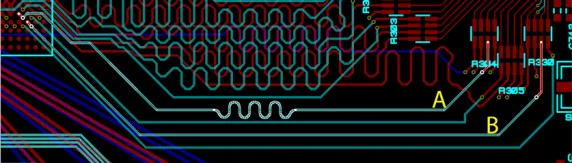

长度匹配轨道

当我们的通信信号使用多条线路时,例如“时钟”和“数据”——甚至可能是具有 8 条或更多数据线的并行总线——那么我们必须确保所有信号同时到达接收器。一旦我们了解电信号不会瞬时传播,那么我们就可以理解,如果多个信号在不同长度的轨道上传播,那么它们将在不同的时间到达接收器(即使它们是在同一时间传输的)。

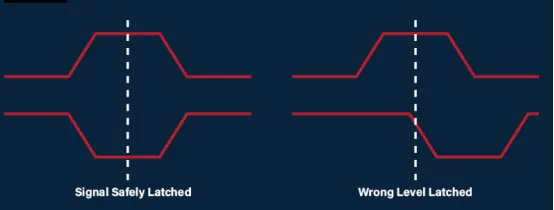

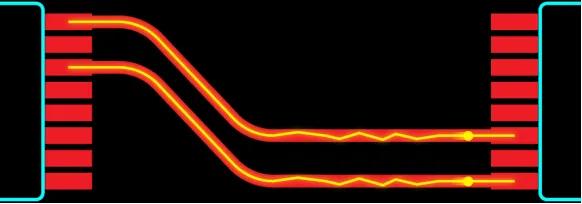

不均匀的磁道长度会导致接收器处的信号不正确

考虑具有 1 条时钟线 (C) 和 2 条数据线(A 和 B)的通信方案;如果数据线B的长度比数据线A的长度长得多,那么来自B线上时钟脉冲#1的信号可能会与来自A线上时钟脉冲#2的信号到达接收器的同时到达接收器,完全失真和破坏了通信。

轨道A和B的长度不同

另一种可视化的方法是想象跑步者在两条不同的赛道上。每个跑步者只能携带半条消息,并在终点线重新组装信息。如果跑步者以相同的速度行进,并且轨道长度相同,则它们各自同时到达目的地,接收者可以正确重新组装文档。但是,如果轨道长度不同,那么我们的跑步者不会同时到达,并且文档无法轻松重新组装。因此,多线通信信号中的轨道长度必须相同,这一点非常重要——这被称为“轨道长度匹配”或“网络调优”。

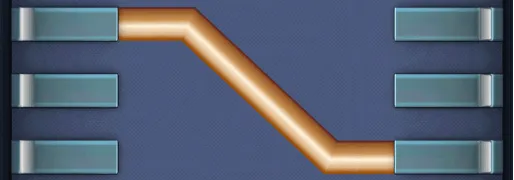

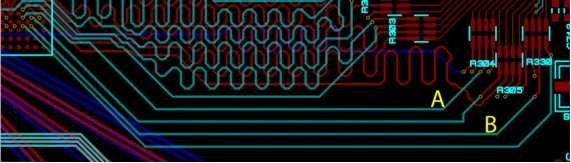

特意为轨道 A 添加长度,以便从源到接收器的距离与轨道 B 相同

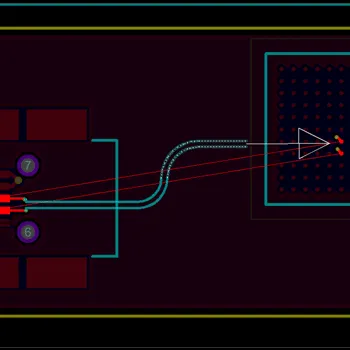

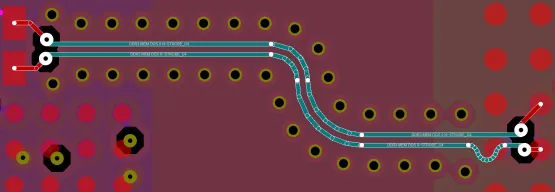

差分对

“差分对”是一种高度不受电磁干扰(因此是可靠的)的通信技术。也许最常见且易于识别的实现是USB。另一种实现差分对的技术是RS485。差分对在两个平行导体上使用“推挽”技术——一个“推”,另一个“拉”。如果一条线是“高”,那么另一条线必须是“低”的,反之亦然。差分对中的信号测量为任一导体上的电压之差。差分对彼此严格平行,并且彼此同相。除了轨道长度匹配之外,同相要求意味着,如果差分对绕过一个弯道(这将导致外轨道的路径比内轨道更长),那么内轨道必须尽快人为地为其轨道增加一点额外的长度,以便尽快使平行对的起点/终点的总距离再次均衡。

差分对可能遇到的任何干扰都应对两个轨道影响程度是一样的,因此它们之间的差异将保持恒定和可靠。然而,保持轨道同相很重要,这样如果电磁干扰在轨道的某一点出现,那么它将以相同的方式影响并行信号。如果信号异相,则信号一侧的峰值可能会受到影响,而信号另一侧的波谷会受到影响。

如果信号线同相,则干扰对两条信号线的影响相同

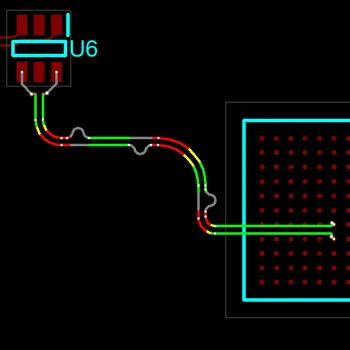

通孔缝合和屏蔽

顾名思义,通孔屏蔽是一种“屏蔽”轨道免受产生和接收电磁干扰的技术。“电源层”(也称为“接地层”或“铜浇注”)放置在多个PCB层上以围绕一个或多个轨道,然后使用过孔将这些电源层缝合在一起,在轨道周围产生“屏蔽”的效果。

通过屏蔽差分对轨道

较高的电压转换速率,即信号从 "高 "到 "低 "或反之亦然的速度,比低电压转换速率产生更多电磁噪声。电压转换速率本身通常在芯片数据手册中指定(有时可配置,例如某些微控制器),因此不由PCB设计阶段决定,但是在屏蔽方面可以更加关注具有已知高电压转换速率的信号。通孔缝合用于将两个电源层“拼接”在一起。其中一个原因是为信号提供一条短的“返回路径”,这对于阻抗匹配等非常重要。

总 结

高速设计使很多数字工程师一开始就有点脱离了他们的舒适区。对于数字信号来说,二进制、即时和可靠不再是必然的,因此我们需要积极采取措施来保护我们在PCB上的信号。希望这篇文章能为初学者解开一些问题的神秘面纱,并为未来的研究提供一些要点。同时,如果你正在寻找一种能够帮助你进行高速设计的CAD工具,那么为什么不仔细看看Proteus PCB设计工具呢!

本文章版权归英国LABCENTER公司所有,由广州风标电子提供翻译,原文链接如下:

https://www.labcenter.com/blog/pcb-highspeed-intro/

-

PCB设计常见问题2012-08-14 0

-

高速PCB设计常见问题2012-09-03 0

-

高速PCB设计之一 何为高速PCB设计2014-10-21 0

-

热门PCB设计技术方案2014-12-16 0

-

PCB设计中常见的问题2021-03-01 0

-

PCB设计常见问题有哪些2021-04-25 0

-

高速PCB设计的叠层问题2009-05-16 610

-

高速PCB设计误区与对策2011-11-23 561

-

高速PCB设计指南二2016-05-09 692

-

高速PCB设计电容的应用2017-01-28 929

-

高速PCB设计技巧有哪些2020-06-19 1585

-

PCB设计常见问题1-20例笔记2023-02-14 1548

-

pcb设计常见问题和改善措施2023-08-29 2079

-

pcb设计会遇到哪些常见的问题2023-09-11 697

全部0条评论

快来发表一下你的评论吧 !