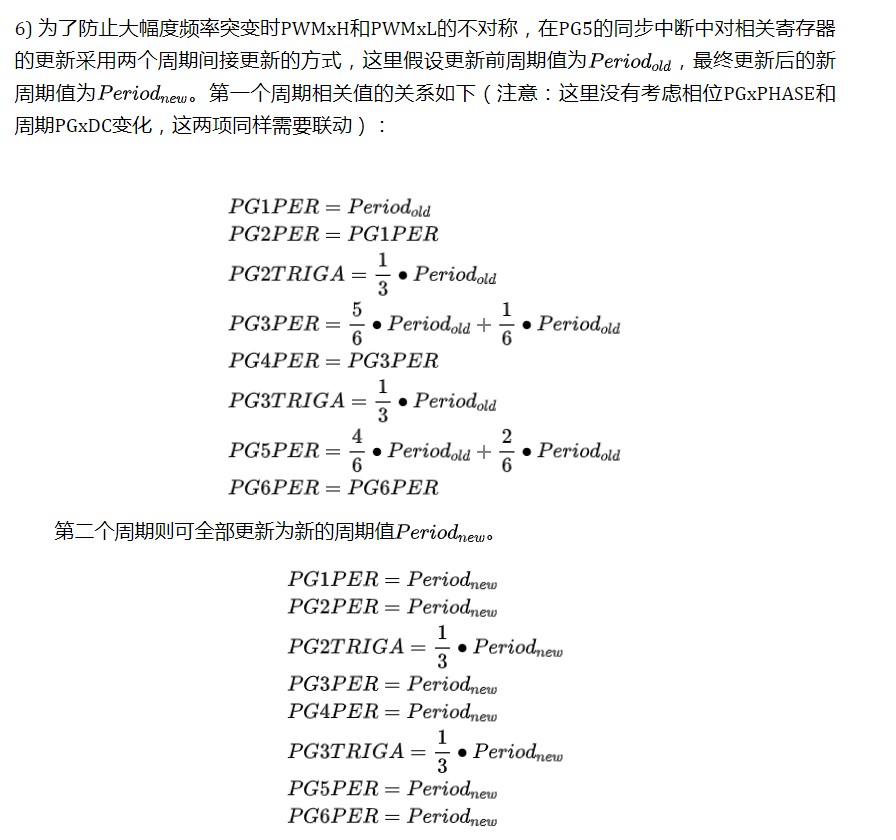

基于dsPIC33CK256MP508实现的三相交错LLC PWM发波逻辑

电子说

描述

本文介绍基于 dsPIC33CK256MP508 实现的三相交错 LLC PWM发波逻辑,该发波逻辑充分利用了 dsPIC33C 系列MCU强大的“支持精细边沿定位的高分辨率PWM”外设,诸如PWM发生器(PG)的ADC触发信号2分频,PCI同步功能和PWM事件输出机制。同时也开启了PG5的同步中断(此中断建议具有最高优先级)。

1. PWM发波逻辑说明

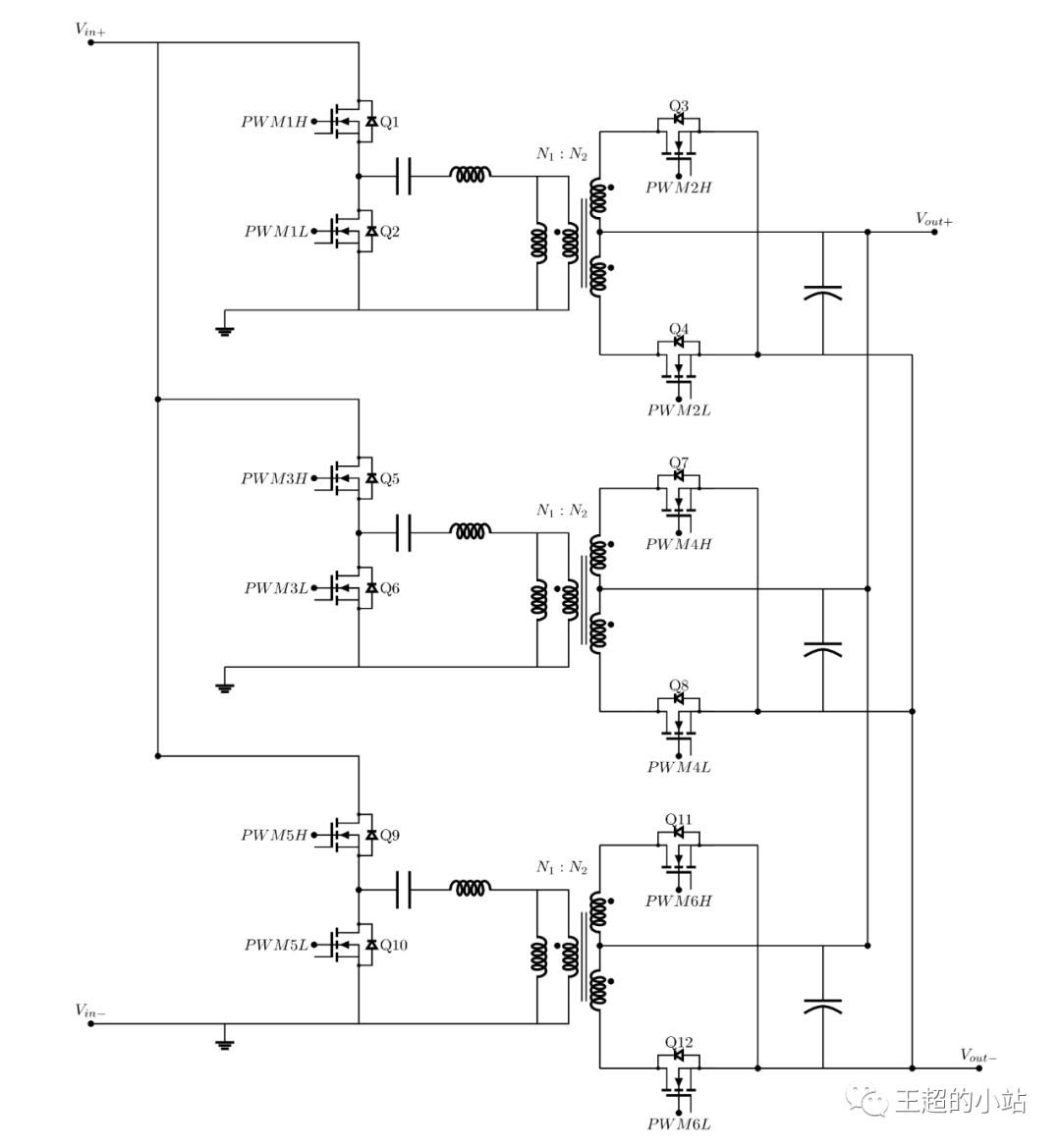

三相交错带同步整流的半桥LLC拓扑结构示意如下,需要6对PWM波。对于dsPIC33CK256MP508 可以用PG1、PG3和PG5作为主管PWM驱动,PG2、PG4和PG6作为同步管PWM驱动。

图 1 - 三相交错LLC拓扑示意

1.1 PWM外设基础知识回顾

在具体研究PWM发波逻辑之前,需要了解下本文用到的dsPIC33C 系列MCU“支持精细边沿定位的高分辨率PWM ^[2]^ ”外设的一些基础知识。

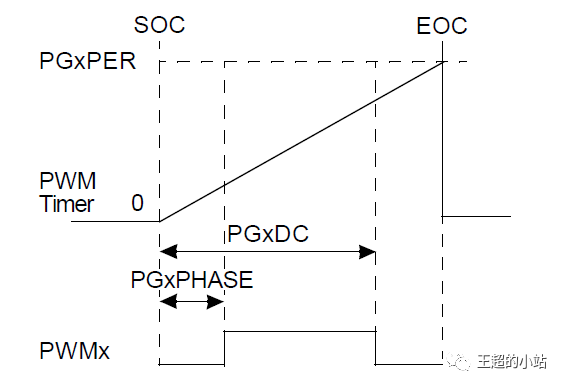

- PWM模式 - 独立边沿PWM模式

- PGxPHASE:确定定时器计数器周期开始后的PWM信号上升沿位置,一般主管PGxPHASE赋值为0,而对应于主管的同步整流管靠PGxPHASE值实现相应的相位偏移。

- PGxDC:确定定时器计数周期开始后的PWM信号下降沿位置。

- PGxPER:确定PWM定时器计数周期的结束位置。

图 2 - 独立边沿PWM模式

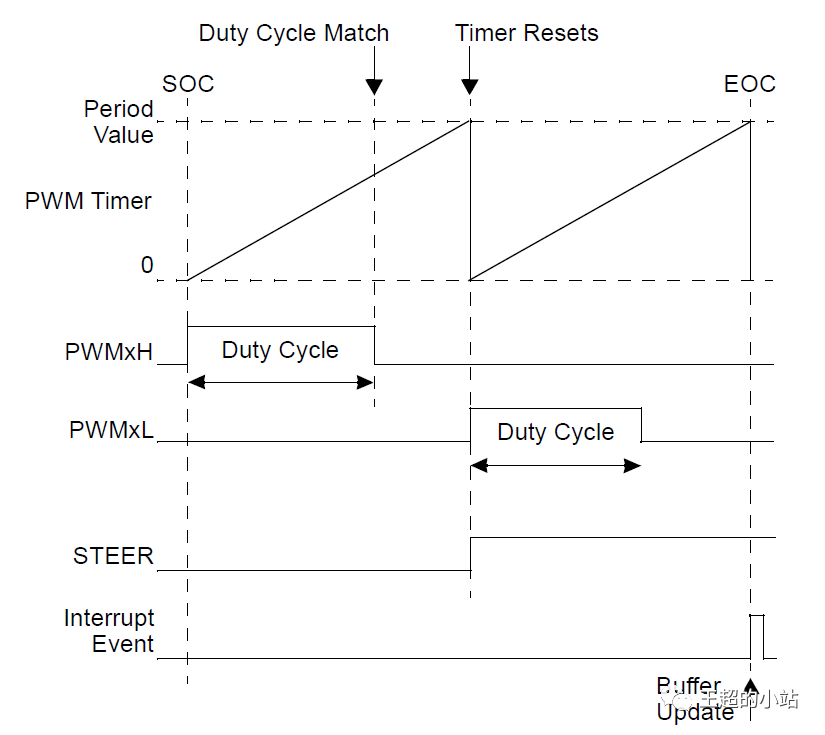

- 输出模式 - 推挽输出模式

推挽输出模式在接收到SOC触发信号时,都会将PWM周期重复两次。由于推挽模式下不能使用死区,所以在独立边沿PWM模式下可以给PGxDC一个小于PGxPER值,以实现死区功能。

图 3 - 推挽输出模式

- ADC触发信号

每个PWM发生器可生成两个ADC触发信号:ADC触发信号1和ADC触发信号2,同时ADC触发信号1输出可以使用ADTRPS<4:0>控制位(PGxEVTL<15:11>)进行后分频,以降低ADC转换的频率。

- PWM事件输出

PWM事件输出功能提供了一种用于将各种PWM信号和事件与其他外设和外部器件接口的机制。本文LLC PWM发波逻辑的错相就会用到将ADC触发信号1的2分频送给PWM事件输出,然后相关PWM发生器与该事件进行同步。

- 同步PCI

同步模块是唯一可启动周期开始的PCI模块,可用作SOCS<3:0>(PGxCONH<3:0>)多路开关的输入,这里用于相关PWM发生器与PWM事件的同步操作,完成错相功能。

- 触发模式

PWM发生器提供了两种触发模式,用于确定如何使用SOC触发信号,分别为单触发模式和可重触发模式,使用TRGMOD<1:0>(PGxCONH<7:6>)选择触发模式,因用了PCI同步功能,这里需要选择重触发模式,以防止SOC触发信号丢失。

- 数据缓冲

PGxPER、PGxPHASE、PGxDC和PGxTRIGA等寄存器都是有缓冲的,本文这里选择在下一个PWM周期开始时真正更新寄存器。只要在PG1新周期开始前完成对PG1~PG6的相关寄存器更新,就可以保证半桥LLC所有PG的正确同步。

1.2 PWM发波逻辑实现

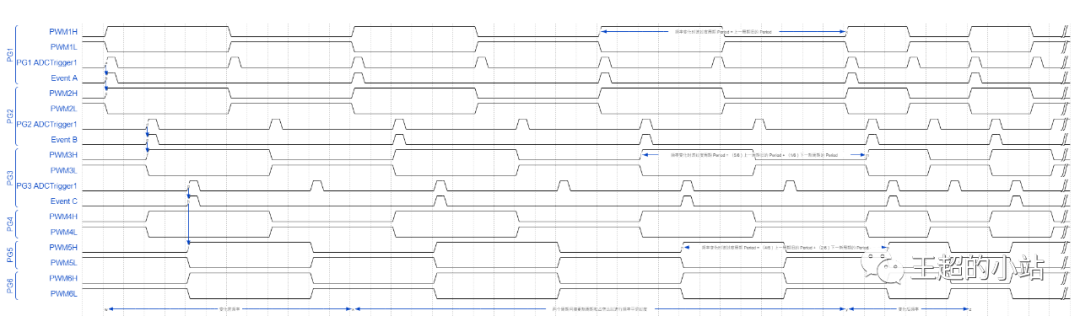

在回顾了PWM外设的基础知识后,开始看一下半桥LLC 三相交错PWM发波的具体实现,示意波形见图4 。这里忽略了死区和同步整流管相对于主管的相位偏移,其他详细说明如下。

图 4 - PWM发波逻辑波形示意

- PG1~PG6配置为独立边沿推挽输出模式。

- PG1采用SOC自触发模式,PG2采用PCI同步功能。PG1的ADC触发信号1经2分频送给PWM事件A(PG1的ADC触发信号1在定时器值等于PG1TRIGA时产生),PG2经PCI同步功能与PWM事件A同步,这就保证了PG1和PG2的相位同步一致。

- PG3和PG4采用SOC PCI同步功能,PG2的ADC触发信号1经2分频送给PWM事件B(PG2的ADC触发信号1在定时器值等于PG2TRIGA时产生),PG3和PG4经PCI同步功能与PWM事件B同步,这就保证了PG3和PG4与PG2的相位相差60°。

- PG5和PG6采用SOC PCI同步功能,PG3的ADC触发信号1经2分频送给PWM事件C(PG3的ADC触发信号1在定时器值等于PG3TRIGA时产生),PG5和PG6经PCI同步功能与PWM事件C同步,这就保证了PG5和PG6与PG3的相位相差60°。

- PG5开启PCI同步中断,此中断优先级需高于控制中断,在该中断中给PG1~PG6的相关寄存器赋值,保证在PG1的下一周期开始时刻所有寄存器统一更新。

2. 开发与验证

2.1 开发环境说明

2.1.1 软件开发环境

相关软件开发版本情况说明如下。

2.2 软件工程创建

您可以直接从如下Gitee链接下载完整的测试工程,参见doc目录下的README.pdf可以一步一步从零开始完成该搭建工程。

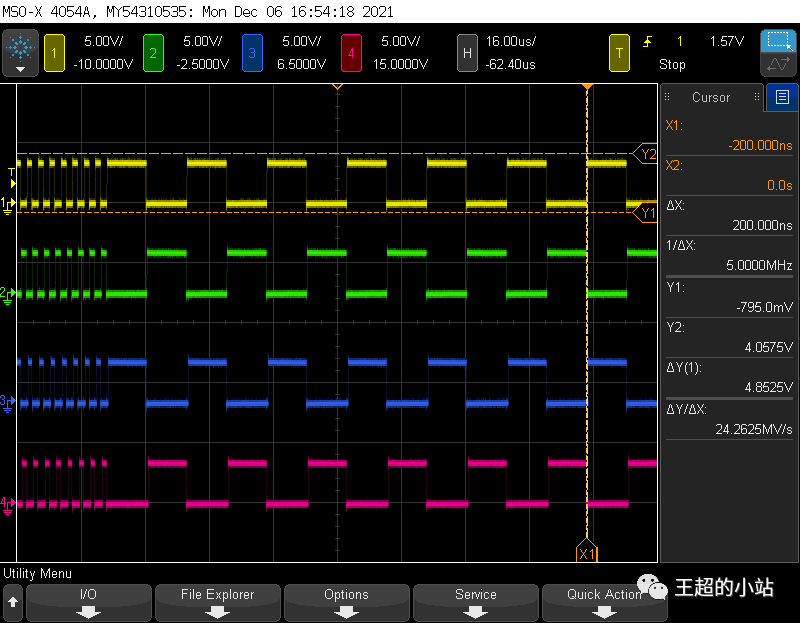

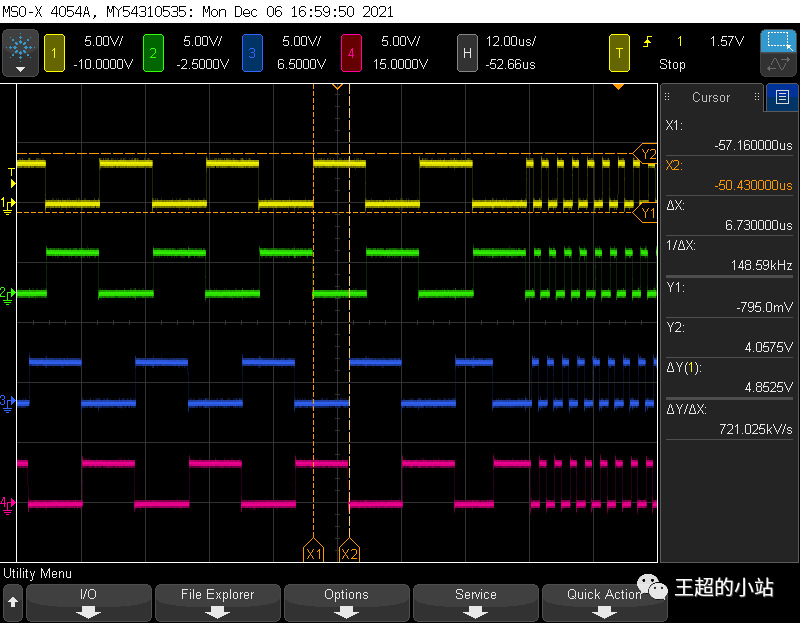

2.3 发波逻辑验证

软件经编译并烧录到dsPIC33CK256MP508后可以详细观察相关的PWM波形。PWM1H、PWM1L、PWM2H、PWM2L的波形关系如图6,在频率突变时也能很好的保证推挽输出正负半波的对称性。对应的PWM2H、PWM2L、PWM3H、PWM3L 和 PWM5H、PWM5L、PWM6H、PWM6L的波形关系也与图6一致。

图 6 - CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

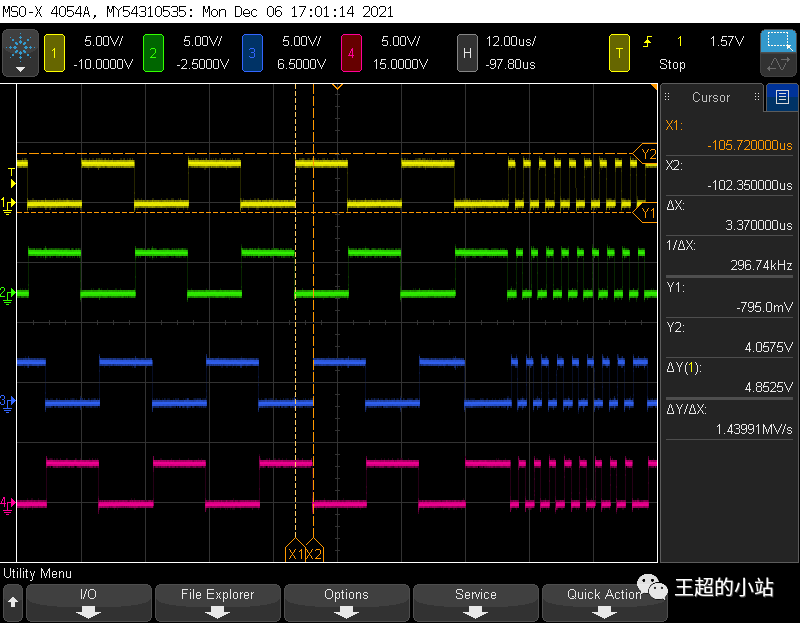

PWM1H、PWM1L、PWM3H、PWM3L的波形关系如图7,PG3滞后PG1 60°。

图 7 - CH1: PWM1H, CH2: PWM1L, CH3: PWM2H, CH4: PWM2L

PWM1H、PWM1L、PWM5H、PWM5L的波形关系如下,PG5滞后PG1 120°。

图 8 - CH1: PWM1H, CH2: PWM1L, CH3: PWM3H, CH4: PWM3L

-

Microchip dsPIC33CK256MP508-IPT 汽车 ISELED氛围灯方案介绍大大通 2022-10-19

-

单相交流电机和三相交流电机的驱动芯片?2013-05-26 0

-

使用C2000 MCU的数控式两相交错LLC谐振转换器设计2018-12-26 0

-

功能齐全的MCP3909RD-3PH3 MCP3909和dsPIC33F三相电能表2020-03-17 0

-

什么是三相交流电源对称?2021-07-12 0

-

三相交流电的产生与描述2021-09-10 0

-

基于FPGA实现三相SVPWM2021-09-13 0

-

Microchip全新dsPIC33CH512MP508双核DSC可为程序存储器2019-03-28 7454

-

dsPIC33CK256MP506数字电源接插模块(PIM)用户指南2021-04-29 1109

-

dsPIC33CH512MP508系列闪存编程规范2021-05-12 517

-

dsPIC33CH512MP508通用接插模块(PIM)信息手册2021-05-12 776

-

dsPIC33CK64MP105通用接插模块(PIM)信息手册2021-05-12 742

-

LLC峰值电流控制PWM发波的设计实现2023-07-22 1126

-

dsPIC33CH128MP508接插模块(PIM)信息手册2023-09-22 90

-

dsPIC33EPXXXGS70X/80X到dsPIC33CK256MP508的移植与性能增强指南2023-09-25 96

全部0条评论

快来发表一下你的评论吧 !