【科普】一文读懂以太网PHY芯片

【科普】一文读懂以太网PHY芯片

描述

摘要

物理层器件PHY(Physical Layer Interface Devices)是将各网元连接到物理介质上的关键部件。负责完成互连参考模型(OSI)第1层中的功能,即为链路层实体之间进行bit传输提供物理连接所需的机械、电气、光电转换和规程手段。其功能包括建立、维护和拆除物理电路,实现物理层比特bit流的透明传输等。通常物理层的功能均被集成在一个芯片之中,本文主要介绍了物理层的主要功能和主要接口以及以太网PHY芯片是如何实现这些功能的。

物理层(PHY)的结构

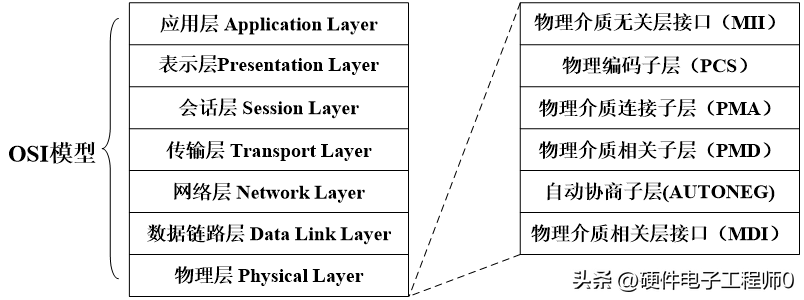

为了更好的阐述以太网物理层PHY芯片的主要功能,我们首先介绍一下物理层的结构。物理层是OSI的第一层,它虽然处于最底层,却是整个开放系统的基础。物理层为设备之间的数据通信提供传输媒体及互连设备,为数据传输提供可靠的环境。其功能:透明的传送比特流;如图1所示,物理层包括四个功能层和两个层接口,四个功能层为:物理编码子层、物理介质连接子层、物理介质相关子层和自动协商子层;两个层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连,以太网物理层PHY芯片实现的功能就是上面所提到的四层和两个接口的功能。

图1 物理层结构

以太网PHY芯片主要功能

以太网中PHY芯片的种类繁多,芯片支持的物理层规范标准也是多种多样,数据单板上使用PHY芯片是BROADCOM公司的BCM5248和MARVELL公司的88E1111,BCM5248支持的10Base-T、100Base-TX和100Base-FX规范标准,88E1111支持10Base-T、100Base-TX和1000Base-T规范标准。

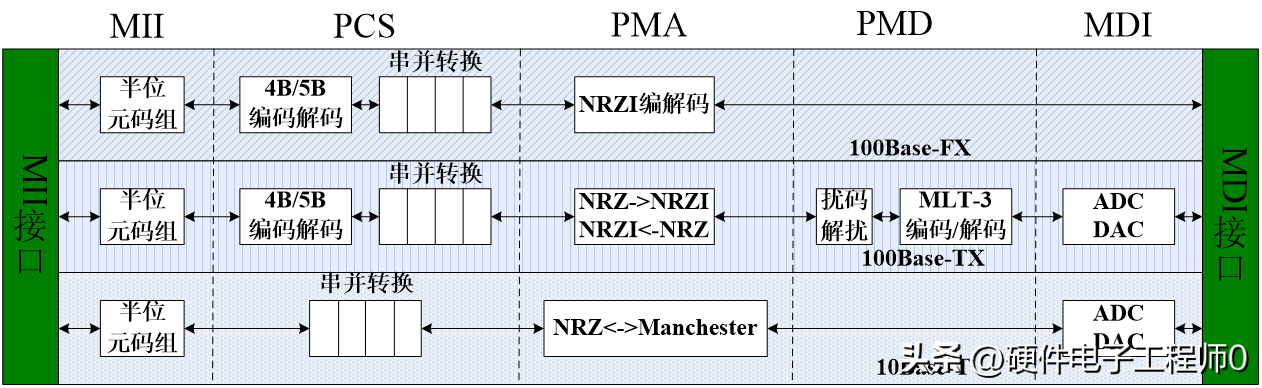

这里主要介绍了常用的10Base-T、100Base-TX和100Base-FX标准下PHY芯片主要完成的功能,如图2所示。在10Base-T的标准下,发送数据的过程为由MAC层的数据首先经过Manchester编码,然后经过串并转换,转换后的串行码流经过NRZ编码,最后经过DAC转换后送到5类双绞线上去进行传输,接受数据过程相反。

在100Base-TX的标准下,发送数据的过程为由MAC层的数据首先经过4B/5B编码,然后经过串并转换,转换后的串行码流经过NRZI编码,NRZI编码后的数据还需要经过扰码和MLT-3编码,最后经过DAC转换后送到5类双绞线或者更高的电缆上去进行传输,接受数据过程相反。在10Base-T的标准,发送数据的过程为由MAC层的数据首先经过串并转换,转换后的串行码流经过NRZ编码,再经过Manchester编码,最后经过DAC转换后送到5类双绞线上去进行传输,接受数据过程相反。在100Base-FX的标准下,发送数据的过程为由MAC层的数据首先经过4B/5B编码,然后经过串并转换,转换后的串行码流经过NRZI编码,直接送到光纤上进行传输,接受数据过程相反。下面将详细讲述各个子层和接口的功能。

图2 在10Base-T/100Base-TX/100Base-FX标准下PHY芯片主要完成的功能

物理介质无关层接口(MII)

MII满足ISO/IEC8802-3和IEEE802.3标准的要求,支持以太网数据传输速率为10Mbit/s、100Mbit/s、1000Mbit/s或10Gbit/s。MII接口主要由与链路层之间的端口(MAC-PHY)和与站管理实体(STA: Station Management Entity)之间的端口(STA-PHY)两部分组成。

3.1 MAC-PHY端口

这是MAC与PHY器件之间的接口,包括同步收发接口和介质状态控制接口。在介质状态控制接口中有载波读出信号(CRS: Carrier Sense Signal)和碰撞检测信号(COL: Collision Detection Signal)等。

3.2 STA-PHY端口

STA-PHY作为MII接口的一部分,用于在STA和PHY器件之间交换有关控制、状态和配置方面的信息。为此,ISO/IEC、IEEE规范了这个双线串行管理接口的相关协议及管理信息帧的结构和管理寄存器的标准。

(1) 管理寄存器

按标准,管理寄存器集(Management Register set)包括强制性“基本控制”寄存器(Mandatory “Basic Control” Registers)、状态寄存器(Status Registers)和专用扩展寄存器ICS(Specific Extended Registers)几部分。

(2) 管理信号帧结构

管理接口是一个双向串行接口,用于交换PHY与STA之间的配置、控制和状态数据,利用定义的寄存器集来实现PHY和STA的数据交换。STA可以启动所有的处理功能。ISO/IEC、IEEE对串行管理数据流定义了相关管理帧结构和协议。

3.3 常用PHY芯片的MII接口

常用PHY芯片的物理介质无关层接口包括:媒质无关接口(MII: Medium Independent Interface)、简化媒质无关接口(RMII: Reduced Media Independent Interface)、串行媒质无关接口(SMII: Serial Media Independent Interface)、源同步串行媒质无关接口(SS-SMII: Source Synchronous-Serial Media Independent Interface)、千兆媒质无关接口(GMII: Gigabit Media Independent Interface)、简化千兆媒质无关接口(RGMII: Reduced Gigabit Media Independent Interface)和串行千兆媒质无关接口(SGMII: Serial Gigabit Media Independent Interface)。具体每种接口的信号定义和数据发送时序在此就不多讲,实际工作过程中遇到某种接口查阅相关文档即可。

物理编码子层(PCS)

物理编码子层PCS有两个对外接口,一是与MII的接口,二是与物理介质连接子层(PMA: Physical Medium Attachment Sublayer)的接口。PCS子层遵循ISO/IEC8802.3和IEEE802.3标准,物理编码子层的主要功能包括对信号的编码译码、收发处理、管理和控制等。这里可用100Base-TX速率来讨论PCS子层要完成的功能。

4.1 PCS在100Mbit/s与10Mbit/s 下的工作模式

一般称10Base-T为以太网,100Base-TX为快速以太网,两者信号的速率,执行的协议以及采用的传输介质均有所不同。PCS子层对于100Base-TX信号进行4B/5B编译码、扰码(Scrambled)和MLT-3编码,将信号交换为62.5MHz的三元数据,然后通过隔离变压器送入5类双绞线电缆或者比5类双绞线电缆更好地电缆线路中传输。对于10Base-T信号则需进行曼切斯特(Manchester)编译码和相关的处理。对100Base-TX信号和10Base-T信号处理的功能比较如表1所示。

表1 100Base-TX和10Base-T信号处理功能的比较

| 信号 | 名称 | 速率 | 协议 | 传输介质 | 信号主要处理过程 |

| 10Base-T | 以太网信号 | 10 | IEEE 802.3 | 3类UTP、STP | Manchester编码 |

| 100Base-TX | 快速以太网信号 | 62.5 | IEEE 802.3u | 5类UTP、STP | 4B/5B->扰码->MLT-3 |

4.2 PCS发送子层

这里讨论10Mbit/s和100Mbit/s两种情况。PCS发送子层的功能是编码、碰撞检测与并/串变换等。

4.2.1 100Mbit/s PCS发送子层

PCS发送10Base-TX的数据需要进行4B/5B编码,即是将4bit数据组成的奈培(nib)变换成由5bit数据组成的码字。4B/5B编码的目的就是将数据包的起始符、帧结束、空载与控制功能等符号都编成码组进行传输。将4B码的nib映射入5B码字的过程是按IEEE 802.3标准规范进行的。

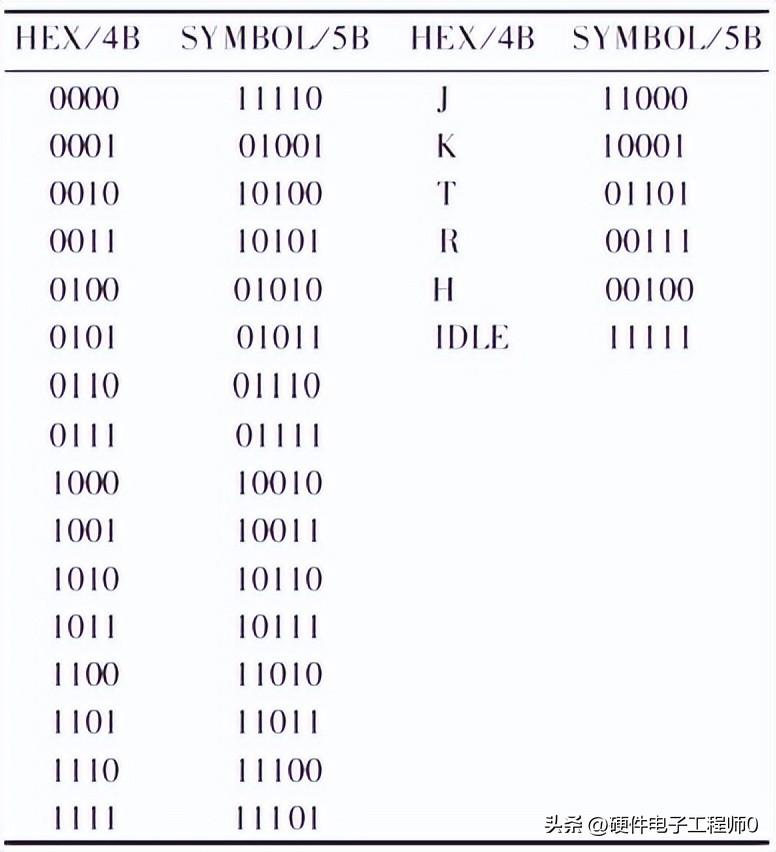

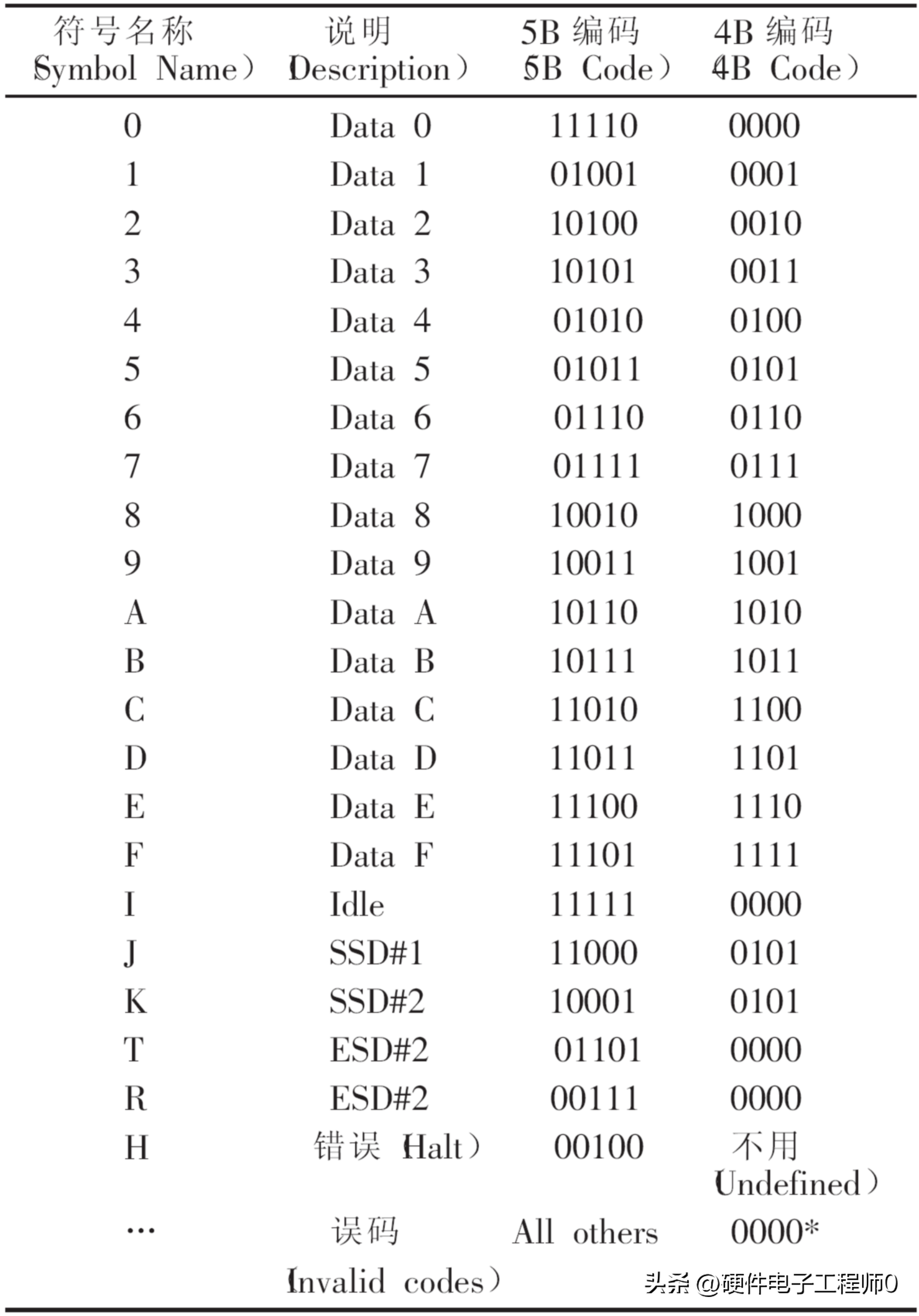

每个MAC/Repeater帧的前16nib(16×4=64bit)表示帧前序(Frame Preamble)。PCS将前二个奈培用数据流起始标帜符/J/K/代替,并在帧结束时加入数据流结束标帜符/T/R/,用于表示包的结束(ESD: End-of-Stream Delimiter)。4B/5B编码器同样在包之间填充间隔空信号(Idle Period)。用间隔空(Idle)符号实现数据流的连续性。表2即是4B/5B编码表,编码后的符号送入后面的扰码器。

表2 4B/5B编码表

PCS发送的子层4B/5B编码,有32种5bit的编码组合,其中16种5bit组合用于表示原16捉nib(4bit)的组合;另16种5bit组合,IEEE标准定义了6种用于控制使用的组合,还有10种认为非法的组合。IEEE定义的6种控制码组是:

1. /H/表示一个发送差错;

2. /I/表示一个IDLE空载;

3. 两个码组表示数据流起始标识符(SSD);

4. /J/和/K/;

5. 两个码组表示数据流结束标帜符(ESD);

6. /T/和/R/;

4.2.2 10Mbit/s的PCS发送子层

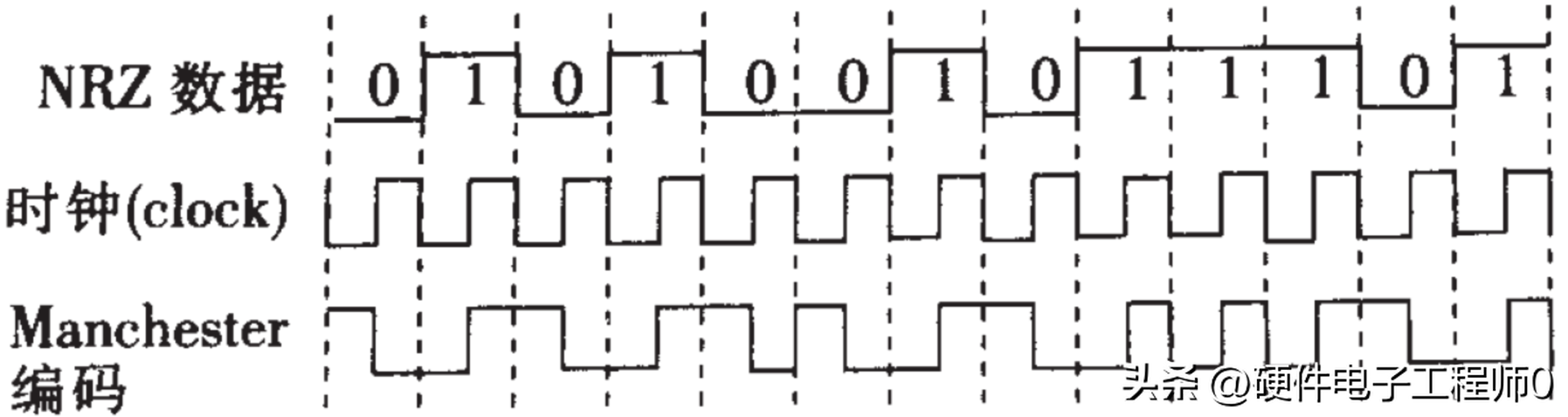

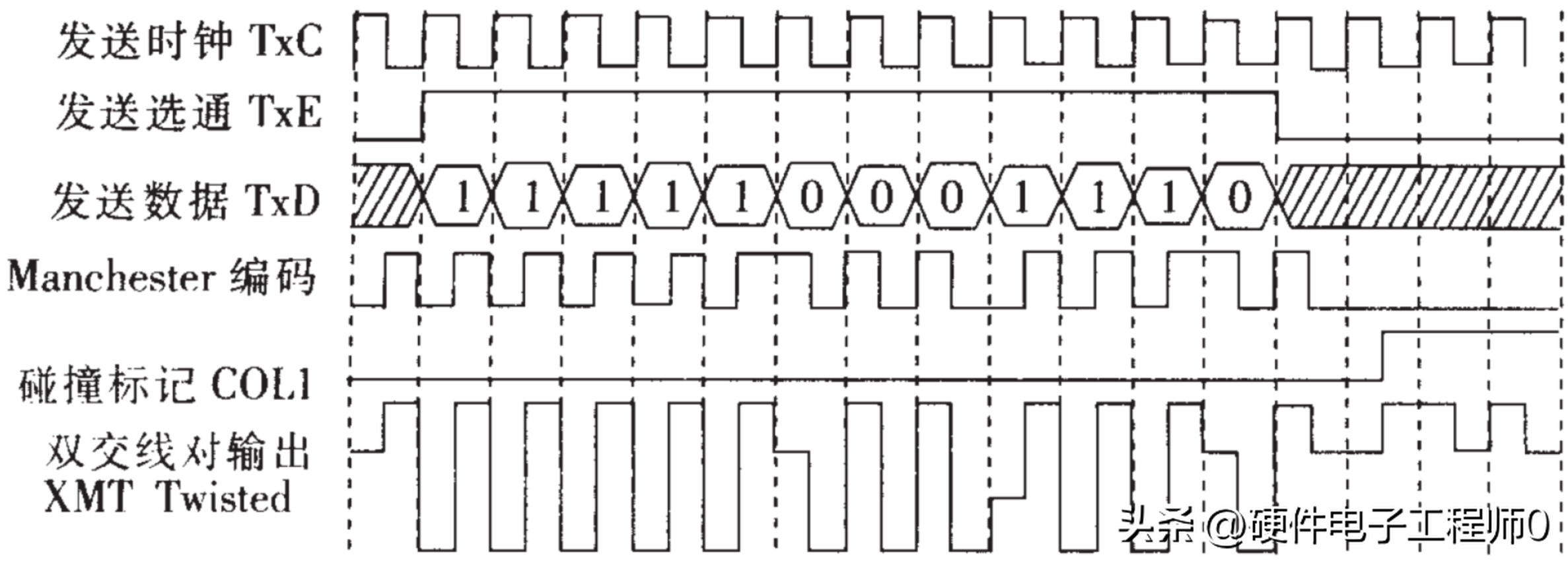

按ISO/IEC、IEEE标准的要求,10Mbit/s的PCS发送子层采用Manchester编码,即利用数据与时钟相“异或”,使数据每bit的前一半CLK取数据的补码,后一半CLK取数据的原码,从而保证跃变沿总是发生在每bit的中央处。Manchester编码器在数据包结束后加入一个起始空脉冲(SOI: Start of Idle Pulse)。在编码过程中包与包之间的间隔则不进行编码,由链路脉冲填充。Manchester编码过程的时间关系如图3所示。

图3 Manchester编码过程的时间关系图

从MAC/Repeater接口来的4bit的nib流或串行bit流,利用Manchester编码进行编码。编码的逻辑是:

1、二进制NRZ数据“1”

当码元(bit)周期前半周期时取负值;

当码元(bit)周期后半周期时取正值。

2、二进制NRZ数据“0”

当码元(bit)周期前半周期时取正值;

当码元(bit)周期后半周期时取负值。

使用Manchester编码的优点,一是每个bit周期可有一编码时钟;二是不必考虑数据本身是“0”还是“1”,增加了数据的跃变沿。但它的缺点是编码后的数据率增加了一倍。

PCS子层还可完成碰撞检测,即在数据传输和接收同时发生时,需按标准规范和根据工作模式进行处理。在半双工工作模式下,发生碰撞时产生检测信号(COL: Collision Detection Signal),而在全双工工作模式下,不产生COL。

4.3 PCS接收子层

4.3.1 PCS接收子层的功能

PCS接收子层主要完成以下功能:

串/并变换;载波检测;4B/5B或Manchester译码;码组成帧。

即PCS接收子层状态机连续接收从PMA来的数据,将其由串行变换为并行,以及成帧和译码,之后送到MAC/Repeater接口。接收状态机则在接收和数据状态判断之间进行转换并连续这个过程,直到发生下述情况之一时为止:

数据流结束标帜符(ESD,即/T/R/符号);

有差错发生;

过早结束(空号)。

依据ESD,接收状态机返回到Idle状态时,ESD并没有被送入MAC/Repeater接口,因此检测出的差错将迫使接收状态机宣告接收错,并等待后面符号。若接收状态机检出“过早结束信号(Premature end)”,同样也要宣告接收错,而返回Idle状态。

4.3.2 100Mbit/s的PCS接收子层4B/5B译码

由于从双绞线对输入的数据在发端进行了4B/5B编码,因此在接收端必须利用4B/5B译码器进行译码,即将5B码组映射成4B码。4B/5B译码器的输入来自解扰器(Descrambler)。按表3所示,将5bit码组变换为4bit的nib。4B/5B译码器应首先将SSD帧符(/J/K/符号)拆除并用两个4B数据“5”nb(/5/符号)来代替,对ESD帧符(/T/R/符号)也需要被拆除并用两个4B数据“0”nib(/I/符号)代替。

表3 4B/5B符号译码表

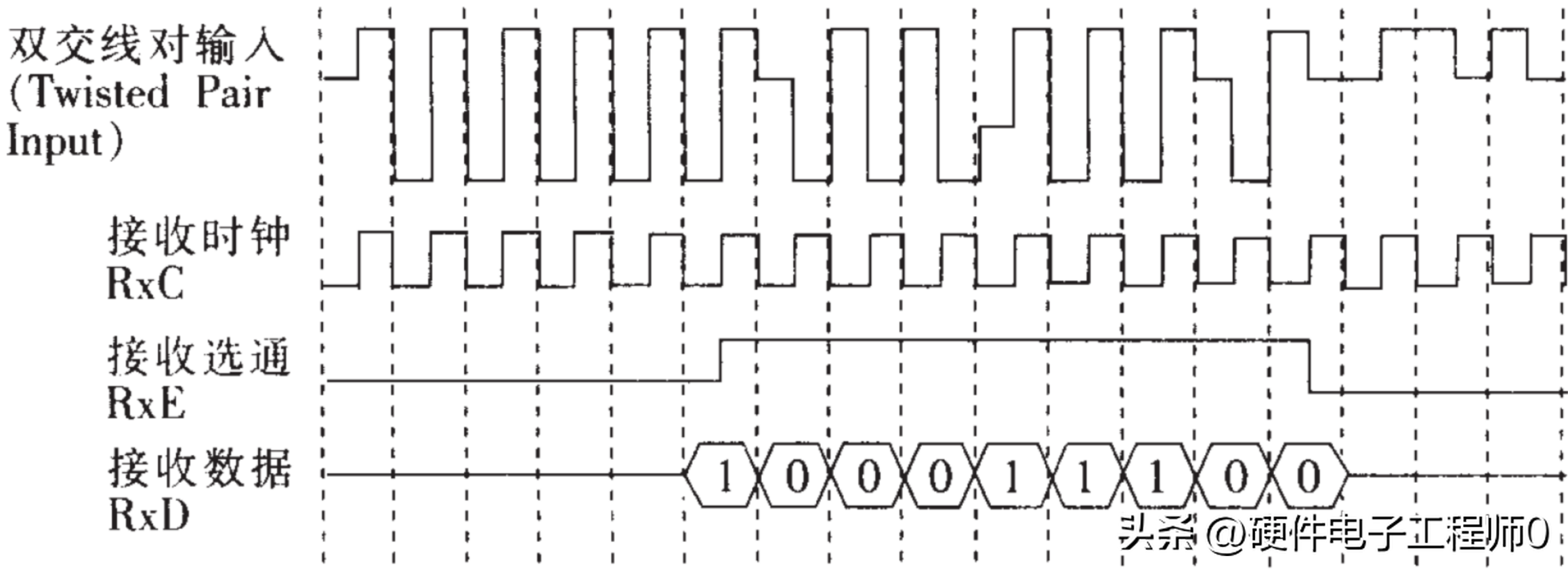

10Mbit/s PCS接收子层Manchester译码

Manchester译码器将从双绞线对接收到的Manchester编码信号变换为原NRZ信号,并将空载开始脉冲(SOI: Start of Idle)拆除。在发送端,NRZ数据被Manchester编码,即数据和时钟相异或。在接收端,数据再次和时钟相异或,就可以恢复出原始数据。图4、图5即为ML2653型10Base-T物理接口芯片发收Manchester信号编译码的定时图。

图4 发送系统定时图

图5 接收系统定时图

PCS子层提供CRS载波检测信号(Carrier Sense Signal)和碰撞检出信号(Collision Detection Signal),用这两个控制信号实现对MII接口的控制与管理。

物理介质连接子层(PMA)

PMA与PCS及PMD子层相连,因此必须有两个接口:一个是到上边PCS子层的接口,另一个是到下边PMD子层的接口。PMA子层主要功能是:

(1) 链路监测(Link Monitoring);

(2) 载波检测(Carrier Detecting);

(3) NRZI编/译码(NRZI En-coding/Decoding);

(4) 发送时钟合成(Transmit Clock Synthesis);

(5) 接收时钟恢复(Receive Clock Recovery);

5.1 PMA发送子层

PMA发送子层(PMA Transmit Sublayer)从PCS子层接收串行比特流并且将其变换为NRZI格式(10Mbit/s不用),然后将其送入物理介质相关子层(PMD)。

PMA使用数字锁相环(PLL)合成技术,从时钟标准接口得到需要发送的时钟脉冲,并根据标准时钟接口的安排,得到不同的发送时钟值。

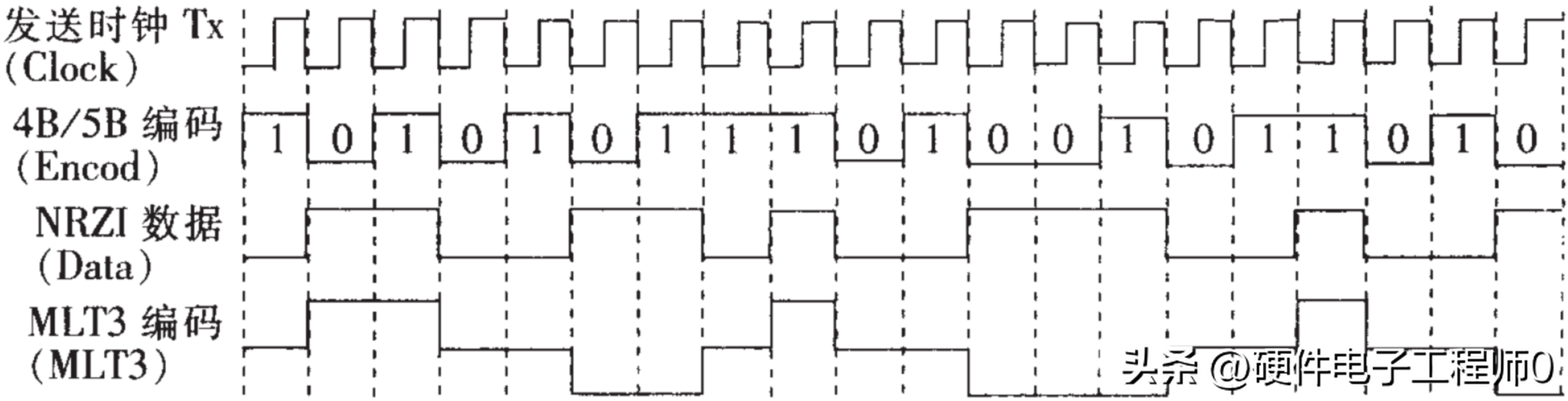

在PMA发送子层需进行NRZI(Non Return to Zero Inverter)编码,这是一种两电平的单极性(O和V)编码。用两电平之间的跃变表示数据“1”,无跃变表示“0”。在这里NRZI编码为将数据变换成MLT-3编码作了准备。具体实例如图6所示。

图6 NRZI和MLT-3编码波形实例

5.2 PMA接收子层

PMA接收子层主要完成下面两个功能:

(1) NRZI译码(NRZI Decoding/10Mbit/s不用): 即将从PMD子层接收的串行bit流进行NRZI译码,并将其变换成单极性的二进进PCS子层。

(2)接收时钟恢复(Receive Clock Recovery): 即接收时钟恢复是由PLL完成的,此PLL锁定于从PMD子层接收据串行数据流上。PLL自动同步于串行数据流并从中提取时钟,最后将恢复时钟和NRZI译码后的数据流送到PCS子层。

当PMA接收子层没有检出任何接收信号时,PMA利用发送时钟作为PLL的参考标准时钟。在100Base-TX信号情况下,恢复出25MHz的时钟。而在10Base-T信号时时钟信号则是2.5MHz。

PMA接收子层的链路监视功能(Link Monitoring Function)可以来监视接收时钟PLL。若接收时钟PLL没有捕获锁定的串行数据流,则产生一个差错信号。在一般情况下,PMA链路监视功能块是连续统计与其连接的链路状态。若没有检出接收信号或者PLL误帧,则宣告接收通道差错。

物理介质相关子层(PMD)

这里主要介绍100Base-TX速率下的双绞线对物理介质相关天的子层(TP-PMD:Twisted-Pair Physical Media Dependent)。按照ISO/IEC IEEE的标准,100Base-TX TP-PMD具有对数据流扰码、解忧码、三电平、多跃变沿MLT-3编译码功能及对接收信号进行直流恢复和自血压计匀衡。

6.1 数据流的扰码器/解扰器

在通常情况下,数字传输系统的鲁棒性(Robustness)依赖于数字信号源的统计特性。例如,接收时钟是从接收数据提取得来的,长串“0”和“1”可能引起同步的丢失。为了使定时恢复电路处于同步状态,数据信号必须包含足够的跃变沿。

IEEE 802.3u协议允许出现一些重复的数据图形,这些重复的数据图形在线路信号的功率频谱密度分布中出现能量峰值,其不连续的频谱分量是有害的,必须将其抑制掉。利用扰码(Scrambling)技术扩展这些图形从而抑制掉这些不连续峰值分量达20dB~25dB。这是因为在一定周期时间内信号数据的随机性使得数据信号有均匀功率输出。这样,峰值能量被消除,从而改善了发送性能。

在发端TP-PMD子层对4B/5B编码信号进行扰码。扰码器(Scrambler)将普通的NRZ bit流利用键控、模2加的方法产生一个被扰码的数据流。其工作过程是:一个11bit的线性反馈移位寄存器(LFSR: Linear Feedback Shift Register)的输入是第11bit和第9bit的模2加(Exclusive-OR),移位寄存器中至少包含有一个非零bit,其产生的伪随机序列可以与需要扰码的信号相加,最后得到已扰码的信号(10Mbit/s不用扰码)。

解扰器(Descrambler)的作用是将被扰码的数据进行解扰,恢复成原NRZI数据信号。在数据解扰前,应首先实现解扰器同步,一旦建立了解扰器同步,在给定的期间内,只要检出足够扰码空载图形“1”的个数,即在1ms时间内至少应检出25个连续解扰空信号“1”,就能保持同步状态。若在1ms时间内没有检出25个连续解扰空信号“1”,则解扰将失步,而需要重新建立同步过程。

6.2 100Base-TX MLT-3编码器/译码器

MLT-3线路编码(MLT-3 Line Code)用于使用电缆介质的快速以太网。MLT-3是一种三电平双极性编码(+V、0和-V),用两电平之间的跃变沿来表示“1”,而无跃变沿表示“0”。这里,MLT-3的最高基频是NRZI的一半。使用MLT-3编码可使高频频谱能量移向低于30MHz的边缘区。与NRZI比较,MLT-3编码90%以上的频谱能量在40MHz以下,而NRZI则在70MHz以下。这样,在相同数据率下,不要求有更高带宽的传输介质。

MLT-3编码器将从扰码器来的NRZI扰码信号(NRZ)变换为三电平MLT-3编码信号;MLT-3译码器则作反变换恢复原NRZI扰码信号。在这里从中提取了时钟,并利用此时钟进行译码。

6.3 直流恢复(DC Restoration)

在100Base-TX数据流的扰码和MLT-3的编码中,可能存在一定长度的连“1”或连“0”序列,使得数据流中产生直流分量,变压器的隔直也会引起信号“基线”的漂移,即“基线”信号从其正常额定直流值移动或漂移,而不利于接收机对于噪声的抑制特性,因此需要恢复信号原直流分量。

6.4 自适应均衡器(Adaptive Equalizer)

当数据在电缆中传输时,由于色散特性,将会导致信号失真和码间干扰(ISI: Inter Symbol Interference),因此在接收机中必需采取措施将进来的失真和码间干扰信号恢复成原信号。失真的产生依赖于信号的频谱和介质环路的长度。由于在多数情况下,双绞线对(TP)端口的特性是未知的,并且每个端口要求均衡的特性也不相同,因此,在TP-PMD标准中,提出了使用自适应均衡器恢复原信号的要求,以保证对接收信号进行适当的补偿。自动均衡的方法之一是监视接收信号的能量,用以确定传输介质的长度,并据此调整均衡器的性能。因为,接收信号的幅度与传输的缆长是成正比的,所以若信号电平降低,则会增加均衡的总量,而便于补偿信号在线路中的损失。

6.5 双绞线对发射机

一般的双绞线对发射机(Twittered-Pair Transmitter)编码器、波形发生器以及传输介质线路驱动器所组成。波形发生器接受MLT-3编码波形,并使用一个电流源交换阵列来控制输出信号上升/下降沿的时间和信号的幅度电平。为了平滑此电流型信号输出和除去高频分量,需通过一个低通滤波器,使发送的输出波形满足有关脉冲样板的标准。电流驱动型差动驱动器将平滑后符合要求的波形变换为可以驱动10m、100欧姆的5类非屏蔽双绞线电缆或100m、150欧姆屏蔽双绞线电缆的电流输出。最后与传输介质的接口是一个隔离变压器。

6.6 双绞线对接射机

一般双绞线对接收机被制作成通用模块,通过一个隔离变压器与传输介质连接。从双绞线对(TP)输入的信号首先进入自适应均衡器,在这里对于缆的低通特性进行补偿,接着进入“基线漂移校正电路”恢复由变压器隔去的波形直流分量。比较器将均衡后的信号变换回原数字电平供“镇噪电路(Squelch Circuit)”使用。MLT-3译码器接收从比较器来的三电平MLT-3信号并且将其变换为常规数字数据,用来恢复时钟和数据。其全过程如图7 所示。

6.7 自动极性校正与隔离变压器

一般的100Base-TX没有极性问题,但是自动协商(FLP)对于极性是比较灵敏的。自动极性校正(Auto Polarity Correction)功能主要是应用于10Base-T工作方式,通常利用规范链路脉冲(NLP: Normal Link Pulses)检验信号极性,从而校正反向的信号极性。

ISO/IEC8802-3、IEEE802.3标准要求要通过隔离变压器(Isolation Transformer)与电缆传输介质连接。而典型的磁性器件模块包含两个隔离变压器,一个用于双绞线对发射机,另一个用于接收机。通过这两个隔离变压器与传输介质物理隔离和交流耦合。

7 自动协商子层(AUTONEG)

7.1 自动协商子层功能

自动协商子层(AN: Auto-Negotiation Sublayer)通常有以下功能:

1、确定在链路段介质或电缆连接的另一端设备所具有的能力;

2、宣布远端链路设备中上述能力;

3、与链路远端设备交换彼此表征技术能力的数据参数,并且与远端链路设备建立协议,自动选择共有的最高性能工作模式。包括工作速率(10/100/1000Mbit/s)、传输介质和半/全双工模式。

自动协商功能是在建立链路两端设备中选择共有的最高性能工作的模式,其算法和链路完整性算法的区别在于:标准链路完整性算法仅用于建立来往远端设备的活动链路,而自动协商算法则是在选择两端共有的最高性能后,还要建立来往远端设备的激活链路。

7.2 自动协商子层的启动

在以下事件之一发生时,需启动自动协商功能算法:

1、设备选通自动协商功能;

2、设备进入链路故障(Fail)状态;

3、自动协商复位。

在ISO/IEC 8802-3标准的附录28B中,列出了各种技术的优先权顺序,如下所示:

100Base-TX全双工(最高优先权);

100Base-T4;

100Base-TX半双工;

10Baed-T全双工;

10Base-T半双工(最低优先权)。

一般地说,自动协商执行的过程要小于500ms,这与对端完成自动协商链路的能力无关。自动协商过程的监视器可以监视自动协商过程和链路是否建立。

总结

PHY物理层器件应满足CSMA/CD以太网ISO/IEC 8802-3的标准要求。前面分别详细描述了MII接口、物理编码子层(PCS)、物理介质连接子层(PMA)、物理介质相关子层(PMD)以及自动协商(Auto-Negotiation)功能和原理。现将各部分功能概括于表1之中,以进行比较。

表4 以太网物理层PHY芯片功能表

| MII | PCS | PMA | TP-PMD | AUTONEG | MDI |

| 接MAC/PHY端口;接STA/PHY管理端口 |

4B/5B编译码 (100Mbit/s); 碰撞检测; 串并转换; Manchester编译码(10Mbit/s); MAC/Repeater接口控制 |

链路监测; 载波监测; NRZI/NRZ编译码(100Mbit/s); 时钟合成/恢复 |

扰码/解扰(100Mbit/s); NRZI/MLT-3编译码(100Mbit/s); 直流恢复; 自动极性校正; 发送/接收变压器隔离 |

NLP链路完整性(主要用于10Mbit/s); FLP自动协商 |

与传输介质相 |

审核编辑:刘清

-

以太网PHY怎么改变现代市场2018-09-07 0

-

STM32F407能不能同时使用USB PHY和以太网PHY2018-11-21 0

-

以太网控制器外部PHY芯片模拟程序代码实现2019-01-18 0

-

以太网MAC芯片与PHY芯片的关系是什么2020-12-28 0

-

以太网芯片MAC和PHY的关系 精选资料分享2021-07-29 0

-

以太网简介2021-08-09 0

-

以太网芯片MAC和PHY有何关系2021-09-22 0

-

请问如何更换以太网PHY芯片?2022-01-11 0

-

如何对以太网PHY芯片的rmii pin脚进行配置2022-02-21 0

-

RK3288搭配以太网PHY芯片怎么使用?2022-03-03 0

-

RK3288搭配以太网PHY芯片需要注意哪些2022-08-31 0

-

以太网PHY如何改变现代市场2022-11-18 0

-

使用不同的以太网PHY,MDC信号的问题求解2023-03-23 0

-

一文详解车载以太网PHY芯片2023-06-19 5109

-

还在为以太网PHY缺芯改版烦恼吗?2022-09-06 1052

全部0条评论

快来发表一下你的评论吧 !