如何优化DC/DC变换器中FB分压电阻的FB布线

电子说

描述

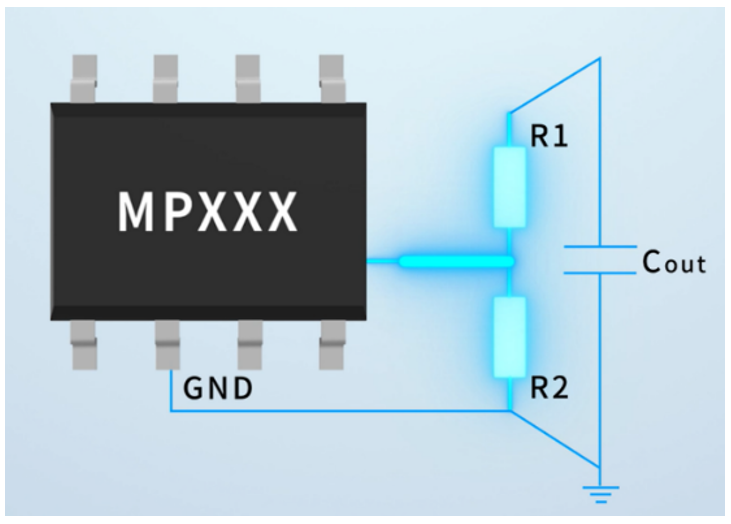

在 DC/DC 变换器中,反馈 (FB) 分压电阻的规格常给设计人员带来各种设计挑战,例如如何确定所需的电阻或调节参数(如输出电压、上分压电阻或下分压电阻)。 图 1 显示了 FB 上/下分压电阻的各种幅度组合。

图 1:FB 上/下分压电阻的各种幅度组合

本文将探讨 FB 分压电阻的设计规范,包括待机功耗、输出电压精度和环路特性。

待机功耗

图 2 显示了具有低静态电流 (IQ) 的 DC/DC 变换器,其 FB 分压电阻在不同数量级下带来的效率差异。以 MP4430 MPQ4430 为例,R1 和 R2 是其分压电阻。

图 2:R1 和 R2 数量级不同带来的效率差异

优化待机功耗,尤其是对电池供电产品,可以按比例增大 DC/DC 变换器的 FB 分压电阻值。

低 EMI DC/DC 变换器的 PCB 设计

本文以 MPS 的 MPQ4431 降压变换器为例,阐述审慎的元件布置与电路板布局如何帮助产品满足汽车行业严格的 EMC 限制

线上研讨会

EMC 优化的降压变换器 PCB 布局

探讨 DC/DC 降压变换器 PCB 设计,包括布局划分、元器件摆放和 EMC 优化布线等。

文章

DC/DC 变换器采用恒定导通时间控制的优势

作为一种比传统电流模式控制方案更加有效的 DC/DC 变换器控制模式,本文讨论了恒定导通时间控制 (COT) 的优势所在。

参考设计

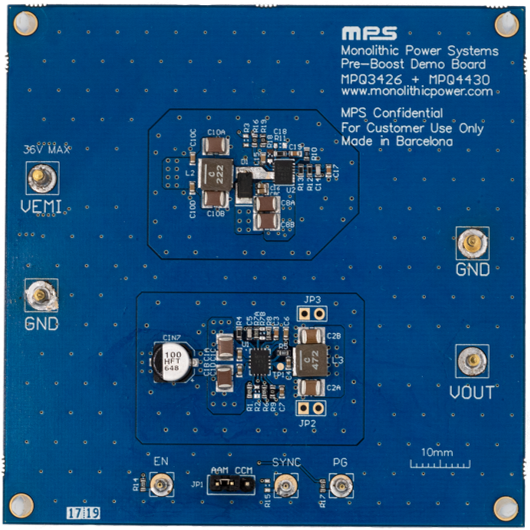

MPQ3426 - 预升压参考设计,解决汽车冷启动瞬变的简单解决方案

该参考设计将帮助工程师实现高达 18W 的电源预升压设计

输出电压精度

增大 FB 分压电阻的阻值,可以降低待机功耗。

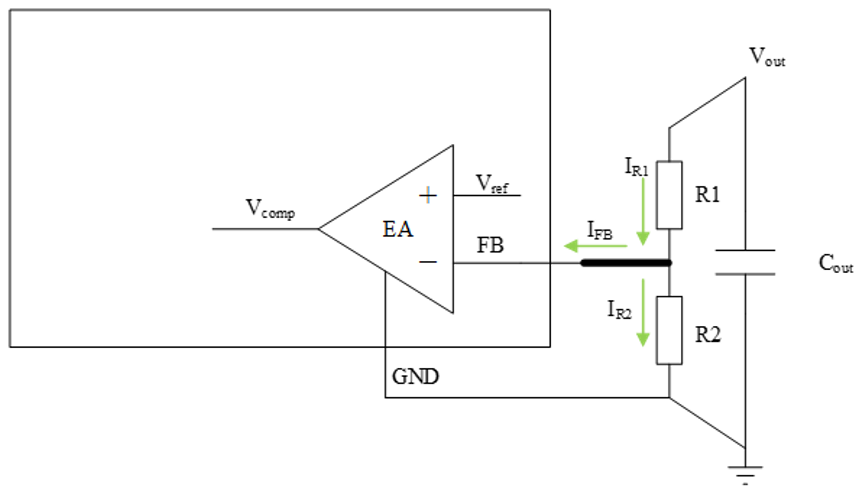

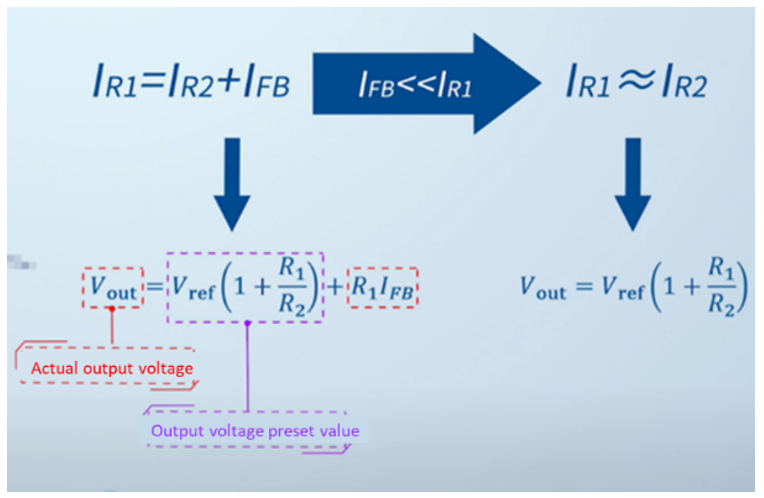

FB 是运算放大器(op amp)的负输入端,它会汲取一定的电流。当 FB 电流(IFB)在分压网络中占比较小时,IFB 可忽略不计;当其占比较大,即分压电阻选值较大时,IFB 就不容忽视(见图 3)。

图 3:FB 电流在分压网络中的占比

如图 4 所示,当实际输出电压 (VOUT) 由于 IFB 的存在而超过预设值时,会降低电压精度。

图 4:计算输出电压精度

因此,建议选择合适的阻值,使流经分压电阻的电流超过 IFB 的 50 倍。

环路特性

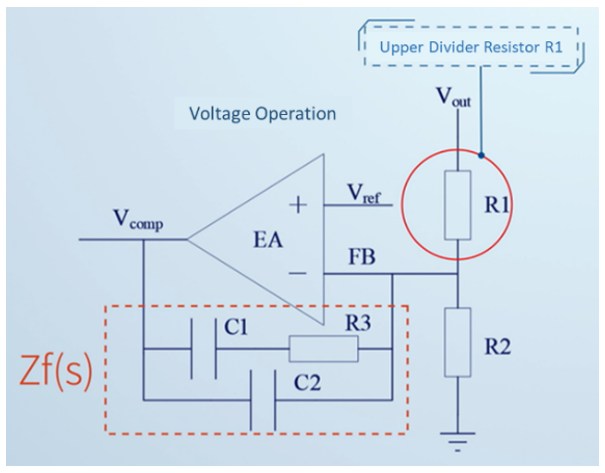

FB 电阻还会影响芯片内部的环路特性。当反馈网络只是单电阻的情况时,电压型运放,误差放大器增益与上分压电阻 R1 有关,在动态负载对纹波有要求的场景,我们可以调整 R1 阻值做进一步优化。

图5: 电压模式运放

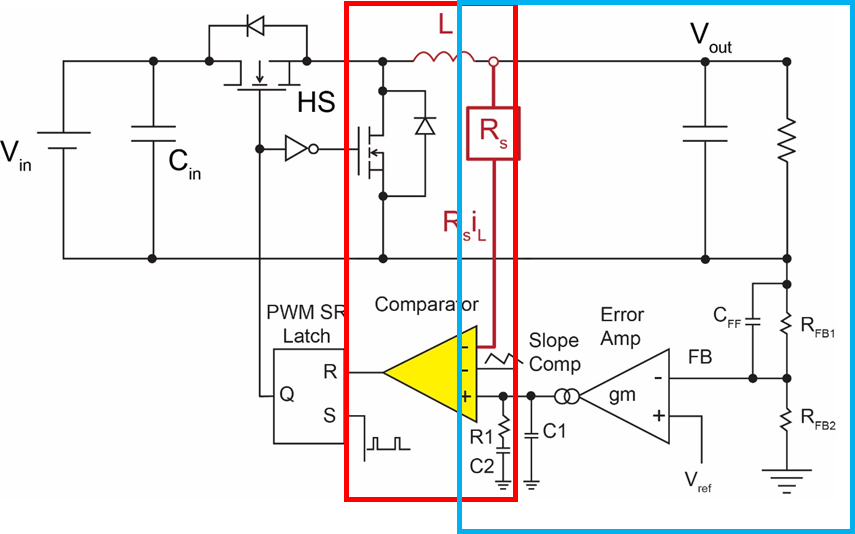

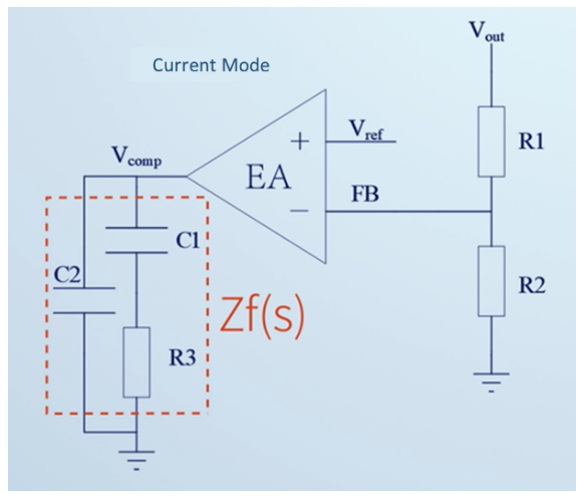

在电流模式运放中,运放增益 (GEA(S)) 与 R1 / R2 值没有直接关系,但与两个电阻的比值有关。图 6 所示为电流模式运放。

图 6:电流模式运放

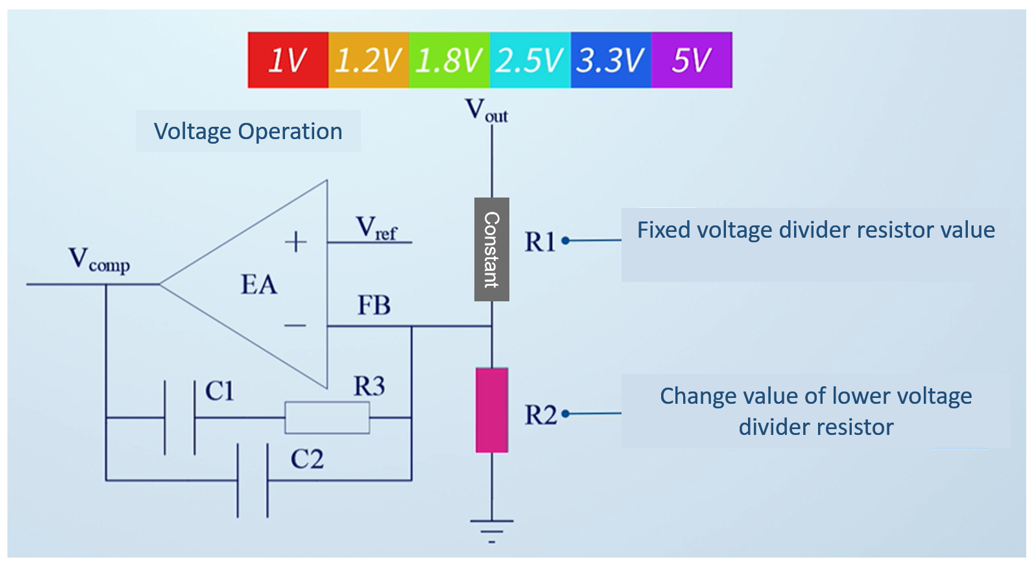

对于不同的 VOUT 场景(1V、1.2V、1.8V、2.5V、3.3V 或 5V),建议保持上分压电阻的阻值不变,只调节下分压电阻的阻值,以获得近似的环路特性(见图 7)。

图 7:根据输出电压的不同调整下分压电阻的阻值

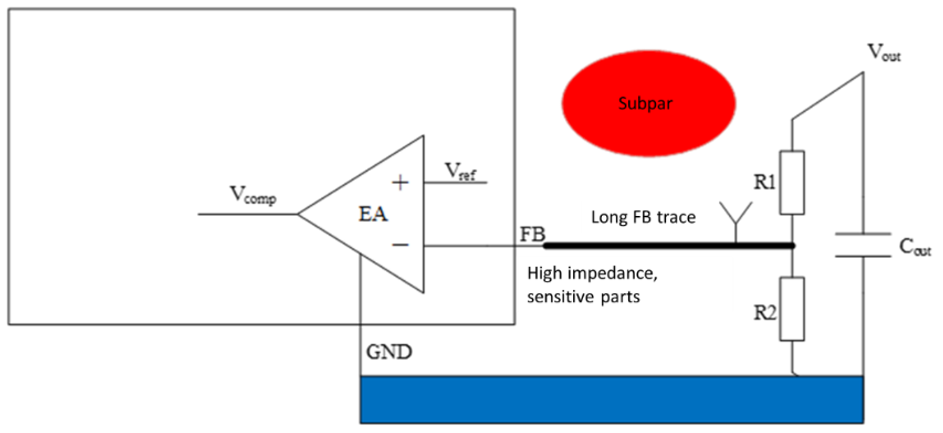

确定 FB 分压电阻值后,还需要注意 FB 引脚的接线。FB 是容易耦合噪声的高阻抗引脚。在实际应用中,常见到 R1、R2 放在输出电容端,这导致 FB 走线较长。这段 FB 走线充当了天线,更易耦合非实反馈,继而导致 VOUT 变化或不稳(见图 8)。

图 8:长 FB 走线更易耦合非实反馈

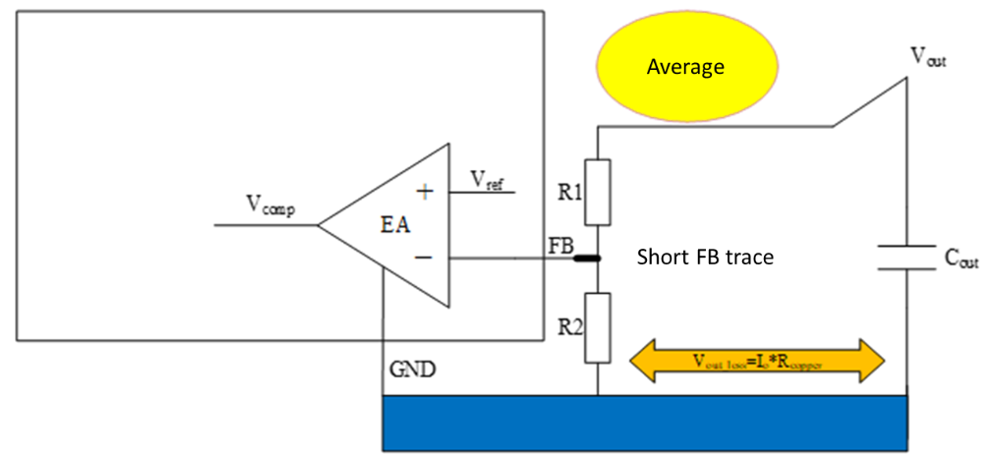

在电路布线设计中,FB 走线应尽量短,R1、R2 应尽量靠近 IC 的 FB 引脚放置;但 VOUT 输出直流电平,抗干扰能力强,所以可采用长走线(图 9)。

图 9:电路走线中的短 FB 走线

一般在输出电流(IOUT)只有几个安培时,R2 的接地可以靠近芯片地。但当 IOUT 超过 10A 时,由于接地线上的敷铜有限,地线上的电压会损失,导致实际 VOUT 低于预设电压。在这种情况下,建议使用远程采样(见图 10)。

图10:远程采样/p>

结语

要优化 DC/DC 变换器 中 FB 分压电阻的 FB 布线,首先要保持第一个电阻走线尽可能地短,并在同一侧直接连接第二个电阻。同时确保没有干扰源,如开关、电感、噪声地等。

审核编辑:彭菁

-

#硬声创作季 闭环降压变换器是如何工作的DC-DC变换器--动画演示Mr_haohao 2022-10-19

-

隔离式DC/DC变换器的电磁兼容设计2009-10-12 0

-

双管正激DC_DC变换器的损耗计算与优化设计2012-08-14 0

-

选择最佳DC/DC变换器的要点及途径2014-06-05 0

-

DC-DC变换器2016-12-28 0

-

最佳的开关式DC/DC变换器2021-11-16 0

-

DC-DC变换器的基本电路2021-11-17 0

-

DC-DC变换器的应用2021-11-17 0

-

降低dc-dc变换器输出电压纹波的电路2022-04-02 0

-

小功率DC/DC变换器设计2022-04-04 0

-

MPS | DC-DC变换器FB分压电阻设计2022-10-16 0

-

电池驱动系统的DC-DC变换器选择2023-03-03 0

-

DC/DC变换器中的反馈(FB)分压电阻设计2023-08-10 2091

-

金升阳首次推出600W、1200W DC/DC宽压电源—VRF3D_FB-xxWR3系列2024-01-12 672

全部0条评论

快来发表一下你的评论吧 !